# Effects of Gate-to-Body Tunneling Current on PD/SOI CMOS Circuits

C. T. Chuang, R. Puri, and \*K. Bernstein

# IBM T. J. Watson Research Center, Yorktown Heights, NY 10598 U. S. A.

### Phone: +1-914-945-3596, Fax: +1-914-945-1358, e-mail: ctchuang@us.ibm.com

\*IBM Microelectronics Division, Essex Junction, VT 05452, U. S. A.

#### I. INTRODUCTION

Recently, the gate-to-body tunneling current in PD/SOI device resulting from the electron tunneling from the valence band (EVB) [1] has been shown to charge/discharge the floating-body, thus changing the body voltage and  $V_T$  and affecting circuit operations [2, 3]. In this paper, we present a detailed study on the effect of gate-to-body tunneling current on PD/SOI CMOS circuits in a 1.5 V, 0.18  $\mu m$  PD/SOI technology with  $L_{eff} = 0.075$  $\mu m$ ,  $t_{OX} = 2.3$  nm,  $t_{Si} = 150$  nm, and  $t_{BOX} = 145$  nm. Basic physical mechanisms underlying the variations in body voltage and delay and their temperature dependence in the presence of the gate-to-body tunneling current are examined. The resuling impacts on the gate delays and Power4 PowerPC microprocessor [4] critical paths are presented.

## II. TEMPERATURE DEPENDENCE & INITIAL QUIESCENT STATE

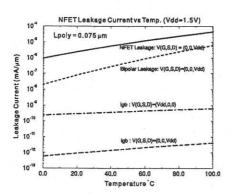

Fig. 1 shows the temperature dependence of the "intrinsic" nMOS leakage, parasitic bipolar leakage, and gate-to-body tunneling current  $(I_{gb})$  for a PD/SOI nMOS with  $L_{eff} = 0.075 \ \mu m$ . Two cases for the  $I_{gb}$  are shown, corresponding to two different biasing conditions for the nMOS; namely V (G, S, D) = (0, 0, 0, 0)  $V_{DD}$ , and V (G, S, D) = ( $V_{DD}$ , 0, 0). As can be seen, the gate-to-body tunneling current exhibits a much weaker temperature dependence compared with the "intrinsic" nMOS leakage and parasitic bipolar leakage, hence its effects are expected to be more significant at lower temperature.

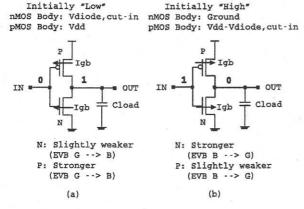

Consider a static CMOS inverter in the quiescent state with input initially at "Low" (Fig. 2(a)). For the nMOS, with V (G,  $S, D) = (0, 0, V_{DD})$ , its body sits at a diode cut-in voltage determined primarily by the balance of the back to back drain-to-body and body-to-source junctions. Thus, there is a "small" negativebias across the gate and body, resulting in "small" EVB from the gate to the body. This "small" body-to-gate tunneling current discharges the body, thus increasing  $V_T$  slightly and making the nMOS "slightly weaker". The body voltage of the nMOS is determined by the balance of the reverse-biased drain-to-body junction leakage current (which flows into the body), the bodyto-gate tunneling current (which flows out of the body), and the forward-biased body-to-source junction current (which flows out of the body). For the pMOS, with V (G, S, D) =  $(0, V_{DD}, V_{DD})$ , its body sits at  $V_{DD}$ . Hence, there is a "large" negative bias across the gate and boy, resulting in EVB from the gate to the body. This body-to-gate tunneling current discharges the body, thus decreasing  $V_T$  and making the pMOS "stronger". The body voltage of the pMOS is determined by the balance of the forward-biased drain-to-body and source-to-body currents (both flow into the body) and the body-to-gate tunneling current (which flows out of the body). When the inverter starts switching, because of the "slightly weaker" nMOS and "stronger" pMOS, the input-rise delay slows down while the input-fall delay speeds up (compared with the case when there is no gate-to-body tunneling current). The complementary situations hold for the case with the input initially at "High" (Fig. 2(b)). For this case, due to the "stronger" nMOS and "slightly weaker" pMOS, the input-rise delay speeds up while the input-fall delay slows down.

### III. STATIC CMOS INVERTER

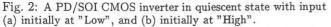

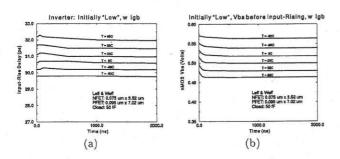

Fig. 3(a) shows the input-rise delays as functions of time with temperature as a parameter for a PD/SOI CMOS inverter "with-out" the gate-to-body tunneling current. The inverter input is initially at "Low" and then switches continuously at 1.0 GHz with 50% duty cycle and 100 ps input slew. The load, 50 fF, is equivalent to a fan-out of 3 for the device sizes used. The body voltages for the nMOS are shown in Fig. 3(b). The corresponding cases, with the gate-to-body tunneling current, are shown in Fig. 4(a) and 4(b), respectively. As the initial nMOS body voltage is determined primarily by the balance of the back to back drain-to-body and body-to-source diodes, both the initial nMOS body voltage (Fig. 3(a)) and the initial input-rise delay (Fig. 3(b)) exhibit strong temperature dependence [5]. Furthermore, as can be seen in Fig. 4(b), the body is only slightly discharged by the body-to-gate tunneling current.

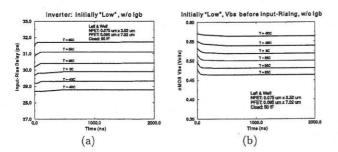

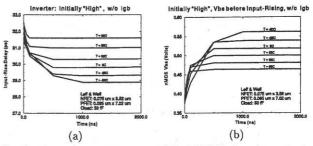

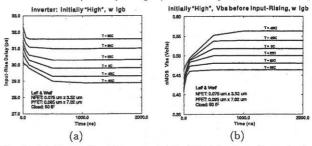

Fig. 5(a) and 5(b) show the complementary situation, where the inverter input is initially at "High", "without" the gate-tobody tunneling current. The corresponding cases, with the gateto-body tunneling current, are shown in Fig. 6(a) and 6(b), respectively. With the input initially at "High", the body voltage of the nMOS before the first input-rising transition is determined primarily by capacitive coupling and exhibits weak temperature dependence (evident by the "clustering" of the initial body voltages in Fig. 5(b), and the weak temperature dependence of the initial input-rise delay in Fig. 5(a)) [5]. Furthermore, as there is full  $V_{DD}$  across the gate and the body, the charging of the body by the gate-to-body tunneling current is quite significant (Fig. 6(b)). The effect can also been seen to be more significant at lower temperature, causing "spread" of the initial body voltages (hence initial input-rise delay as well).

### IV. IMPACT ON CIRCUIT DELAYS

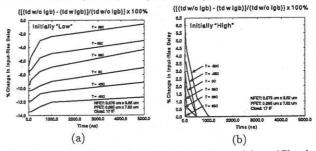

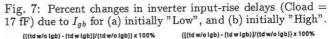

Fig. 7(a) and 7(b) show the percent changes in the inverter input-rise delay due to the gate-to-body tunneling current for the two initial conditions with Cload = 17 fF (equivalent to fan-out of 1). The percentage change in the delay is defined as [(Delay without  $I_{gb}$ ) - (Delay with  $I_{gb}$ )]/(Delay without  $I_{gb}$ ) x 100%. As expected, with the input initially at "Low", the input-rise delay slows down with  $I_{gb}$  and the effect is more pronounced at lower temperature (Fig. 7(a)). At 25 °C, the slow-down is 9.5% initially and 4.4% at t = 5000 ns. For the case of initially "High" input, the input-rise delay speeds up. At 25 °C, the speed-up is 1.75% initially and 0.0% at t = 5000 ns.

Fig. 8(a) and 8(b) show the corresponding cases for the inputfall delay (dictated by the pMOS). The effect of  $I_{gb}$  can be seen to be more significant. For example, with input initially at "low" at 25 °C, the input-fall delay speed-up is 15% initially and 8.0% at t = 5000 ns

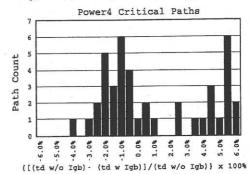

Fig. 9 shows the path counts vs the percent changes of the path delays due to  $I_{gb}$  at 85 °C for critical paths in the 1.0 GHz 170 million transistors Power4 PowerPC microprocessor [4]. The presence of  $I_{gb}$  can be seen to affect the path delays ranging from 4.0% slow-down to 6.0% speed-up.

#### V. CONCLUSION

In summary, the presence of gate-to-body tunneling current changes the strength of individual transistor in the quiescent state, thus affecting circuit delays when the circuit subsequently switches. The effect is more pronounced at lowered temperature. The impact on the gate delays and microprocessor critical path delays are significant with  $t_{OX} = 2.3$  nm in a 1.5 V, 0.18  $\mu m$ ,  $L_{eff} = 0.075 \ \mu m$  PD/SOI technology. With thinner gate oxide in scaled devices, a full understanding of the the effect is crucial to ensure proper circuit functionality and performance.

### References

- W. C. Lee and C. Hu, "Modeling Gate and Substrate Currents due to Conduction- and Valence-Band Electron and Hole Tunneling," Dig. Tech. Papers, Symp. VLSI Technology, 2000, pp. 198-199. S. K. H. Fung et. al., "Impact of the Gate-to-Body Tunneling Current on SOI History Effect," Proc. IEEE Int'l SOI Conf., 2000, pp. 122-[2] 123.

- 123.

[3] S. K. H. Fung et. al., "Controlling Floating-Body Effects for 0.13 μm and 0.10 μm SOI CMOS," IEDM Tech. Dig., 2000, pp. 231-234.

[4] C. J. Anderson et al., "Physical Design of a Fourth-Generation POWER GHz Microprocessor," Dig. Tech. Papers, ISSCC, 2001, pp. 2002. 232-233.

- R. Puri et. al., "On the Temperature Dependence of Hysteresis Effect in Floating-Body Partially-Depleted SOI CMOS Circuits," Extended Abstracts, Int'l Conf. on Solid State Devices and Materials, 2000, pp. 470-471.

Fig. 1: Temperature dependence of "intrinsic" nMOS leakage, parasitic bipolar leakage, and gate-to-body tunneling current  $(I_{gb})$  in a PD/SOI nMOS.

Fig. 3: (a) Input-rise delays, and (b) nMOS body voltages before the "input-rising" transitions as functions of time for a PD/SOI CMOS inverter (initially "Low") without  $I_{gb}$  (Cload = 50 fF).

Fig. 4: (a) Input-rise delays, and (b) nMOS body voltages before the "input-rising" transitions as functions of time for a PD/SOI CMOS inverter (initially "Low") with  $I_{gb}$  (Cload = 50 fF).

Fig. 5: (a) Input-rise delays, and (b) nMOS body voltages before the "input-rising" transitions as functions of time for a PD/SOI CMOS inverter (initially "High") without  $I_{gb}$  (Cload = 50 fF).

Fig. 6: (a) Input-rise delays, and (b) nMOS body voltages before the "input-rising" transitions as functions of time for a PD/SOI CMOS inverter (initially "High") with  $I_{gb}$  (Cload = 50 fF).

Fig. 8: Percent changes in inverter input-fall delays (Cload = 17 fF) due to  $I_{gb}$  for (a) initially "Low", and (b) initially "High".

Fig. 9: Path counts vs percent changes of path delays due to  $I_{gb}$  at 85 °C for critical paths in Power4 microprocessor