## D-5-4

# A Novel GaAs Binary Decision Diagram Device Having Quantum Wire Branch-Switches Controlled by Wrap Gates

# Miki Yumoto, Seiya Kasai and Hideki Hasegawa

Research Center for Integrated Quantum Electronics and Graduate School of Electronics and Information Engineering, Hokkaido University, N13, W8, Kita-ku, Sapporo 060-8628, Japan Tel: +81-11-706-7172, Fax: +81-11-716-6004, E-mail: yumoto@rciqe.hokudai.ac.jp

## 1. Introduction

Needs for high-density integrated logic circuits that perform high-speed and high-volume information processing continue to increase in the internet era. Quantum devices are promising candidates as key devices for the next-generation nanoelectronics due to their ultra-small switching delaypower product near the quantum limit beyond the scalingdown limit of the Si CMOS technology. However, quantum devices are weak and sensitive. Thus, in order to realize quantum large-scale integrated circuits (QLSIs), it is necessary to adopt a novel logic architecture rather than sticking to the conventional Boolean logic gate architecture.

From such a view point, we have recently proposed a hexagonal binary decision diagram (BDD) quantum circuit approach[1,2] where a hexagonal nanowire network is controlled by nano-scale Schottky gates so as to implement quantum BDD logic circuits. Here, the key device is the BDD node device.

The purpose of this paper is to propose and investigate a novel GaAs BDD node device based on wrap gate (WPG) control of quantum wires.

### 2. Device Concept, Structure and Operation

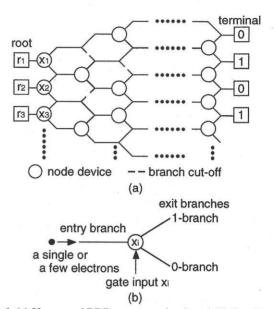

A hexagonal BDD quantum circuit consists of an array of quantum node devices formed on a hexagonal closely packed planar nano-wire network, as schematically shown in **Fig.1(a)**. As shown in **Fig1(b)**, each node device consists of one-entry and two exit-branches, such that one of exit-branches is selected for the information messenger coming into the entry-branch to exit, depending on the gate input  $x_i$ . Here, the information messenger is either a single electron or a few electrons, and path switching is realized by control of quantum transport.

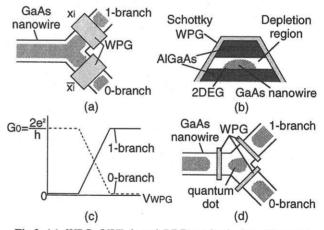

The novel GaAs BDD node device proposed in this paper is shown in **Fig.2(a)**. Here, two branch-switches are realized by quantum wire (QWR) pieces controlled by Schottky wrap gates (WPGs)[3] as shown in **Fig.2(b**). By switching two QWR branch-switches between zeroth and first steps of conductance quantization in a complimentary fashion as shown in **Fig2.(c)** with small enough gate capacitances, path switching near the quantum limit for a few electrons used as the signal messenger.

Fig.1 (a) Hexagonal BDD quantum circuit and (b) function of BDD node device.

**Fig.2** (a) WPG QWR-based BDD node device, (b) crosssection of WPG QWR structure, (c) operation of QWR-based BDD node device, and (d) WPG single electron Y-switching.

As compared our previous device shown in **Fig.2(d)**[1] based on a WPG single electron Y-switching, the present device is more suitable for higher temperature operation and high density integration, because realization of a small and uniform quantum dot in the previous device is rather difficult.

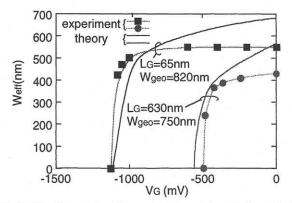

Fig.3 Weff-VG curves from experimental and theoretical calculation of WPG-controlled GaAs nanowires.

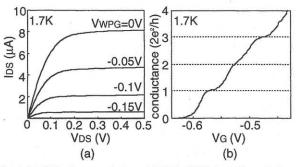

**Fig.4** (a) I-V characteristics of WPG QWR branch-switches and (b) their conductance switching behavior.

#### 3. Experimental Results and Discussion

First, individual WPG branch-switches were fabricated on GaAs QWR pieces produced by EB lithography and chemical etching to investigate the basic gate control characteristics. Figure 3 shows the effective wire width as a function of gate voltage obtained from the magnetoresistance measurements. The WPG controls the effective wire width sensitively near the channel pinch off. The samples with different gate length showed that the threshold voltage depends on not only the nanowire width but also gate length in the nanometer-size WPGs. This corresponds to the short channel effect and such experimental behavior could be well reproduced by the theory based on the three-dimensional potential simulation. The simulation has shown that Fermi level pinning on the semiconductor surface around the WPGs strongly affects the gate controllability[4]. Careful device design could be made using this computer simulation.

The I-V curves of the fabricated WPG QWR branch switches are shown in **Fig.4(a)**, showing good FET characteristics at low temperature which was maintained up to RT. At low temperatures, the conductance quantization could be seen as shown in **Fig.4(b)**. From the vertical magnetic field dependence of conductance step width, the lateral confinement energy was estimated to be 6-7meV.

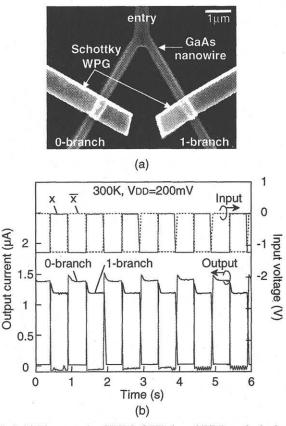

Figure 5(a) shows a SEM micrograph of fabricated QWR-based WPG BDD node device. Each node worked like

Fig.5 (a) Photograph of WPG QWR-based BDD node device, (b) its path switching characterisric.

as conventional FET. Due to the characteristics shown in **Fig.4(b)**, path switching between quantized conductance could be realized at low temperature. Furthermore, the device could realize path switching even at RT as shown in **Fig.5(b)**. This is because the device operation changes gradually from a few electron quantum regime to the many electron classical regime with increase of temperature.

#### 5. Conclusions

We proposed and investigated GaAs QWR-based WPG BDD device. The WPG exhibited excellent gate control of GaAs nanowires from low temperature to room temperature. Then, we successfully fabricated WPG QWR-based GaAs BDD node devices and they realized clear current path switching from low temperature up to room temperature.

#### References

- N.Asahi, M.Akazawa and Y. Amemiya, IEEE Trans. Electron Devices 42 (1995) 1999.

- [2] H.Hasegawa, S. Kasai, M. Yumoto and T. Muranaka, presented at Advanced Research Workshop on Semiconductor Nanostructres, Feb. 5-9, Queenstown, New Zealand (2001).

- [3] S.Kasai, K.Jinushi, H.Tomozawa and H.Hasegawa, Jpn. J. Appl. Phys. 36, 1678 (1997)

- [4] M.Yumoto, M.Iwaya, S.Kasai and H.Hasegawa, accepted for presentation at Int. Conf. Formation Semiconductor Interface, June 10-15, Sapporo, Japan (2001)