## F-2-3

# **Elevated Extension Structure for 35 nm MOSFETs**

Yoshiki Kamata, Mizuki Ono and Akira Nishiyama

Advanced LSI Technology Laboratory, Corporate R&D Center, Toshiba Corporation Phone: +81-45-770-3691, Fax: +81-45-770-3578 e-mail: yoshiki.kamata@toshiba.co.jp

8 Shinsugita-cho, Isogo-ku, Yokohama, 235-8522 JAPAN

### Abstract

A novel extension structure using in-situ doped selective silicon formation is proposed. Using device simulation we show the design guideline of this structure for the minimization of the propagation delay of 35nm CMOS devices. Eventually, this structure proves itself to have a better cut-off characteristic and higher current drive than the already reported comparable MOSFET.

#### 1. Introduction

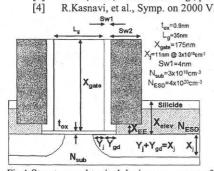

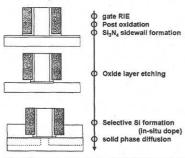

Shallow extension structure is required for the realization of sub-100nm CMOS transistors. There are many candidates for its formation [1-4], however none of them have satisfied the ITRS requirements <sup>[5]</sup> for the junction depth (X<sub>i</sub>) and the sheet resistance for 70nm node CMOS and further generations so far. Therefore, we propose the application of highly doped selective silicon formation and solid state diffusion for the realization of very shallow extensions with low sheet resistance as in Fig. 1. In-situ doped selective Si and SiGe formations have already been reported [6-7]. The newly proposed structure uses the insitu doped silicon layer as the elevated extension and contact source/drain region by one step selective formation as in the process sequence (Fig. 2). In order to accomplish extremely shallow junctions with low sheet resistance, the extensions are elevated. Hence this structure might suffer from a large parasitic capacitance between gate and source/drain (Cpara). We investigated the influence of the structural parameters on the parasitic capacitance and the extension resistance and successfully obtained a set of optimum parameters in terms of the CMOS gate delay.

## 2. Structure in Simulation

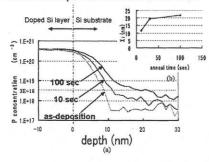

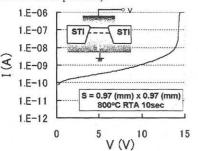

A three-dimensional device simulator (DIAMOND) was used in this study. An elevated extension structure and typical device parameters are depicted in Fig. 1. The gate electrode is made of n+-poly silicon and the substrate doping concentration (N<sub>sub</sub>) is uniformly 3x10<sup>18</sup> cm<sup>-3</sup>. The extension region consists of two parts. The upper part is the in-situ doped silicon region with the impurity concentration of  $4x10^{20}$  cm<sup>-3</sup>. The lower part is the diffusion layer in the silicon substrate. Figure 3 (a) shows phosphorous concentration SIMS profiles for samples, in which the impurity atoms were doped by solid phase diffusion from the doped silicon layer with the impurity concentration of  $4 \times 10^{20}$  cm<sup>-3</sup> deposited by CVD at 600°C. RTA at 800°C for 10 seconds resulted in the junction depth of 11nm at 3x10<sup>18</sup> cm<sup>-3</sup> (Fig. 3 (b)). Furthermore the leakage current level of this shallow junction was well suppressed as in Fig.4. Therefore we used the phosphorous profile of this condition as the diffusion

layer in the silicon substrate. The measured resistivity of doped silicon layer as low as  $1m\Omega cm$  was also implemented in this simulation. We calculated the propagation delay time changing the distance between the gate and the elevated extension (Y<sub>gd</sub>) and the extension thickness (X<sub>EE</sub>). We also optimized the silicon thickness (X<sub>elev</sub>) outside the silicon nitride sidewall and the sidewall thickness (Sw2).

#### 3. Results and Discussion

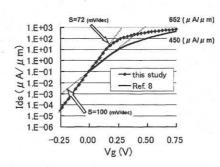

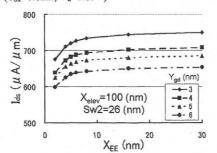

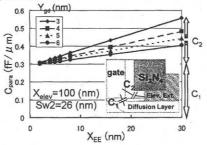

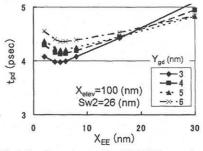

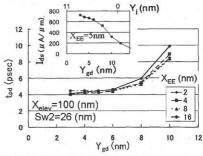

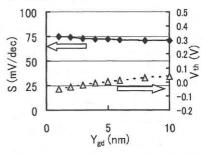

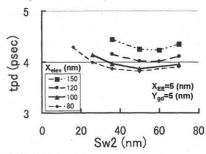

Figure 5 shows a comparison of Ids-Vg characteristics between this elevated extension device with typical structural parameters (see caption and Fig. 1) and the already reported 30nm device in ref. 8. This figure shows a better cut-off characteristic and a higher current drive in the newly proposed structure. Optimizations of the structural parameters are mentioned in detail as follows. Figures 6 and 7 show that  $I_{ds}$  and  $C_{para}$  increase when  $X_{EE}$ increases. Ids increases up to XEE value of 6nm and saturates for farther X<sub>EE</sub> increase. It has been revealed that the increase of the capacitance component C2 between elevated extension and gate (inset Fig. 7) can be well explained by the parallel plate approximation. The optimized X<sub>EE</sub> is around 5nm in terms of the reduction of t<sub>pd</sub> (CMOS inverter) as in Fig. 8. This optimized X<sub>EE</sub> didn't change for various Xelev and Sw2 values. Figure 9 shows Y<sub>gd</sub> dependence of t<sub>pd</sub> with X<sub>EE</sub> as a parameter. It can be seen that  $t_{pd}$  increases drastically with  $Y_{gd}$  over 6nm. This phenomenon can be explained by the steep decrease of Ids, and indicates that the gate/diffusion-region overlap Y<sub>i</sub> of at least 5nm is required for large I<sub>ds</sub> (inset Fig.9). Figure 10 shows that the dependences of S-factor and V<sub>th</sub> on Y<sub>gd</sub> are weak, indicating that the extremely precise Ygd control is not required. Figure 11 shows that there are local minima of tpd with respect to Sw2. This phenomenon can be explained by the increase of parasitic resistance and the decrease of Cpara with Sw2 increase. The Sw2 value which realizes the minimum t<sub>pd</sub> slightly increases with Xelev. tpd increases monotonically with the Xelev increase. We selected 100nm for the minimum Xelev in order to retain a distance between the silicide and pnjunction for the suppression of pn-junction leakage current increases [9-10]. Optimum regions of structural parameters considering 5% increase of tpd are summarized in Table 1(a). Table 1 (b) shows electrical properties of the optimized 35nm device. The gate delay comparable to that of 50nm technology node (Lg=32 nm, high performance) was successfully obtained.

#### 4. Conclusions

It has been shown that the novel extension structure using in-situ doped selective silicon formation can realize excellent performances of MOSFETs of 35nm and farther generations.

## References

- Y.H. Song, et al., IEDM Tech. Dig., p.505 (1999). [1]

- [2] M. Ono, et al., IEEE Trans. Electron Devices, 42, p.1755

- (1995)[3]

- B. Yu, et al., IEDM Tech. Dig., p.509 (1999). R.Kasnavi, et al., Symp. on 2000 VLSI Tech., p.113.

Fig.1 Structure and typical device parameters of MOSFET with elevated extension (shadow area represents in-situ doped silicon layer)

Fig.2 Process sequence of MOSFET fabrication with in-situ doped selective silicon formation

Fig.3 (a) Phosphorous concentration SIMS profile for as-deposited and after diffusion by 800°C RTA

(b) Junction depth at  $3 \times 10^{18}$  cm<sup>-3</sup> as a function of annealing time

(Depth is measured from the original surface before silicon deposition.)

Fig.4 Current-voltage characteristic of n+/p junction formed by solid phase diffusion from doped silicon region (800°C RTA 10sec)

Fig.5 Ids-Vg characteristics of 35nm MOSFET with the optimized device parameters (V<sub>d</sub>=0.75V, X<sub>EE</sub>=5nm, Y<sub>gd</sub>=5nm, Sw2=50nm, Xelev=100nm) and 30nm device of ref.8 (Tox=0.8nm, Vd=0.85V)

Fig.6 XEE dependences of Ids with Ygd as a parameter

Fig.7  $X_{EE}$  dependences of  $C_{para}$  with  $Y_{gd}$  as a parameter

Fig.8 X<sub>EE</sub> dependence of t<sub>pd</sub> (CMOS inverter) with Ygd as a parameter

- International Technology Roadmap for Semiconductors. [5] Available at http://public.itrs.net/

- Y. Mitani, et al., Symp. on 1996 VLSI Tech., p.176 [6] [7]

- T. Uchino et al., IEDM Tech. Dig. P.479 (1997)

- [8] Robert Chau, et al., IEDM Tech. Dig., p.45 (2000) [9]

- K. Goto, et al., IEDM Tech. Dig., p.449 (1995)

[10] T. Sukegawa, et al., Jpn J. Appl. Phys. Part1 vol.36 p.6244 (1997)

Fig.9  $Y_{gd}$  dependence of  $t_{pd}$  with  $X_{EE}$  as a parameter

(Inset: Ygd, Yi dependence of Ids in the case of X<sub>sw</sub>=5nm)

Fig.10  $Y_{gd}$  dependence of S-factor and  $V_{th}$ (X<sub>EE</sub>=5nm, Sw2=26nm and X<sub>elev</sub>=100nm. Other parameters are depicted in Fig.1)

Fig.11 Sw2 dependence of tpd with Xelev as a parameter

Table.1 (a) Optimal ranges of structural parameters extracted from the tpd degradation of 5%

(b) Electrical properties of 35nm MOSFET with optimized structural parameters (X<sub>EE</sub>=5nm, Ygd=5nm, Sw2=50nm and Xelev=100nm.Other parameters are depicted in Fig.1)

|                   | (a)             | (b)                          |              |

|-------------------|-----------------|------------------------------|--------------|

| X <sub>EE</sub>   | 5±4 (nm)        | I <sub>ds</sub>              | 652 (μ A/μm) |

| Y <sub>gd</sub>   | < 6 (nm)        | t <sub>pd</sub>              | 3.9 (psec)   |

| Sw2               | 50±20 (nm)      | S-factor                     | 72 (mV/dec)  |

| X <sub>elev</sub> | 100~130<br>(nm) | $\Delta V_{th} / \Delta L_g$ | 2.3 (mV/nm)  |