## LB-2-2

# Single-Electron Detection in Si-Wire Transistors at Room Temperature

Akira Fujiwara, Kenji Yamazaki, and Yasuo Takahashi

NTT Basic Research Laboratories

3-1 Morinosato Wakamiya, Atsugi, Kanagawa 243-0198, Japan

Phone: +81-462-40-2643 Fax: +81-462-40-4317 E-mail: afuji@aecl.ntt.co.jp

### 1. Introduction

Single-electron (SE) devices have been attracting much attention because of their low power consumption. Detection of the single electron is one of the basic functions of SE devices. Recently, we proposed a simple method of detecting the elementary charges stored in Si-wire transistors [1,2]. It is based on the electron-hole (e-h) system in a Si/SiO<sub>2</sub> quantum wire. Due to the electric field applied perpendicular to the wire direction, electrons and holes are spatially separated within the Si wire so that they do not recombine soon. With this system, stored charges in the Si wire can be sensed by the nearby flowing current of the other type of charges. We have so far reported single-hole storage and detection at 25 K, and their application to single-hole manipulation in a Si charge-coupled device [1]. Based on the operation principle of our method, two types of charge detection should be available depending on whether the transistor is n-channel or p-channel: (i) detection of stored holes by the electron current; (ii) detection of stored electrons by the hole current.

In this letter we show that both types of charge detection (single-electron and single-hole) are successfully performed at *room temperature*. We also discuss the sensitivity and the time-scale issue of our method.

## 2. Device Structure and Principle of Method

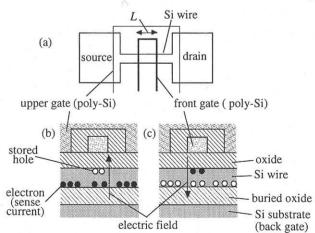

The devices were Si-wire MOSFETs fabricated on a SOI wafer. Figure 1 (a) shows the schematic top-view of the Si-wire MOSFET. The Si-wire is covered with the front poly-Si gate with the gate length L. The upper poly-Si covers a wider area and is used as an implantation mask during the formation of source and drain (S/D) regions. Both n-channel MOSFETs with  $n^+$  S/D and p-channel MOSFETs with  $p^+$  S/D were fabricated. Figures 1(b) and (c) schematically show the cross-section of the Si-wire channel and also describe how the charges

Fig. 1 (a) Schematic top-view of the Si-wire MOSFET. Schematic cross-section of the device along the Si wire with (b)  $n^+$  source and drain and (c)  $p^+$  source and drain.

are stored and sensed for the n-channel MOSFET and the pchannel one, respectively. In the case of the n-channel MOSFET, the front gate voltage  $(V_{fg})$  is negatively biased to store a small number of holes at the top Si/SiO2 interface. On the other hand, the backgate (substrate) voltage  $(V_{bg})$  is positively biased so that the back n-channel can open at the bottom Si/SiO<sub>2</sub> interface. The electric filed (~105V/cm) across the Si wire keeps the holes and the electrons apart, preventing them from recombining soon. Since the back n-channel potential is biased due to the stored holes, the n-channel current can sense the number of holes. In the case of the p-channel MOSFET,  $V_{fg}$  is positively biased and  $V_{\rm he}$  is negatively biased. Electrons under the front gate can be sensed by the hole current. The Si wire is cylindrical and the diameter is estimated to be about 20 nm. Thickness of the gate oxide that surrounds the Si wire is about 40 nm. The buried oxide is 400-nm thick. The SiO<sub>2</sub> spacer between the front gate and the upper gate is 30-nm thick.

### 3. Experimental Results and Discussion

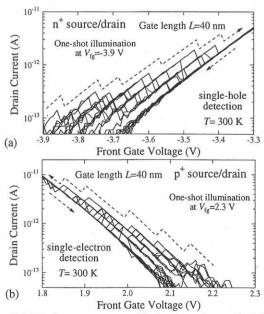

Figures 2 (a) and (b) show the drain current as a function of  $V_{\rm fg}$  for the n-channel MOSFET and the p-channel MOSFET, respectively. The gate length (*L*) is 40 nm. The drain voltage was 100 mV. For the n-channel MOSFET,  $V_{\rm fg}$  was scanned from -3.9 V to -3.3 V, and then back to -3.9 V with the scan speed of 22 mV/s while  $V_{\rm bg}$  and the upper gate voltage ( $V_{\rm ug}$ ) were kept at 45 and 0.15 V, respectively. Before each scan, the device was illuminated once with a halogen lamp at the starting  $V_{\rm fg}$ . Due to this one-shot illumination, the holes are stored under the front gate since the potential well is formed along the top interface.

Fig. 2 (a) Drain current versus  $V_{fg}$  for the n-channel MOSFET with L=40 nm. (b) Drain current versus  $V_{fg}$  for the p-channel MOSFET with L=40 nm. Dashed lines with an arrow are guides for the eye.

Then, the scan was carried out in the dark. In Fig. 2, the overlay of the results for several runs (one-shot illumination and scan) is shown. Being affected by the store holes, back-channel current begins to flow, but suddenly jumps to some lower level due to single e-h recombination. Thus, the hole number  $(n_h)$  can be detected by the electron current level. In Fig. 2 (a),  $n_h$  changes from 6 to 0 during the forward scan.

For the p-channel MOSFET,  $V_{\rm fg}$  scan was from 2.3 V to 1.8 V, then back to 2.3 V.  $V_{\rm bg}$  and  $V_{\rm ug}$  were -80 V and -1 V, respectively. As is similar to the n-channel case, the number of stored electrons  $(n_{\rm e})$  can be clearly determined, showing the versatility of the proposed method.

Here we discuss the detection sensitivity. One possible index is the current change due to a single charge. In the subthreshold region, the sensitivity factor  $(F_s)$  can be defined as

$$F_{\rm s} \equiv I_{\rm n+l}/I_{\rm n} = \exp\left(E_{\rm c}/kT\right).$$

(1)

Here,  $I_{n+1}$  and  $I_n$  represent the current level when the number of stored charges are n+1 and n, respectively.  $E_c$  represents the change in channel potential due to a single charge. For the present devices,  $F_s$  ( $E_c$ ) was estimated to be 1.7 (30 meV) for the n-channel device and 1.5 (25 meV) for the p-channel one. The obtained  $E_c$  agrees reasonably with that estimated from the device size. If the cylindrical Si wire with L=40 nm is assumed, the gate capacitance ( $C_g$ ) is calculated to be 5.4 aF. Then,  $e^2/C_g$  is 30 meV. Further reduction and optimization of the device size and structure will lead to larger  $E_c$  and  $F_s$ . It should be noted that the subthreshold swing in Fig. 2 deviates from the ideal value since the channel under the front gate is also capacitively coupled to the upper gate due to the relatively thick gate oxide.

Another important issue is the lifetime of e-h recombination and generation. These times are key parameters for controlling the elementary charge in our e-h system. Figures 3 (a) and (b) show the time dependence of the drain current for the n-channel device when  $V_{fg}$  is fixed at -3.5 V. Under a dark condition, the current indicates  $n_{h}=0$  almost all the while, but a single hole is

Fig. 3. Time dependence of the drain current for the n-channel MOSFET (a) in the dark and (b) under illumination. Current levels corresponding to each  $n_{\rm h}$  are indicated by bars.

Fig. 4. (a) Histogram of the time for which the state  $n_h=1$  persists until it changes to  $n_h=0$ . (b) Histogram of the time for which the state  $n_h=2$  persists until it changes to  $n_h=1$ .

generated and stored approximately once per 60 s. Under continuous illumination, holes are generated more frequently and they also recombine. One-by-one increase and decrease of  $n_h$  results in multi-level fluctuations as show in Fig. 3(b). By analyzing the data, we can estimate the recombination lifetime.

Figures 4 (a) and (b) show histograms of the time for which the state  $n_h=1$  persists until it changes to  $n_h=0$  and the time of  $n_h=2$  to  $n_h=1$ . From the histograms, the recombination lifetimes are estimated to be 4 and 2 s for  $n_h=1$  and  $n_h=2$ , respectively. The reason the time for  $n_h=1$  is twice that for  $n_h=2$  can be attributed mainly to the difference in the probability that a hole encounters flowing electrons. If the current level becomes lower, the hole has less chance to recombine with an electron. In fact, the factor of 2 coincides well with the ratio of  $I_2$  and  $I_1$ , which corresponds to  $F_s$  of 1.7 as shown in eq. (1). This indicates that the recombination lifetime is inversely proportional to the sensing current.

The mechanism of the e-h generation (thermal excitation, contribution of midgap trap centers) and that of the e-h recombination (nonradiative or radiative) in this small system are interesting subjects, but are not yet clear. Further investigation will be needed.

#### 5. Summary

We demonstrated both single-electron and single-hole detection in Si-wire MOSFETs at room temperature. While the e-h generation lifetime was on the order of a minute, the recombination lifetime of a few seconds was obtained at subpA sensing currents. The validity of our method for both types of charges will open up the possibility that we can manipulate a single electron and single hole, and, moreover, control their recombination in the present e-h system.

#### References

- [1] A. Fujiwara and Y. Takahashi, Nature 410, 560 (2001).

- [2] A. Fujiwara and Y. Takahashi, Silicon Nanoelectronics Workshop in 2001, (2001) p.40.