## Low-Temperature Electrical Characteristics of Strained-Si MOSFETs

## Nobuyuki Sugii and Katsuyoshi Washio

Central Research Laboratory, Hitachi, Ltd., Kokubunji-shi, Tokyo 185-8601, Japan Phone: +81-42-323-1111, Fax: +81-42-327-7764, E-mail: sugii@crl.hitachi.co.jp

The strained-Si MOSFET is attracting much attention these days because of its high electron and hole mobilities. Many research groups have enhanced the performance of this device [1, 2]. We previously reported large increases in mobility of electrons and holes (120% and 42%, respectively) compared to a conventional Si-MOSFET in a strained-Si MOSFET with a chemo-mechanical polished SiGe substrate [3]. There have been many theoretical investigations on the mechanism of the increase in mobility [4, 5], although a discrepancy between experimental and theoretical values still exists. It is necessary to investigate mobility-limiting mechanisms of the strained-Si MOSFET. Useful information can be gained from mobility measurements at low-temperature. But there are few reports on the low-temperature mobility [6]. Accordingly, in this study, we investigated temperature dependence of both electron and hole mobilities in a strained-Si MOSFET.

Details of the device fabrication are described elsewhere [3]. Channel-doping density was around  $4\times10^{17}$ /cm³. The gate-oxide thickness was 4 nm, and n<sup>+</sup>- and p<sup>+</sup>- poly-Si gate electrodes were used. Electrical characteristics of the devices were measured by using a low-temperature wafer prober in a temperature range of 83-300 K.

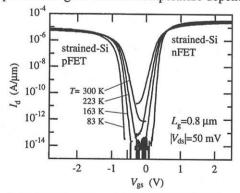

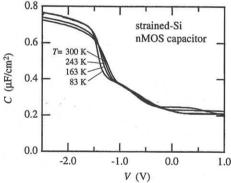

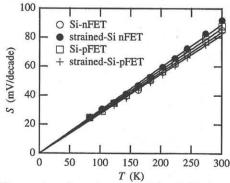

The  $I_d$ - $V_{os}$  characteristics of the strained-Si devices with  $L_a$  of 0.8  $\mu$ m are shown in Fig. 1. With decreasing temperature, threshold voltage  $|V_{th}|$  decreases, and on-state  $I_d$  and subthreshold slope (S) increase. The  $|V_{th}|$  values of all the devices at 83 K are approximately 0.2 V higher than those at 300 K. This result is consistent with that from device modeling at low temperatures [7]. High-frequency (1 MHz) C-V characteristics of the strained-Si nMOS capacitor are shown in Fig. 2. Accumulation-state capacitance (V<-2 V) increases a little with decreasing temperature. This increase suggests that gate-oxide capacitance slightly (<5%) increases with decreasing temperature. Since minimum capacitances among all the devices under a depletion-inversion state (V > -0.5 V) are identical and do not depend on temperature, the space charges of all the devices seem to be the same and independent of temperature. Figure 3 shows temperature dependence of S

Fig. 1  $I_{\rm d}$ - $V_{\rm gs}$  characteristics of strained-Si MOSFETss with  $L_{\rm g}$ =0.8  $\mu$ m.

for devices with  $L_{\rm g}$  of 0.8 µm. If space charge and interface-trap charge densities are constant, S should be proportional to temperature. The result indicates that interface-charge densities of all the devices are almost the same because their space-charge densities are the same. The interface state between the gate oxide and the strained-Si channel therefore seems to be the same as that for conventional Si devices.

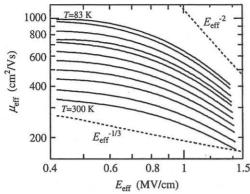

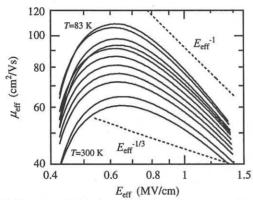

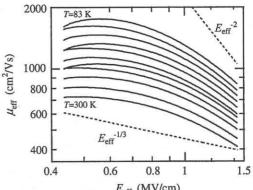

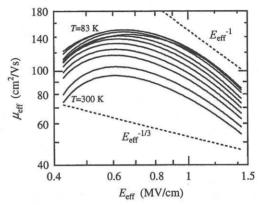

Figures 4-7 show electron and hole mobilities ( $\mu_{\rm eff}$ ) as a function of effective electric field ( $E_{\rm eff}$ ). At 300 K,  $\mu_{\rm eff}$  in the Si control devices is identical to the universal values [8] under high  $E_{\rm eff}$  (>0.8 MV/cm). This indicates that mobilities are mainly limited by phonon and surface-roughness scattering. With decreasing temperature,  $\mu_{\rm eff}$  increases because the contribution of phonon scattering decreases. But in the nFETs, unlike the results in the literature [8], the contribution of surface-roughness scattering ( $E_{\rm eff}^{-2}$ ) is still weak below 100 K. This may be because the contribution of Coulomb scattering is strong because of high channel-doping density. Mobilities of the strained-Si devices are higher than those of the conventional ones throughout the measured temperature range.

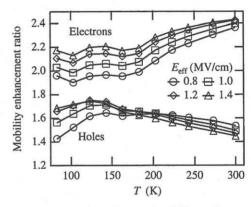

Mobility-enhancement ratio of the strained-Si devices over corresponding conventional-Si devices is plotted in Fig. 8. Surprisingly, the enhancement ratio does not significantly decrease with decreasing temperature; on the contrary, the

Fig. 2 High-frequency C-V characteristics of a strained-Si nMOS capacitor.

Fig. 3 Temperature dependence of subthreshold slope (S) of the  $L_e$ =0.8  $\mu$ m devices.

Fig. 4 Electron mobilities ( $\mu_{\rm eff}$ ) of Si control devices as a function of effective electric field ( $E_{\rm eff}$ ). Measurements were done at 83, 103, 123, 143, 163, 183, 203, 223, 243, 273, and 300 K.

Fig. 6 Hole mobilities ( $\mu_{\rm eff}$ ) of Si control devices at the same temperatures as in Fig. 4.

ratio for holes increases slightly ( $E_{\rm eff} \ge 1~{\rm MV/cm}$ ). As explained in the literature [4, 9], if the electron-mobility enhancement is due to a decrease of the inter-valley phonon scattering, the electron-mobility enhancement should be less than 10% below 100 K. Moreover, under a high electric field ( $E_{\rm eff} \ge 1~{\rm MV/cm}$ ), the enhancement should be small [9], even at room temperature, because the two dimensionality of the inversion layer is enhanced with increasing  $E_{\rm eff}$ , and the reduction of the inter-valley scattering occurs even in the conventional Si devices. Thus, the present experimental results cannot be explained only by the mechanism reported so far. Further investigations such as mobility measurements with different channel-dose amounts, as well as theoretical investigations of mobility-limiting mechanisms of strained-Si devices, are necessary.

In summary, we measured low-temperature electrical characteristics of strained-Si MOSFETs in order to understand the mobility-limiting mechanism in this device. We found that, unlike previous theoretical investigations, both the electron and hole mobilities do not significantly decrease with decreasing temperature. These results cannot be explained by the mechanisms reported so far; namely, electron-mobility enhancement is not only caused by the reduction of phonon scattering by the valley splitting.

## Acknowledgments

We thank the staff of the pilot line at Hitachi's Central Research Laboratory (HCRL) for the wafer processing, Dr. Shin'ichiro Kimura, Mr. Digh Hisamoto, and Natsuki Yokoyama of HCRL for

Fig. 5 Electron mobilities ( $\mu_{\rm eff}$ ) of strained-Si devices at the same temperatures as in Fig. 4.

Fig. 7 Hole mobilities ( $\mu_{\rm eff}$ ) of strained-Si devices at the same temperatures as in Fig. 4.

Fig. 8 Temperature dependence of mobility-enhancement ratio of strained-Si devices over corresponding conventional Si devices.

their discussions on the device fabrication, and Katsutaka Kimura and Dr. Takahiro Onai of HCRL for their encouragement.

## References

[1] K. Rim et al., IEEE Trans. Elec. Dev. 47, 1406 (2000). [2] T. Mizuno et al., IEEE Elec. Dev. Lett. 21, 230 (2000). [3] N. Sugii et al., Tech. Dig. Int. Electron Devices Mtg., 2001, pp. 737. [4] S. Takagi et al., J. Appl. Phys. 80, 1567 (1996). [5] R. Oberhuber et al., Phys Rev. B 58, 9941 (1998). [6] J. Welser et al., Tech. Dig. Int. Electron Devices Mtg., 1994, pp. 373. [7] S. Selberherr, IEEE Trans. Elec. Dev. 36, 1464 (1989). [8] S. Takagi et al., IEEE Trans. Elec. Dev. 41, 2357 (1994). [9] G. Formicone et al., Solid-State Electronics 41, 879 (1997).