# B-9-4

# Performance of DRAM Cell Transistor with TDSE (Thermal Desorption Silicon Etching) and Selective Si Channel Epi techniques

C.-S. Kim, B.C. Lee, J.R. Ryu, D.-H. Lee, <sup>†</sup>J.-H. Ku, S. Choi,

U.I. Chung, and J.T. Moon

Process Development Team, Memory Division, Samsung Electronics Co., Ltd.

Advanced Process Development Project, System LSI Division, Samsung Electronics Co., Ltd.

San #24, Nongseo-Ri, Kiheung-Eup, Yongin-City, Kyunggi-Do, Korea, 449-711 Tel: 82-31-209-6329, Fax: 82-31-209-6299, e-mail: chulsung@samsung.co.kr

### 1. Abstract

TDSE (Thermal Desorption Silicon Etching) process is introduced before Si channel-epi growth using UHV-SEG (Selective Epitaxial Growth) technique to improve transistor performance in DRAM device. Compared with the conventional channel-epi which shows the degradation of transistor characteristics due to the raised active profile, TDSE structure with channel-epi presents superior transistor performance in terms of transistor hump characteristics and inverse narrow width effect (INWE).

#### 2. Introduction

Silicon SEG (Selective Epitaxial Growth) has been widely investigated in terms of device integrations and transistor performance [1-5]. Channel-epi engineering using SEG is one of the key technologies for improving the mobility and short channel effect of MOSFETs [6]. DRAM cell transistor with channel-epi, however, has not been studied in details. Raised active profile from channel-epi growth at small bar-type cell shows transistor hump at the edge of cell, which decreases threshold voltage (Vth) of cell transistor and eventually results in degradation of dynamic refresh characteristics in DRAM. To improve DRAM cell transistor, TDSE (Thermal Desorption Silicon Etching) technique has been developed and integrated with channel-epi for the first time. In this paper, the improved transistor characteristics with TDSE and channel-epi processes are described.

# 3. Experimental

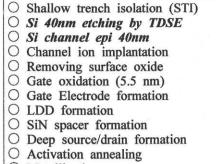

DRAM FEOL (Front End Of Line) process flow is illustrated in Table 1. An STI process was performed After wet cleaning, TDSE process was ing Cl<sub>2</sub> gas at 700 °C in UHV chamber. for isolation. carried out using  $Cl_2$  gas at 700 °C in UHV chamber. The process pressure was 10<sup>6</sup> torr. Following the TDSE process, In-situ Si channel-epi is grown at the same chamber. The selectively grown Si channel was doped by ion implantation through a sacrificial oxide layer. After the removal of sacrificial oxide layer, 5.5 nm of nitrided oxide was grown as a gate dieletric. For the formation of gate electrode, phosphorus doped polysilicon and WSi<sub>x</sub> are sequentially grown on gate oxide. The lightly doped drain (LDD) and deep source/drain were formed by phosphorus and arsenic ion implantations, respectively.

# 4. Results and Discussion

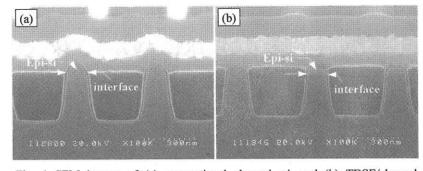

Figure 1 shows the cross sectional SEM images of DRAM cell with conventional channel-epi and TDSE/ channel-epi. As shown in Figure 1, TDSE/ channel-epi technique can align Si epi surface with STI top surface, while conventional channel-epi results in raised active profile with strong Si (111) facet. Figure 2 is the distribution of Vth for three different cell transistors. TDSE/channel-epi transistor exhibits higher  $V_{th}$  of cell transistor compared to conventional channel-epi and reference (no channel-epi) cell transistors. The higher Vth

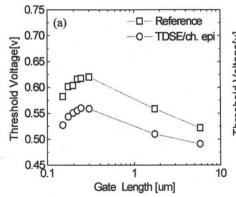

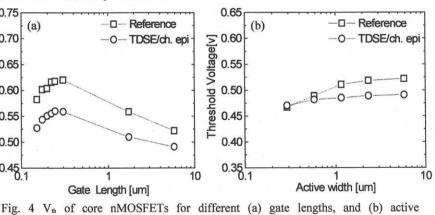

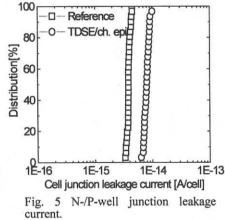

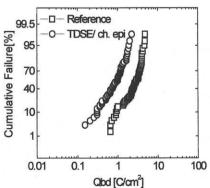

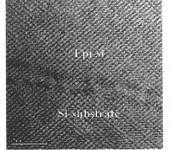

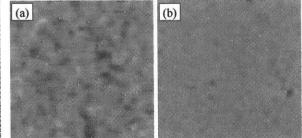

for TDSE/channel-epi transistor may be attributed to active corner rounding formed by TDSE and SEG processes [7]. Shown in Figure 3 are the  $L_{4}$ -V<sub>g</sub> characteristics for different back biases. Using TDSE/ channel-epi technique, the Id-Vg characteristics for different back biases are significantly improved while conventional channel-epi transistor shows severe hump characteristics as back bias increases. Figure 4 is the V<sub>th</sub> of core nMOSFETs for different gate lengths and active widths. As shown in Figure 4, less inverse narrow width effect (INWE) is identified for TDSE/ channel-epi transistor than for reference transistor (no channel epi). It can be also suggested that the improved INWE is ascribed to active corner rounding for core nMOSFETs. The N-/P-well junction leakage and Qbd characteristics are depicted in Figure 5 and Figure 6, respectively. From the Figure 5 and 6, it is identified that both junction leakage and  $Q_{bd}$  characteristics are degraded by TDSE/channel-epi process. TEM image in Figure 7 suggests that the degradations of junction leakage and  $Q_{bd}$  characteristics may be related to the defects at channel epi/Si-substrate interface, which is originated from rough Si surface after TDSE process. Therefore, it is expected that the degradations of junction leakage and  $Q_{bd}$  characteristics can be improved by minimizing initial Si roughness before channel epi growth via H2 added TDSE or H<sub>2</sub> annealing after TDSE process (Figure 8).

#### 5. Conclusion

TDSE (Thermal Desorption Silicon Etching) process is introduced before Si channel-epi growth using UHV-SEG (Selective Epitaxial Growth) technique to improve transistor performance in DRAM device. Compared with the conventional channel-epi which shows the degradation of transistor characteristics due to the raised active profile, TDSE structure with channel-epi presents superior transistor performance in terms of transistor hump characteristics and inverse narrow width effect (INWE). In addition, it is suggested that the degradations of junction leakage and Qbd characteristics can be improved by minimizing initial Si roughness before channel-epi growth via H<sub>2</sub> added TDSE or H<sub>2</sub> annealing after TDSE process.

#### References

H. Koga et al., IEDM Tech. Dig., p.25, 1997.

Satoshi Yamakawa et al., IEEE Electron Device Letters, 20(7), p.366, 1999.

[3] Emmanuel Augendre et al., IEEE Tran. Electron Devices, 47(7), p.1484, 2000.

[4] A. Hokazono et al., IEDM Tech. Dig., p.243, 2000.

[5] Yoshiki Kamata et al., Extended Abstracts of the 2001 International Conference on Solid State Devices and Materials, 2001, p.150, 2001.

[6] Kenji Noda et al., IEEE Tran. Electron Devices, 45(4), p.809, 1998.

[7] H. S. Uh et al., Symp on VLSI Tech., p.27, 2001.

Metallization 0

Table 1. Process flow for DRAM fabrication.

10<sup>0</sup>

10

10

10

10-

10<sup>-10</sup>

10-12

10

0.0

epi transistors.

Drain Current, I<sub>d</sub>A

(a)

voltage of cell transistor. Reference indicates no channel-epi transistor.

1.0

Gate Voltage, V, [V]

0.5

=0,-1,-2,-3V

1.5

2.0

widths.

Fig. 6  $Q_{bd}$  characteristics of nitrided gate oxide 5.5nm.

7 TEM of Fig. image TDSE/channel-epi layer. The image shows defects at Si-substrate and epi-Si interface.

Fig. 8 Atomic force microscopic (AFM) view of Si surface (a) after TDSE (Cl<sub>2</sub>)/channel-epi growth (RMS= 0.460nm), and (b) after TDSE (Cl<sub>2</sub>+H<sub>2</sub>)/channel-epi 0.460nm), and (b) after growth (RMS =0.356nm).

Fig. 1 SEM images of (a) conventional channel-epi, and (b) TDSE/channel -epi transistors.

10

10

10

10

10

10-10

10

10

2.0

Fig. 3 Id-Vg characteristics of (a) conventional channel-epi, and (b) TDSE/channel-

0.0

0.5

1.0

Gate Voltage, V [V]

Drain Current, I<sub>d</sub>[A]

1,-2,-3

1.5

(b)