# C-7-3

# Impact of Nitrogen Profile on Negative-Bias Temperature Instability and CMOS Performance

M.Terai, T.Yamamoto, K.Watanabe, M.Togo, K.Masuzaki, N.Ikezawa, T.Tatsumi, and T.Mogami

Silicon Systems Research Labs., NEC Corporation

1120 Shimokuzawa, Sagamihara, kanagawa 229-1198, Japan

Phone:+81-42-779-6193, Fax:+81-42-771-0886, E-mail:m-terai@cj.jp.nec.com

#### Abstract

We have investigated an impact of nitrogen profile in SiON gatedielectric on negative bias temperature instability (NBTI) and sub-100-nm CMOS device performance. The main component of the V<sub>T</sub> shift caused by NBTI is found to be increased interface trapping, and interfacial nitrogen enhances the generation of interface traps. Suppressing the interfacial nitridation through radical nitridation improved the NBTI lifetime. CMOS circuits with a low-interfacial-nitrogen SiON gate-dielectric formed using N-radicals performed  $(1/\tau_{PD})$  10% better and were ten times as reliable.

### Introduction

A low-leakage, highly reliable ultrathin SiON gate-dielectric is essential to achieve high-performance sub-100-nm CMOS devices [1]. SiON gate-dielectrics fabricated by various techniques have been reported [2]-[4]. However, nitrogen incorporation into an ultrathin gate oxide increases NBTI [5]. In this paper, we investigate nitridation process and an impact of nitrogen profile in SiON gate-dielectric on device properties and reliability, and discuss the NBTI mechanism.

## **Gate-dielectric fabrication**

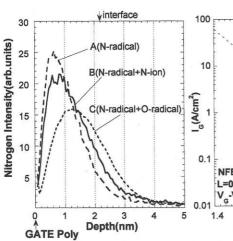

We fabricated ultrathin SiON films by using an electroncyclotron resonance (ECR) plasma. Three processes of nitridation (A: N-radicals, B: N-radicals + N-ions, and C: N-radicals + Oradicals) were applied after 1.6-nm (A and B) or 1.2-nm (C) radical-base SiO<sub>2</sub> formation to control the nitrogen profiles. Figure 1 shows SIMS profiles of the nitrogen in the gate SiON fabricated under the three processes. The Si/SiON interface was located at 2.2 nm. Process "C" led to a broad nitrogen profile with a high nitrogen intensity at the interface. Process "A" formed a steep nitrogen profile with low nitrogen intensity at the interface. The interfacial nitrogen intensity obtained through process "B" was higher than that with process "A" because the N-ions used in process "B" correctly nitridate the interface.

### **Results and discussion**

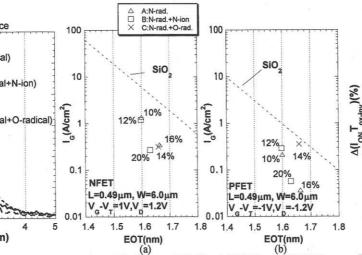

# A) Gate-leakage current and drivability

Figure 2 shows the I<sub>G</sub>-EOT (equivalent oxide thickness) characteristics of SiON films fabricated by process "A", "B", and "C". The nitrogen concentration measured by XPS (N<sub>XPS</sub>) is also shown. Nitridation decreased the gate-leakage current for both the NFET (Fig. 2(a)) and the PFET (Fig. 2(b)). Figure 3 shows the  $N_{\text{XPS}}$  dependence on the  $I_{\text{ON}}T_{\text{OX-inv}}$  (which is the drain current normalized by electrical oxide thickness) degradation from the SiO<sub>2</sub> in the PFET. As N<sub>XPS</sub> increased, I<sub>ON</sub>T<sub>OX-inv</sub> for all three processes deteriorated but the rate of deterioration was greater for process "B" than for process "A". If we compare SiON films with the same N<sub>XPS</sub>, process "C" led to the worst films. These results indicate that IONTOX-inv of a PFET is sensitive to the interfacial nitrogen concentration and that interfacial nitrogen degrades the hole mobility. Process "A" suppressed the interfacial nitridation and can be used to control the degradation of PFET drivability.

# B) Reliability (NBTI)

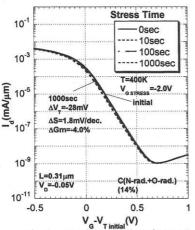

We measured the NBTI of PFETs with an S/D and an n-well electrode grounded at 400K. Figure 4 shows the  $I_p-V_G$  characteristics of a PFET, fabricated using process "C", before and after bias temperature (BT) stress. The BT stress caused a -28-mV V<sub>T</sub> shift, a 1.8-mV/dec subthreshold-swing (S) increase, and a 4% Gm degradation. The V<sub>T</sub> shift caused by the NBTI is the key to

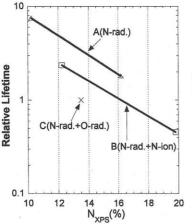

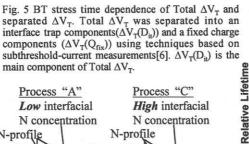

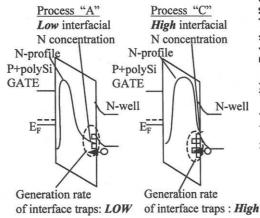

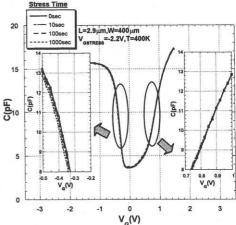

ultrathin SiON gate-dielectrics. It has been reported that the main component of the  $\Delta V_T$  caused by NBTI is due to a fixed charge increase in the SiON, but  $\Delta V_T$  was not separated into an interface trap component ( $\Delta D_{it}$ ) and a fixed charge component ( $\Delta Q_{fix}$ ) [5]. Figure 5 shows the stress-time dependence on total  $\Delta V_T$  and separated  $\Delta V_T$ . The total  $\Delta V_T$  was separated into a  $\Delta D_{it}$  component and a  $\Delta Q_{fix}$  component using techniques based on subthresholdcurrent measurement [6]. These results indicate that the main component of  $\Delta V_T$  is caused by an increase of  $D_{it}$  irrespective of the nitridation processes. To confirm the  $\Delta V_T$  component, we also carried out C-V measurements. Figure 6 shows the C-V characteristics of a PMOS with SiON film (EOT ≅ 1.8 nm, formed by process "A") before and after BT stress. The C-V curves did not shift near  $V_{FB}$  (the flatband voltage  $V_G$  was ~0.9 V), but shifted in the negative direction in inversion. Figures 5 and 6 indicate that a large quantity of interface traps was generated by BT stress while there was only a slight increase in the fixed charges. Figure 7 shows the N<sub>XPS</sub> dependence on the NBTI lifetime that fell as N<sub>XPS</sub> increased. The NBTI lifetime for the SiON films with a low interfacial nitrogen concentration (formed by process "A") were improved by about 4 times of magnitude compared to that in films with a high interfacial nitrogen concentration (those formed by process "C") at the same  $N_{XPS}$ . Figure 8 shows a schematic of the NBTI mechanism for SiON. Interfacial nitrogen enhances the generation of interface traps during BT stress, but process "A" (with N-radicals) results in so low interfacial nitridation that suppresses the NBTI degradation.

## C) CMOS performance and reliability

Figure 9 shows the total gate leakage (IGTOTAL) versus the CMOS performance  $(1/\tau_{PD})$  and the NBTI lifetime.  $\tau_{PD}$  and  $I_{GTOTAL}$  were calculated as

$\tau_{PD} = C_L V_{DD} (1/I_{ON(NMOS)} + 1/AI_{ON(PMOS)}),$

$I_{GTOTAL} = I_{G(NMOS)} + AI_{G(PMOS)},$

$A = I_{ON(NMOS)} / I_{ON(PMOS)} = constant,$ where C<sub>L</sub> and V<sub>DD</sub> are load capacitance and supply voltage, respectively.

We have demonstrated that process "A" improves performance  $(1/\tau_{PD})$  by 10% and reliability by a factor of ten compared with process "C" at the same IGTOTAL condition.

This result indicates that the steep nitridation profile with low interfacial nitrogen concentration that can be obtained by radical nitridation is important to fabricate a low gate-leakage, highperformance, and highly-reliable SiON gate-dielectric for CMOS devices.

#### Summary

We found that the main component of the  $V_T$  shift caused by NBTI is increased interface trap generation due to interfacial nitrogen. Nitridation using N-radicals, resulting in steep nitrogen profile with low interfacial nitridation, is an effective way to fabricate a low-leakage, high-performance SiON gate-dielectric that suppresses NBTI degradation in CMOS devices.

### References

[1]M.Togo et al., Symp.on VLSI Tech., p. 116, 2000.

[2] Y.Yasuda et al., Symp.on VLSI Tech., p. 83, 2001.

[3]M.Fujiwara et al., IEDM Tech. Dig, p. 227, 2000.

[4] H. Yang et al., IEDM Tech. Dig, p. 245, 1999.

- [5]N.Kimizuka et al., Symp. on VLSI Tech., p. 92, 2000.

- [6]P.J.McWhorter et al., Appl. Phys. Lett., vol. 48, p. 133, 1986.

Fig. 1 SIMS profiles of the nitrogen in SiON fabricated by different processes. Process "A" can form steep nitrogen profile with low interfacial nitrogen intensity.(Interface:2.2nm)

$V_{g}$ - $V_{T initial}(V)$ Fig. 4 I<sub>d</sub>- $V_{g}$  characteristics of a PFET before and after bias temperature (BT) stress. BT stress caused  $V_{T}$  shift, S increase, and Gm degradation.

Fig. 7 N<sub>XPS</sub> dependence of NBTI Lifetime. Process "C" (N-radicals and Oradicals) degrades lifetime much more than the others with same N<sub>XPS</sub>.

Fig. 2  $I_{g}$  vs. EOT for (a)NFET and (b)PFET. Open triangles indicate process "A". Open squares indicate process "B". Cross mark indicates process "C". Nitrogen concentration estimated by XPS (N<sub>XPS</sub>) are also indicated.

Fig. 8 Schematic of NBTI mechanism for SiON. Interfacial nitrogen enhances the generation of interface trap during BT stress. Process "A" results in low interfacial nitridation that suppresses NBTI degradation.

OZ

Fig. 3  $N_{XPS}$  dependence of  $\Delta(I_{ON}T_{OX-INV})$  degradation from radical SiO<sub>2</sub> in PFET. degrades  $\Delta I_{ON}$  or access "C" (N-radicals of  $Q_2$  m PTP1) degrades  $\Delta I_{ON} T_{OX-NV}$  much more than the others with the same N<sub>XPS</sub>.

$L_{\rm product} = 1000 \, {\rm gamma} / 1000 \, {\rm gamm$ degradation in CMOS devices.