# New multi layer top electrode of SRO/IrOx for 0.35µm FRAM

Yoshimasa Horii, Jeffrey S. Cross<sup>1</sup>, Naoyuki Sato, Soichiro Ozawa, Katsuyoshi Matsuura,

Mitsushi Fujiki, Takeyasu Saito, Satoru Mihara, Takashi Eshita,

Shan Sun<sup>2</sup>, Fun Chu<sup>2</sup>, Glen Fox<sup>2</sup>, Rick Baily<sup>2</sup>, Tom Davenport<sup>2</sup> and Tatsuya Yamazaki

Fujitsu Limited, FRAM Development Department,

4-2 Nishine-Moriyama, Kanegasaki, Isawa-gun, Iwate, Japan

Phone: +81-46-250-8281, Fax: +81-46-250-8804, E-mail: horii@ed.fujitsu.co.jp

<sup>1</sup> Fujitsu Laboratories Ltd., Inorganic material laboratories,

10-1 Morinosato-Wakamiya, Atsugi, Kanagawa, 243-0197, Japan

<sup>2</sup> Ramtron International Corporations,

1850 Ramtron Drive, Colorado Springs, Co 80921, USA

### 1. Introduction

Smart cards or multi-purpose IC cards and highly secured electronic devices need high performance nonvolatile memory in the future. In these application, FRAM is the most suitable memory because of its high access speed and low power consumption. We reported that our 0.35  $\mu$ m 256 kbit FRAM showed good performance [1], such as less than 50 ns access time at a low voltage of 3.3 V and good retention. It is also reported that SrRuO<sub>3</sub> (SRO) electrode improves ferroelectric properties [2,3]. We developed a new SRO/IrO<sub>x</sub> top electrode system for FRAM. In this paper, we describe capacitors with our new developed SRO/IrO<sub>x</sub> top electrode and its electric properties including hydrogen (H<sub>2</sub>) endurance examination.

## 2. Device fabrication and characterization

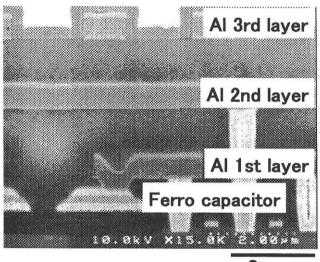

Our newly developed ferroelectric capacitor consisted of SRO/IrOx/PZT/Pt. This structure varies from previous bi-layer top electrodes [2] because the SRO film was not in direct contact with PZT. Figure 1 shows the cross sectional SEM image of 0.35 µm FRAM structure. PZT was deposited on Pt bottom electrode by sputtering method and crystallized by rapid thermal annealing. Multi-layer top electrode (TE) of SRO/IrOx was deposited by sputtering. The conventional capacitor structure is almost the same as the new capacitor except for single  $IrO_x$  TE. The thickness of new SRO/IrO<sub>x</sub> TE and conventional IrO2 TE are about 200 nm. Patterned capacitors were encapsulated with a dielectric layer (encapsulation layer) eliminating hydrogen (H2) diffusion into the capacitor. H<sub>2</sub> generated during metal or interlayer dielectric deposition is known to degrade the ferroelectric capacitor performance [3]. After capacitor fabrication, we adopted conventional triple Al layer interconnection and inter layer dielectric (ILD) process. Technology features are summarized in Table I.

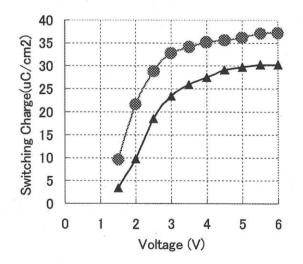

The ferroelectric capacitor with our new SRO/IrOx multi TE shows superior performance to the conventional

IrO<sub>2</sub> TE capacitor (Fig. 2). Switchable charge (Qsw) of 33  $\mu$ C/cm<sup>2</sup> at 3 V operation was obtained on the new capacitors, while a Qsw of conventional capacitor was 23  $\mu$ C/cm<sup>2</sup>. In addition better lower voltage performance is obtained the with SRO/IrO<sub>x</sub> multi layer TE. It indicates that the ferroelectric property is improved by the SRO.

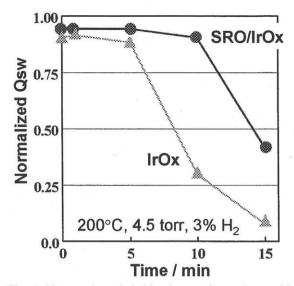

Next, we investigated the  $H_2$  endurance of ferroelectric capacitor to examine the capacitor degradation during Al interconnection and dielectric interlayer deposition. While capacitors with IrO<sub>x</sub> TE degraded immediately, capacitors with SRO/IrO<sub>x</sub> TE showed good H<sub>2</sub> endurance (Fig. 3). Changes in IrO<sub>x</sub> TE surface from black to metallic indicate that IrO<sub>x</sub> is reduced by H<sub>2</sub> and changes to metal rich IrO<sub>x</sub>[3]. It is proposed that H<sub>2</sub> diffusion and reduction of the IrO<sub>x</sub> is slower with the SRO than that of the independent IrO<sub>x</sub> TE. In other words, SRO acts a barrier or "H<sub>2</sub> blocker" to prevent the reduction of the IrO<sub>x</sub>.

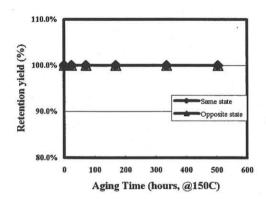

78 chips of 256 kbit FRAM are fabricated with our new capacitor. They show excellent retention (Fig. 4). No bit fail is observed until 504 hours at 150°C. It corresponds to more than 5 years reliability.

### **3.** Conclusion

We developed SRO/IrO<sub>x</sub> multi layered top electrode. Capacitors with the new top electrode have high initial switchable charge, and hydrogen degradation endurance. It indicates that the SRO top layer serves not only as an electrode but also as a H<sub>2</sub> blocker. 256 kbit FRAM with new capacitor showed excellent retention over 504 hours in 150 °C.

### References

[1] T. Yamazaki, Extended Abstracts of the 2001 International Conference on Solid State Devices and Materials, 2001 (2001) p.514

[2] J.S. Cross et. al, *Integrated Ferroelectrics* **21**(1998) p.263

[3] J.S. Cross, et. al, Jpn. J. Appl. Phys. 41, (2002) p.698

Table I. Technology feature of 0.35 µm FRAM

| Gate length               | 0.35 µm                       |

|---------------------------|-------------------------------|

| Ferro capacitor structure | SRO/IrOx/PZT/Pt               |

| Source/Drain              | TiSix                         |

| Via                       | W-plug                        |

| Metal                     | Triple Aluminum               |

| Metal pitch               | 1.1 mm                        |

| Source voltage            | 3.0 V                         |

| Cell size                 | 13.95 µm <sup>2</sup> (2T/2C) |

|                           | 8.69 µm <sup>2</sup> (1T1C)   |

| Capacitor size            | $1.50 \ \mu m^2$              |

$2 \mu m$

Fig. 1 Cross sectional view of 0.35  $\mu$ m FRAM; Ferro capacitor is consisted of SRO/IROx/PZT/Pt. Ferroelectrc capacitor is fabricated after conventional CMOS process.

Fig.2 Comparison of Qtv between SRO/IrOx/PZT/Pt ferroelectric capacitor (circles) and IrO2/PZT/Pt ferroelectric capacitor (triangles). (50µm X 50µm capacitor)

Fig. 3 Changes in switchable charge of capacitors with new SRO/IrOx top electrode (circles) and IrOx top electrode (triangles) during annealing in hydrogen atmosphere (200°C, 4.5torr, 3%)

Fig. 4. 256 kbit FRAM retention performance with new SRO/IrOx multi layer TE capacitor; No bit fail appears even after 504 hours at 150°C.