# Ultra Thin Body Silicon-On-Insulator (UTB SOI) MOSFET with Metal Gate Work-function Engineering for sub-70 nm Technology Node

Daewon Ha, Pushkar Ranade, Yang-Kyu Choi, Jeong-Soo Lee, Tsu-Jae King, and Chenming Hu

University of California at Berkeley, Department of Electrical Engineering and Computer Science 373 Cory Hall, University of California, Berkeley, CA 94720, USA Phone: +1-510-643-2558 Fax: +1-510-643-2636 E-mail: <u>daewon@eecs.berkeley.edu</u>

## 1. Introduction

Fully depleted ultra-thin-body (UTB) SOI MOSFET structures provide excellent suppression of short channel effects and hence are promising for sub-70nm technology [1],[2]. However, it is very difficult to adjust the threshold voltage ( $V_T$ ) of a UTB MOSFET by conventional channel implantation [3]. To avoid dopant fluctuation effects, a lightly doped Si body should be used, with threshold voltage adjustment achieved via gate work-function engineering. Metallic gate materials are desirable for reducing resistance, and for eliminating the gate depletion effect as well as dopant penetration through ultra-thin gate dielectrics. In this paper, threshold voltage adjustment for Mo-gated UTB MOSFETs by nitrogen implantation is demonstrated for the first time.

## 2. Device Fabrication

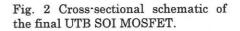

Fig.1 summarizes the sequence of process steps used to fabricate UTB MOSFETS in this work, and Fig.2 provides a cross-sectional schematic of the final structure. The initial SOI film (p-type, 15 $\Omega$ -cm, <100>, T<sub>Si</sub>/T<sub>BOX</sub>=100nm/400nm) was thinned down to ~10nm by thermal oxidation. The body thickness was chosen not to be too thin, to avoid VT shifts due to quantum confinement [4]. After active-area patterning, the gate dielectric was formed by thermal oxidation (2.5nm) and the Mo gate film (40nm) was deposited in a DC magnetron sputtering system at 200°C (10-7 Torr base pressure). Then, nitrogen implantation was performed at various doses (see Table I for experimental split conditions). N+ poly-Si and a SiO2 hard-mask layer were then deposited. The purpose of the hard mask was to prevent shorting of the source and drain (S/D) during the subsequent selective deposition of Ge to form raised S/D contact regions (Fig. 2). A highly selective dry etch process (selectivity > 70:1) was developed to etch the Mo gate on thin gate oxide. After gate-sidewall spacer formation, Ge was deposited selectively and S/D implants were performed. Device fabrication was completed with a 60s, 700°C RTA in N2 ambient to activate the implanted S/D dopants. This conservative anneal was used because Ge and Si intermixing is known to be enhanced in the presence of dopants [6], for the formation of abrupt and shallow pn junctions with low thermal budget.

## 3. Results and Discussion

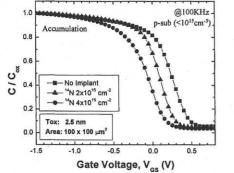

Fig.3 shows the measured high-frequency C-V curves for bulk-Si control devices implanted with various doses of  $^{14}N^+$  (Table

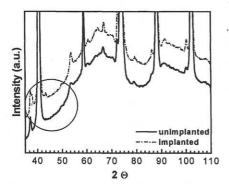

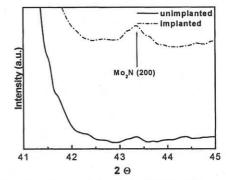

I). The shift in flat-band voltage  $V_{FB}$  is proportional to the implant dose ( $\Delta V_{FB} = 65 \text{mV}/1 \times 10^{15} \text{ cm}^{-2}$ ). Since nitrogen diffuses rapidly in Mo and segregates to the Mo-SiO<sub>2</sub> interface [5], the concentration of nitrogen at the interface is dependent on the total nitrogen dose implanted inside the Mo film. Fig.4 shows XRD analysis results for two different samples. The sample implanted with nitrogen shows several diffraction peaks corresponding to Mo<sub>2</sub>N. This is evidence that Mo is chemically modified to Mo<sub>2</sub>N at the interface, to effect a reduction in gate work-function.

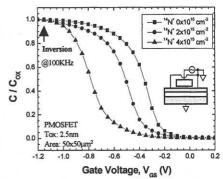

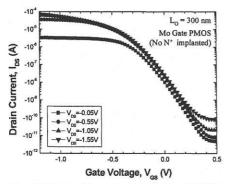

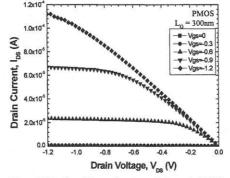

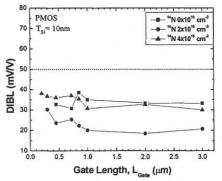

$V_T$  was extracted for the UTB MOSFET using the  $g_{m,max}$  method, as shown in Fig.6. The Mo-gated PMOS  $V_T$  is -0.2V, and shifts by approximately -65mV for every  $1 \times 10^{15} \text{ cm}^{-2}$  increment in  $^{14}\text{N}^+$  implant dose (Fig.7). Thus, the threshold voltage of UTB MOSFETs can be effectively adjusted via gate work-function engineering. In order to achieve the desired  $V_T$  (0.2~0.3V) in n-channel UTB MOSFETs, and estimated dose of 6~8x10<sup>15</sup> cm<sup>-2</sup> is needed. Fig.8 shows measured DIBL for UTB PMOSFETs. Despite the lightly doped (10<sup>15</sup> cm<sup>-3</sup>) body, DIBL is greatly suppressed (< 40mV/V) because of the ultra-thin body.

### 4. Summary

Metal gate work-function engineering is demonstrated to be feasible for adjusting the  $V_T$  in UTB SOI MOSFETs, for the first time. Mo gate technology is an attractive candidate for future CMOS technologies employing UTB MOSFET structures, particularly for multiple- $V_T$  applications.

## Acknowledgement

This work is supported from the MARCO Focused Research Center on Materials, Structures, and Devices which is funded at the Massachusetts Institute of Technology, in part by MARCO under contract 2001-MT-887 and DARPA under grant MDA972-01-1-0035. The authors would like to thank the staff of the Microlab in University of California, Berkeley.

## References

- [1] Y.-K. Choi et al., IEEE Electron Device Lett., 22, 447 (2001)

- [2] J. Kedzierski et al., IEDM Technical Digest, p.437 (2001)

- [3] L. Chang et al., IEDM Technical Digest, p.719 (2000)

- [4] Y.-K. Choi et al., 2001 Symp. VLSI Technology, p.19

- [5] K.T. Ho et al., Thin Solid Films, 127, 171 (1985)

- [6] P. Ranade, et al., Electrochemical & Solid State Letters, 5, p. G5, (2002)

Table I. Process split conditions

|        | Initial<br>WF                                             | <sup>14</sup> N <sup>+</sup> Implant<br>Condition |

|--------|-----------------------------------------------------------|---------------------------------------------------|

| Ctrl 1 | Bulk<br>P-type<br><10 <sup>15</sup> cm <sup>-3</sup>      | No Implant                                        |

| Ctrl 2 |                                                           | 20KeV, 2x10 <sup>15</sup> cm <sup>-2</sup>        |

| Ctrl 3 |                                                           | 20KeV, 4x10 <sup>15</sup> cm <sup>-2</sup>        |

| Smpl 1 | UTB SOI<br>P-type<br>(10 <sup>15</sup> cm <sup>-3</sup> ) | No Implant                                        |

| Smpl 2 |                                                           | 20KeV, 2x10 <sup>15</sup> cm <sup>-2</sup>        |

| Smpl 3 |                                                           | 20KeV, 4x10 <sup>15</sup> cm <sup>-2</sup>        |

Fig. 3 Measured high-frequency CV curves of bulk-Si control devices after RTA.

Body Thinning & Active Formation Gate Stack (SiO<sub>2</sub>/Mo)

- Nitrogen Implantation

- Poly-Si/LTO Deposition

- Gate & Gate Spacer Formation

- Raised Ge S/D Formation

- S/D Implantation & RTA

Fig. 1 Sequence of fabrication steps for UTB SOI MOSFET.

40/10 1 0/10 V<sub>DS</sub>=-0.05V PMOS 300nn Drain Current, I<sub>Ds</sub> (A) -3.0x sconductance, -2.0x10 1.0x10 gm 0/10 -1.0x10 R 0.0 -0.0L -1.0 -0.4 -0.6 Gate Voltage, V<sub>cs</sub> (V)

50 nm

LTO

Raised

130 nm

N+ Poly

Ge S/D

40 nm

Mo

10 nm

Si

400 nm

BOX

Fig. 6 Measured high frequency CV curves for UTB capacitors. ( $V_T$ =-0.2, -0.32, -0.6)

Fig. 4 XRD analysis of Mo gate films. (a) The entire range of peaks, (b),(c) details of XRD peaks. The peaks indicate that  $Mo_2N$  is formed in the nitrogen implanted sample.

37

Fig. 7(a)  $I_{DS}$ -V<sub>GS</sub> characteristic of UTB PMOSFET.

Fig. 7(b)  $I_{DS}$ - $V_{DS}$  characteristic of UTB PMOSFET.

Fig. 8 DIBL is suppressed below 40mV/V due to the ultra thin body.

M60, (111)

38

39

40

Mo,N (112)

Fig. 5 The  $g_{m,max}\xspace$  method was used to

extract the V<sub>T</sub> of UTB MOSFET.

unimplanted

implanted

36

Intensity (a.u.)

35

783