# Reduction of Pattern-Edge Defects in Partial SOI by LII (Light-Ion Implantation) Technique

Atsushi Ogura

Silicon Systems Res. Labs, NEC Corp. 1120 Shimokuzawa, Sagamihara, Kanagawa 229-1198, Japan Phone: +81-42-771-2394, Fax: +81-42-771-2481, e-mail: a-ogura@cd.jp.nec.com

# Abstract

We demonstrated the reduction of pattern-edge defects in partial SOI by using the light-ion implantation (LII) technique. Compared to the conventional SIMOX, the LII process causes less damage and can therefore reduce the defect density at the pattern edge in partial SOI structures. An SON formed by LII process showed a further reduction of the defect density, probably because the stress induced by the SiO<sub>2</sub> formation can be minimized, and its surface was extremely flat. Therefore, the LII has great advantages for fabricating partial SOI as a substrate for SOCs.

#### **1. Introduction**

Partial SOI is attractive for the use as a superior substrate for Si on chip (SOC), because it can simultaneously provide both a high-speed logic circuit on the SOI region and high-performance DRAM cells on the bulk region. So far, patterned SIMOX, in which  $O^+$  ions are implanted through a patterned mask, has usually been used for partial SOI fabrication [1]. However, the substrates fabricated by patterned SIMOX usually contain a high defect density especially at the boundaries between the SOI and the non-SOI region.

We have demonstrated a new SOI formation technique in which  $O^+$  implantation is eliminated from the SIMOX process by applying light-ion implantation and annealing appropriately using atmospheric oxygen to enhance the oxygen precipitation at the implantation damage (LII technique) [2]. The LII causes less damage than SIMOX and can therefore provide a better crystalline quality, because the implantation damage is much less than in the conventional SIMOX. In this study, we applied the LII technique to obtain a partial SOI substrate and then evaluated the fabricated structures.

# 2. Experiment

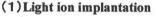

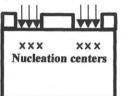

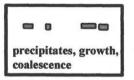

Figure 1 shows the partial SOI fabrication process using the LII technique. In this process, light ions are partially implanted into the Si substrate to create the nucleation centers for the oxygen precipitation [Fig. The sample is then annealed in the Ar/O<sub>2</sub> 1(a)]. atmosphere to enhance the oxygen precipitation. The precipitates also grow and coalesce during the annealing [Fig. 1(b)]. A partial SOI structure appears after the annealing. In the present study, we implanted He<sup>+</sup> as light ions through a 0.5-um-thick patterned SiO2 mask at a 45-KeV acceleration voltage and in 3.5  $-4 \times 10^{17}/\text{cm}^2$  doses. Then, the samples were annealed at 1340°C for four hours in an Ar/O<sub>2</sub> atmosphere at a ramping rate of 0.02 to 1°C/min from 1200 to 1340°C and at an Ar/O2 ratio of 100/1-20. The fabricated structures were evaluated by SEM and

(2) Anneal (Ar/O<sub>2</sub>)

(3) Partial SOI formation

Fig. 1 Partial SOI fabrication by LII. TEM.

# 3. Results and discussion

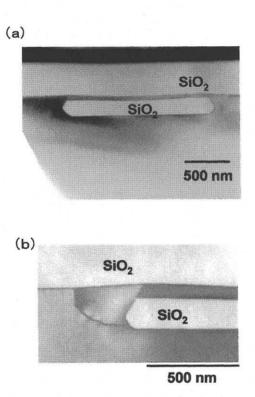

We believe the LII technique causes less damage to Si crystals and therefore fewer defects in SOI compared with conventional SIMOX. Especially for the partial SOI formation, highly defective areas at the boundaries between SOI and non-SOI regions have been a severe problem. Therefore, we thought that a partial SOI formation would demonstrate LII's high potential. Figure 2 shows the TEM image of the partial SOI formed by LII technique. The substrate surface was not completely flat, because the SOI layer was thicker at the pattern edge than that at the pattern center [Fig. 2(a)]. Some defects were also observed at the pattern edge [Fig.2 (b)]. However, both the quality of the surface flatness and that of the defect density may be better than those produced by patterned SIMOX.

By changing the annealing conditions, we could control the ratio of the volume filled by SiO2 in the insulating layer. An SOI structure with a small SiO<sub>2</sub> volume in the insulating layer may be called Si-on-nothing (SON) rather than SOI. An SON fabricated by high-aspect trench is usually formation and high-temperature annealing in an H<sub>2</sub> ambient or by preferential etching of a sacrificial layer [3]. The advantages of the LII technique are its simple fabrication process and the possibility of coating the inner surface of the buried empty space with SiO<sub>2</sub>. The defects in an SON formed by LII may also be further reduced, because stress caused by the volume expansion due to the SiO<sub>2</sub> formation should not be significant.

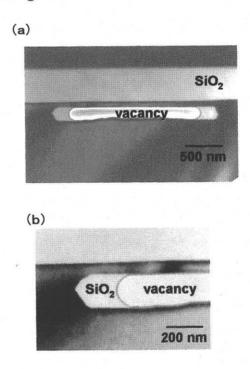

Figure 3 shows the SON fabricated by LII. The SON surface was extremely flat compared with the partial SOI and SON surfaces fabricated by other techniques, although the thickness of the insulating laver was not completely uniform [Fig. 3(a)]. This flat surface would be a great advantage for an ULSI-SOC, because state-of-the-art photolithography requires an extremely flat surface due to a focal depth Furthermore, no defects were observed, limitation. even at the pattern edge [Fig. 3(b)]. The stress induced by the buried SiO2 formation might have been minimized when the insulating layer was replaced by a vacancy from the SiO<sub>2</sub>, and therefore the pattern-edge defects disappeared. The inner surface of the buried vacancy was covered by SiO<sub>2</sub> film. This is expected to provide good interface electrical properties. The SiO<sub>2</sub> film was thicker at the sidewall than at the top and bottom.

# Acknowledgements

Fiig. 3 SON formed by LII

The authors thank Dr. Y. Mochizuki and Dr. S. Ohya for their continuous encouragement.

# References

[1] R. Hamman, et. al., 2000 Symposium on VLSI Technology, p.66 (2000).

- [2] A. Ogura, Jpn. J. Appl. Phys., 40, L1075 (2001).

- [3] T. Sato et .al., IEDM Tech. Dig. 517 (2001).