P10-7

# A Significant Improvement in Memory Retention of MFIS Structure for 1T-type Ferroelectric Memory by Rapid Thermal Annealing

Minoru Noda, Kazushi Kodama, Itaru Ikeuchi, Mitsue Takahashi and Masanori Okuyama

Area of Materials and Device Physics, Department of Physical Science, Graduate School of Engineering Science, Osaka University

1-3 Machikaneyama-Cho, Toyonaka City, Osaka, 560-8531, Japan Tel:+81-6-6850-6332 Fax +81-6-6850-6341 E-mail:noda@ee.es.osaka-u.ac.jp

## **1. Introduction**

Recently 1T-type ferroelectric memory device has attracted much attention as memory is nonvolatile and nondestructive, however, the MFIS-FET has still short memory retention time at the present stage except for a few successes[1,2]. We have studied retention degradations of the MFIS structures theoretically. It is clarified from the analysis that current flow through the ferroelectric degrades the retention characteristics[3]. Also, we have experimentally found that a furnace post-O<sub>2</sub> annealing is very successful for the improvement of retention characteristics, which leads us to obtain good quality of the M/F and F/I interfaces and the ferroelectric film[4]. However, increasing post-annealing temperature and time includes mutual diffusion and damage to interfaces in the MFIS structure, although the increase surely improves the SBT film quality then its ferroelectricity.

In this work, we newly report on that the retention time has been significantly improved up to  $6 \times 10^5$  s (about 1 week) by using rapid thermal annealing (RTA) in O<sub>2</sub> atmosphere.

### 2. Experimental

SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>(SBT) thin films were used as the ferroelectric layer, which were deposited on SiON/ n-Si(100) substrates at 550°C in O<sub>2</sub> atmosphere by PLD method by using a stoichiometric SBT ceramic target[4]. The RTA apparatus allows us to have a uniform heating area as large as 2-inch wafer size, and heating rate of about 30°C/s, respectively. With the RTA, several MFIS structures were annealed at 600 to 1000°C in O<sub>2</sub> atmosphere for 30 s and 1 min, and compared with samples of furnace annealed at 600°C in O<sub>2</sub> for 20 min.

## 3. Results and Discussion

## XRD patterns

From XRD patterns of SBT films on SiON/Si annealed at 900°C for 30 s, 900°C for 1 min, and 1000°C for 30 s, respectively, we found that all the patterns show

preferential SBT(105) peaks, which are nearly the same as that with furnace annealing previously described[4]. It is noted that the peak intensity for 1 min is larger than for 30 s at 900°C annealing, also that the intensity for 1000°Cis larger than for 900°C at the same annealing time of 30s.

(a) 900°C for 30 s and (b) 1000°C for 30 s.

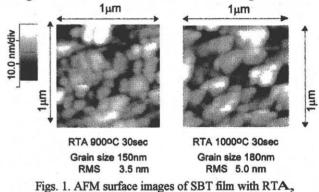

#### AFM surface views

Figures 1(a) and (b) show AFM surface views of SBT films annealed at 900°C for 30 s and 1000°C for 30 s. From the figure, as similar to the tendency in the XRD result, both the grain size and surface roughness of 150 and 3.5 nm of 900°C-annealed sample increase to those of 180 and 5 nm of 1000°C-annealed sample, respectively. The furnace annealing at 600°C and 20 min showed previously those of 80 and 9.6 nm. This means that the RTA makes larger grain size due to high temperature but much smaller surface roughness due to short time than the furnace annealing. Therefore, these lead to results that RTA is more advantageous for forming ideal MFIS structure than the furnace one, because both better ferroelectricity and lower leakage in the SBT film are obtained.

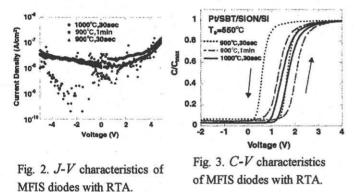

### J-V characteristics

Figure 2 shows current density(J)-voltage curves of MFIS diode for RTA of 900°C for 30 s, 900°C for 1 min, and 1000°C for 30 s, respectively. It is found that every curve shows that leakage current density is almost below

$5 \times 10^{-8}$  A/cm<sup>2</sup>, suggesting little serious mutual diffusion occurs by the RTA especially through the thin SiON buffer layer with about 20 nm thickness.

# C-V characteristics

Figure 3 shows capacitance-voltage (C-V) curves of MFIS diode for RTA of 900°C for 30 s, 900°C for 1 min, and 1000°C for 30 s, respectively. Compared to J-V characteristics in Fig. 2, some differences are seen in between their curves. As annealing time increases from 30 s to 1 min at 900°C, the C-V curve shows a positive voltage shift, a reduced memory window and degraded steepness at its transition region. This means that a mutual reaction at interface between SiON/Si and charge injection occurred. Also indicates that annealing time up to 1 min in the RTA is too long to keep a good interface at SiON/Si in the MFIS structure. This relation is almost the same when increasing annealing temperature for the same annealing time. With increasing the temperature from 900 to 1000°C for 30 s, the C-V curve shows the same tendency as the case above. Especially, the memory window becomes smaller for 1000°C than for 900°C. This also implies that time of 30 s is still long for 1000°C annealing of the MFIS structure.

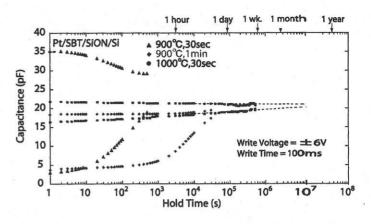

#### Capacitance retention characteristics

Retention characteristics have been finally studied for the MFIS structures with three RTA conditions (Fig. 4). The writing conditions have been decided to obtain saturated hysteresis loops. At hold states, some offset bias voltages have been applied to the diodes to have a flat-band condition. It is significantly noted that the situation observed in retention curves in Fig. 4 is much different from that in *C-V* curves in Fig. 3. The MFIS diode with 900°C for 30 s annealing has a poor retention time of less than  $10^3$  s, although its *C-V* characteristic is fairly good. The reason is considered to be due to the fact that the annealing condition might be insufficient to have enough ferroelectricity, including polarization retention. On the other hand, the diodes with 900°C for 1 min, and 1000°C for 30 s show long retention times of  $10^4$  and

Fig. 4. Retention characteristics of MFIS structures with RTA.

$6x10^5$  s (i.e. 1 week), respectively, although their C-V shapes are not so satisfactory. We think it is especially important that the latter case (1000°C for 30 s) showed a very long retention time, even though the initial ON/OFF capacitance ratio is small due to its small memory window (0.3 V). We are afraid, at present stage, that annealing condition necessary to have sufficient ferroelectric property in SBT film are not so optimized to those that can avoid interface reaction enough in the MFIS structure. It is expected from Fig. 4 that a slight and monotonous degradation of retention will be extended up to in the range of  $10^6$  s.

### 4. Summary

RTA at 900 and 1000°C in  $O_2$  atmosphere has been performed in order to improve more the retention characteristics of MFIS structures. It revealed and was understood that the RTA is more effective than the furnace one to increase grain size and decrease surface roughness in the SBT film, leading to better MFIS diode properties then improved retention characteristics. We believe the RTA treatment is essential to realize practical MFIS structures for ferroelectric nonvolatile 1T-type memory.

#### Acknowledgments

This study was partially supported by grants from Semiconductor Technology Academic Research Center (STARC), ROHM CO. LTD. and a Grant-in-Aid for Scientific Research from the Ministry of Education, Science and Culture, in Japan (No.12134205).

#### References

[1] B-E. Park and H. Ishiwara: Appl. Phys. Lett. Phys. 79 No.6, 806 (2001).

[2] K. Sakamaki, S. Migita, S-B. Xiong, H. Ota and S. Sakai: Int'l Meeting on FeRAM2001 (2001)p.182.

[3] M. Takahashi, H. Sugiyama, T. Nakaiso, K. Kodama,

M. Noda and M. Okuyama: Jpn. J. Appl. Phys. 40 2923 (2001).

[4] K. Kodama, M. Takahashi, M. Noda and M. Okuyama, Jpn. J. Appl. Phys. 41 (2002), in press.