# Annealing Effects on Interface States and Fixed Charges of TiN/Al<sub>2</sub>O<sub>3</sub>/Si MOS structure deposited by Atomic Layer Deposition

In Sang Jeon<sup>1</sup>, Jaehoo Park<sup>1</sup>, Cheol Seong Hwang<sup>1</sup>, Hyeong Joon Kim<sup>1</sup>, Jong-Ho Lee<sup>2</sup>, Nae-In Lee<sup>2</sup>, Ho-Kyu Kang<sup>2</sup>

School of Materials Science & Engineering, Seoul National University, San 56-1, Shillim-dong, Kwanak-ku, Seoul, KOREA

<sup>2</sup>Advanced Process & Development TEAM, System LSI Division & <sup>3</sup>Technology & Development TEAM,

Samsung Electronics Co., Ltd., San#24, Nongseo-Ri, Kiheung-Eup, Yongin-City, Kyungki-Do, KOREA

Phone:82-2-880-5451(233), Fax:82-2-887-6575, E-mail:isjeon07@snu.ac.kr

## 1. Introduction

With the continued scaling of gate length to the deep sub micron, numerous researches have been focused on high-k dielectric materials as a substitute for SiO2 gate oxide. The candidate gate dielectrics are  $Ta_2O_5$ ,  $Al_2O_3$ ,  $HfO_2$ ,  $ZrO_2$  and Hf, Zr silicates, etc. Among these materials Al<sub>2</sub>O<sub>3</sub> is promising since it shows a low level leakage current density due to larger band-gap although its dielectric constant is rather low. However, there are several issues to overcome for its application as gate dielectric. First, Al2O3 is known to have a large amount of fixed charge density [1-2] resulting in a flat band (V<sub>b</sub>) or threshold voltage shift. Second, it has a large interface state density (D<sub>ii</sub>) compared to SiO2. Therefore, in this study, the variations in Dit and Vib of TiN/Al2O3/Si MOS capacitor with the various annealing conditions were investigated. From this investigation the optimum annealing condition was determined. "Slow" and "fast" interface states were analyzed from the hysteresis measurement of C-V curves and conductance method, respectively.

## 2. Experimental

5.8-nm-thick-Al2O3 film were grown on 8-in-diameter p-type (doping concentration of 4.7×1017/cm3) Si (100) wafer by an atomic layer deposition method at 350 °C using TMA (Trimethyaluminum:Al(CH3)3) and H2O as the precursors. The growth rate of Al2O3 was ~1 Å/cycle. Then, TiN/300-nm-thick Al film stack 25-nm-thick was sputter-deposited as the metal electrode. The MOS capacitors with an active area of 52402µm<sup>2</sup> were patterned using photolithography and reactive ion etching. Post-annealing of the capacitors was performed at temperatures of 300, 375, 450°C, respectively, for 30min under H2/N2=10/90 ambient using a vertical furnace. For more exact comparison, one of the samples was annealed at 450°C for 30min in N2 ambient. The C-V measurement frequency ranged from 1KHz to 100KHz. Table 1 shows the list of annealing conditions and some data from C-V measurements.

## 3. Result and discussion

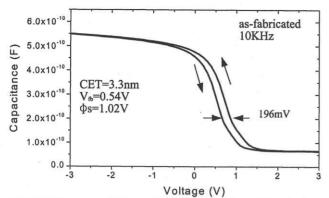

Fig.1 shows the conventional high frequency C-V curve of the as-fabricated sample. The measured capacitance equivalent oxide thickness (CET), from accumulation capacitance is 3.3 nm, and, thus, the dielectric constant of the  $Al_2O_3$  film was estimated to be 6.8, which is a somewhat lower value than the bulk dielectric constant.

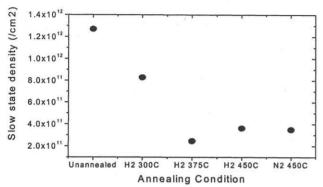

It is known that the hysteresis voltage (V<sub>b</sub>) of C-V curve can be used to estimate the slow interface state density using the following equation:  $N_{si}=C_{ox}V_{b}/q$ , where  $C_{ox}$  is the areal capacitance of insulator layer and q is the electron charge [3]. The slow interface state density of the as-fabricated sample was estimated to be  $1.27 \times 10^{12}/\text{cm}^2$ , which is far higher than that of the SiO<sub>2</sub>/Si interface. It was found that V<sub>b</sub> was reduced with post-annealing temperature regardless of annealing ambient. Fig. 2 shows that the slow interface state density reduced to  $\sim 3 \times 10^{11}/\text{cm}^2$  after the annealing at temperatures above 375 °C.

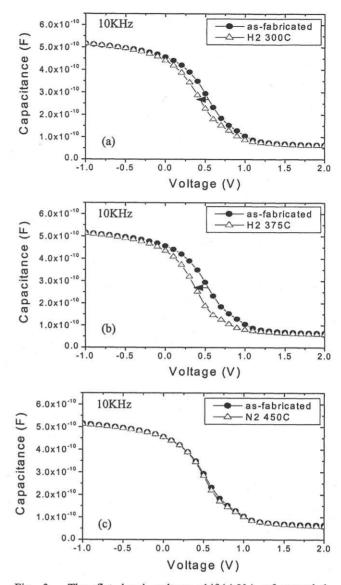

It was reported that ALD-Al2O3 films had a large amount negative fixed charge (Qf) of approximately  $5 \times$  $10^{12}$ /cm<sup>2</sup> and the flat-band voltage shift ( $\triangle V_{fb}$ ) was positive. Because the fixed charge degrades device performance, it is important to understand their properties and thermal behavior with annealing conditions and to reduce their densities for device application. Fig. 3 shows that the H2 annealing was very effective for reducing the fixed charge densities. Due to the decrease in the fixed charge, a negative voltage shift  $(\triangle V_{fb})$  is obtained. The higher annealing temperature resulted in a larger  $\triangle V_{\oplus}$ . However,  $\triangle V_{n}$  was almost zero when the sample was annealed at 450 °C under N<sub>2</sub> atmosphere. This result suggests that there is a chemical reaction between hydrogen and the fixed charges in Al<sub>2</sub>O<sub>3</sub>. The reductions of fixed charge density  $(\triangle N_f)$  are  $6.8 \times 10^{11}$ /cm<sup>2</sup>,  $1.07 \times 10^{12}$ /cm<sup>2</sup>,  $8.5 \times 10^{11}$ /cm<sup>2</sup>, of the samples annealed 300°C(H2), 375°C(H2), 450°C(H2), respectively.

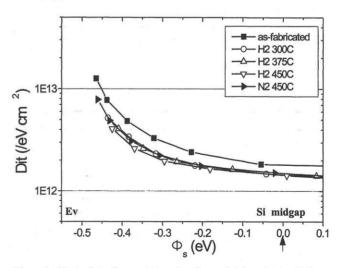

In order to extract fast interface state density (D<sub>it</sub>), conductance of the MOS capacitors were measured as a function of frequency [4]. Fig.4 shows the change in D<sub>it</sub> with annealing conditions. D<sub>it</sub> of the as-fabricated sample was  $1.8 \times 10^{12}$ /eVcm<sup>2</sup> at the Si midgap and  $1.27 \times 10^{13}$ /eVcm<sup>2</sup> near the valence band edge. The D<sub>it</sub> decreases with H<sub>2</sub> and N<sub>2</sub> annealing. However, no difference was observed in the 300~450 °C range. After annealing, the fast interface state density decreased to  $1.4 \times 10^{12}$ /eVcm<sup>2</sup> at the midgap. The capture cross-section ( $\sigma_p$ ) near the midgap is ~6 × 10<sup>-14</sup> cm<sup>2</sup> in the as-fabricated sample which is higher than that of SiO<sub>2</sub>/Si MOS capacitor [5]. This suggests that there are higher possibility for carrier (hole) to collide with the trap centers in TiN/Al<sub>2</sub>O<sub>3</sub>/Si MOS system.

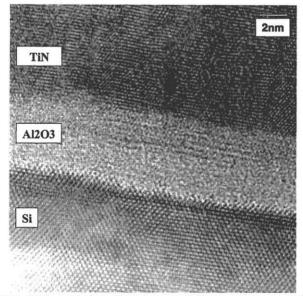

Fig. 5 is a high resolution TEM image of sample annealed 450°C in H<sub>2</sub>. Al<sub>2</sub>O<sub>3</sub>/Si interface is very clear and no interfacial layer is observed. The TiN/Al<sub>2</sub>O<sub>3</sub> interface was a little bit rough which might cause the fast state centers. More detailed study on the fast states generated by metal/Al<sub>2</sub>O<sub>3</sub>(or other oxide materials) system electrode will be necessary.

### 4. Conclusion

The variations in slow/fast interface states of TiN/Al<sub>2</sub>O<sub>3</sub>/Si MOS capacitor as a function of the post-annealing were studied using C-V and conductance method. It was observed that the slow interface states, by fixed charge, were drastically reduced by H<sub>2</sub> annealing at 375 °C for 30min. Fast states were also reduced by the H<sub>2</sub> or N<sub>2</sub> annealing at temperatures higher than 300 °C.

#### 5. Reference

- [1] J.M.Hergenrother, G.D.Wilk, T.Nigam et al, IEDM2002,

- [2] D.G.Park, H.J.Cho et al., J. Appl. Phys.89, 6275(2001)

- [3] Takashi Hori, Gate Dielectric and MOS ULSIs, (1997)

- [4] E.H.Nicollian, J.R.Brews, MOS Phys. and Tech. (1982)

- [5] G. Barbottin, A. Vapaille., Instabilities in Silicon Devices, (1990)

Fig.1 C-V curve of the as-fabricated sample. Hyteresis due to the slow interface states

Fig.2 Slow interface states densities with annealing ondition from C-V measurement

Table I. List of samples:Annealing condition and the results of C-V measurement(10KHz).

| Sample              | Temp.(C) | Ambient                                | V <sub>h</sub> (mV) | $\Delta V_{fb}$ (mV) |

|---------------------|----------|----------------------------------------|---------------------|----------------------|

| as-fabricated       | -        | -                                      | 169                 |                      |

| H <sub>2</sub> 300C | 300℃     | H <sub>2</sub> /N <sub>2</sub> = 10/90 | 128                 | -107                 |

| H <sub>2</sub> 375C | 375℃     |                                        | 36                  | -167                 |

| H <sub>2</sub> 450C | 450℃     |                                        | 56                  | -134                 |

| N <sub>2</sub> 450C | 450℃     | N <sub>2</sub>                         | 54                  | -19                  |

$V_{\hbar}$ : Hysteresis form forward and reward voltage sweep  $\bigtriangleup V_{\hbar}$ : Voltage shift from C-V curves due to the reduction of the fixed charge

Fig.5 High resolution TEM image of the sample annealed at 450  $^\circ C$  in H2. The thick of Al2O3 is 58Å.

Fig. 3 The flat band voltage shift( $\triangle V_{rb}$ ) of annealed samples from the flat band voltage( $V_{rb}$ =0.54V) of as-fabricated sample. The negative voltage shift due to the reduction of negative fixed charge. (a) H<sub>2</sub> 300°C, (b) H<sub>2</sub> 300°C, (c) H<sub>2</sub> 450°C.

Fig. 4 Fast interface state density which obtained by using conductance method.  $\Phi$  s is the surface potential. ( $\phi$  s=0 in Si midgap.)