P3-21

# Room Temperature Formation of Thick SiO<sub>2</sub> Layers by Anodic Oxidation of Porous Silicon

Fan Xinyu<sup>1,3</sup>, Hideo Isshiki<sup>1</sup>, Riichiro Saito<sup>1</sup>, Tadamasa Kimura<sup>1</sup>, Satoshi Yamamoto<sup>2</sup> and Cui Ronggiang<sup>3</sup>

<sup>1</sup>Department of Electronic Engineering, The University of Electro-Communications 1-5-1 Chofugaoka, Chofushi, Tokyo 182-8585, Japan Phone: +81-424-43-5153 Fax: +81-424-43-5152 E-mail: xinyu@tube.ee.uec.ac.jp <sup>2</sup>Electron Device Laboratory, Fujikura Ltd. 5-1 Kiba 1 chome Koto ku Tokyo 135 8512 Japan Phone: +81 3 5606 1030

5-1,Kiba 1-chome, Koto-ku, Tokyo 135-8512, Japan, Phone: +81-3-5606-1030

<sup>3</sup> Department of Applied Physics, Shanghai Jiao Tong University

1954 Hua Shan Road, Shanghai, 200030, P.R.China

# 1. Introduction

The development of a flip-chip type (self-package type) device has been drawn much attention. In the case of flip-chip type devices [1][2], sensor and integrated circuit elements are made in separate processes and are joined with each other in the Z-direction via through-hole interconnections. To form through-hole interconnections through a silicon wafer (silicon interposer), it is necessary to develop a process of forming a micrometer thick insulating layer with a sufficiently high breakdown voltage (>~100 V) on the sidewall of the through-holes at low temperatures (< 400°C). Anodic oxidation of silicon is one of the oxidation processes feasible at room temperature, but it proceeds in general only to the depth of several nanometers from the surface, which is too thin to attain a sufficiently high breakdown strength.

This paper describes the formation of thick  $SiO_2$  layers at room temperature by applying anodic oxidation to thick porous layers. Improvement of the breakdown strength was studied by optimizing the porosity and the Si crystalline size of the starting porous Si layers as well as the anodic oxidation conditions at room temperature. It also describes the structural information of the obtained  $SiO_2$  layers from XPS (x-ray photoelectron spectroscopy) measurements.

## 2. Experimental

Porous Si layers were prepared on the <100> surface of boron-doped p-type silicon substrates of  $1-10\Omega$  cm resistivity. The Si substrates were first degreased using a series of acetone, ethanol and water rinses. Then the native oxide was removed by etching in 4.2 wt% HF for 1 min. An ohmic back-contact was achieved by vacuum deposition of aluminum followed by annealing at 470°C in Ar. The electrolyte used for the formation of porous silicon layers was a mixture of 1:1 HF (46 wt%)/ethanol (96wt%). Anodic etching was performed in a single-tank Teflon cell in the dark at 40°C under a constant current mode. Various anodic current densities (10 to 100 mA/cm<sup>2</sup>) were used to make porous layers of different porosities/crystalline sizes. The estimate porosity was 60% for  $10\text{mA/cm}^2$  and 65% for  $40\text{mA/cm}^2$ . Anodic oxidation of porous silicon layers was performed in the dark at 40°C in 0.1M HCl, at a constant voltage of  $20\text{V}_{\text{SCE}}$  (the voltage between a sample and a reference Pt electrode) for 30 minutes for all the samples. After anodic oxidation, aluminum dots of 1 mm radius were evaporated on the surface of the oxidized layers. The samples were set on the copper plate and the current vs. voltage characteristics between a front aluminum dot and the back aluminum contact was measured in the dark in a shielded probe station.

# 3. Results and Discussion

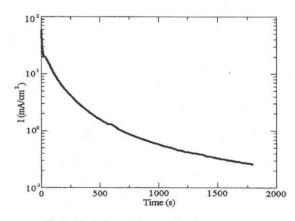

Fig.1. Variation of the anodization current

Porous layers of samples  $1\sim4$  were formed at current densities of  $10\text{mA/cm}^2$ ,  $20\text{mA/cm}^2$ ,  $30\text{mA/cm}^2$  and  $40\text{mA/cm}^2$ , for 260s, 100s, 80s and 65s, respectively, to fix the thickness of the porous layers for  $2-\mu\text{m}$ . Samples  $5\sim7$  were etched at  $100\text{mA/cm}^2$  to the thickness of  $7\mu\text{m}$ ,  $13.5\mu\text{m}$ ,  $27\mu\text{m}$ . Fig.1 shows the change of the anodization current as a function of time during the anodic oxidation of the porous silicon layer (sample 1) at a constant voltage of  $20 \text{ V}_{\text{SCE}}$ . The figure shows that upon oxidation at a fixed potential, the current density decreases rapidly with time. This is

associated with the progress of oxidation. The anodization current decreased more rapidly for the porous Si layers formed at higher current densities, that is, for larger Si crystalline sizes.

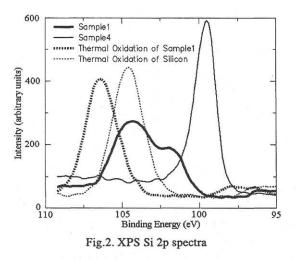

Fig.2 shows the Si 2p XPS spectra of three differently oxidized samples, together with a reference of a thermally oxidized Si crystal surface layer. The measurement was carried out on the surface after the surface was etched with Ar<sup>+</sup> ion beam for 10 minutes. Sample 1 shows a broad spectrum with double peaks. The peak at 104.5eV indicates the presence of SiO<sub>2</sub>, while the other peak at 101.7eV indicates the presence of suboxides  $SiO_x$  (x<2). The latter indicates that the anodic oxidation did not proceed completely into the core of Si crystallites. In comparison, sample 4 shows one large peak at 99.5eV, which indicates that a large amount of unoxidized Si-Si bonds remain. This may be that the crystalline size of sample 4 is too large to be completely oxidized. When sample 1 was subsequently annealed in O<sub>2</sub> at 1100°C for 2 hrs, the SiO<sub>x</sub> and Si-Si bond peaks disappeared and a new peak at 106.4eV appeared. It could be a mixture of Si-F and Si-O bond peaks.

Table I shows the electrical characterization of the seven samples (1~7). The highest breakdown field of 1.9 MV/cm was obtained for samples 1,2 whose porous layers were formed at 10 and 20 mA/cm<sup>2</sup>, respectively. In contrast, the breakdown field was ~1 MV/cm or less when the porous layers were formed at the etching current density of 100mA/cm<sup>2</sup>. The high breakdown strength of samples 1,2 was obtained due to the preparation of the starting porous layers with smaller Si crystallites as a result of the decreased current density for the anodic etching. However, the value of 1.9 MV/cm is still smaller than the value for the thermal oxide (8-10 MV/cm). It means that the oxidation is still incomplete, consistent with the XPS results. In fact, we observed an increase of the breakdown strength by 35% when sample1 was subsequently oxidized in O2 at 1100°C for 2 hrs.

|        | Table I                                                             | Electrical Ch     | naracterization             |                               |

|--------|---------------------------------------------------------------------|-------------------|-----------------------------|-------------------------------|

| Sample | Current<br>Density<br>of Anodic<br>Etching<br>(mA/cm <sup>2</sup> ) | Thickness<br>(µm) | Breakdown<br>Voltage<br>(V) | Breakdown<br>Field<br>(MV/cm) |

| 1      | 10                                                                  | 2                 | 380                         | 1.9                           |

| 2      | 20                                                                  | 2                 | 380                         | 1.9                           |

| 3      | 30                                                                  | 2                 | 310                         | 1.5                           |

| 4      | 40                                                                  | 2                 | 340                         | 1.7                           |

| 5      | 100                                                                 | 7                 | 770                         | 1.1                           |

| 6      | 100                                                                 | 13.5              | 1150                        | 0.8                           |

| 7      | 100                                                                 | 27                | 1300                        | 0.5                           |

The size of the Si crystallites of the porous silicon layers should be small enough for the anodic oxidation to proceed deep inside the Si crystallites [3]. In our experiment, sample1 whose porous layer was formed at the lowest anodic etching current density of 10mA/cm<sup>2</sup> was found to be most highly oxidized from both the XPS spectra and the breakdown strength. We consider that oxide layers with higher breakdown strength can be obtained when we decrease further the anodic etching current density below 10mA/cm<sup>2</sup>. The porosity of the porous layers may also be a key factor to obtain pore-less good oxide layers. It can be controlled by the anodic etching current density and HF concentration. A simple calculation shows that the porosity should be around 55% for the volume expansion due to oxidation to compensate the loss of volume and to allow the formation of a dense and fully oxidized structure. Experiments under more optimized conditions are now in progress.

### 4. Conclusions

Micrometer-thick oxide layers with a breakdown field of ~2 MV/cm were obtained by anodic oxidation of porous layers at room temperature. Formation of fine Si crystallites with a suitable porosity is a key to obtain an oxide layer of good electrical properties. This process can be easily applied to the oxidation of the sidewall of silicon through-holes at room temperature.

#### Acknowledgements

The authors thank Dr. H. Yasuhara of Fujikura Ltd. for a fruitful discussion and support of the research.

### References

- A. Satoh, Proc. 3rd International Micromachine Symposium, 1997 p. 163.

- [2] A. Satoh, T. Suzuki and H. Hashimoto, Trans. IEE of Japan, 118-E, 393 (1998)

- [3] A. Bsiesy, et al., J. Electrochem. Soc., 138, 3455 (1991).