# Fabrication and characterization of a single electron transistor using n<sup>+</sup> GaAs

S. H. Son<sup>1), 2)</sup>, B. H. Choi<sup>1), 2)</sup>, K. H. Cho<sup>1)</sup>, Y. M. Park<sup>2)</sup>, Y. J. Park<sup>2)</sup>, S. W. Hwang<sup>1), 3)</sup> and D. Ahn<sup>3)</sup>

<sup>1)</sup>Dept. of Electronic & Computer Engineering, Korea University, Sungbuk, Anam, Seoul 136-075, Korea

Phone: +82-2-927-6114 Fax: +82-2-927-6114 E-mail: swhwang@korea.ac.kr

<sup>2)</sup>Semiconductor Materials Lab. Nano Device Research Center, Korea Institute of Science and Technology,

P. O. Box 131, Cheongryang, Seoul 130-650, Korea

<sup>3)</sup>Institute of Quantum Information and Processing Systems, University of Seoul

Dongdaemun, Jeonnong, Seoul 130-743, Korea

## 1. Introduction

Single electron transport through semiconductor quantum dots is intensively investigated due to its interesting physics and potential applications [1]. However, most of the quantum dots (QDs) using compound materials have been fabricated by the split gate technique [2]. In this paper, we report the fabrication and the characterization of a single electron transistor (SET) made from a thin layer of  $n^+$  GaAs. Clear Coulomb oscillations and Coulomb staircases are observed and the data are consistent with the lithographic dimension of the dot.

## 2. Experiment

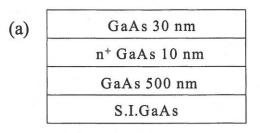

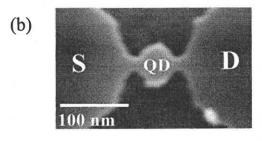

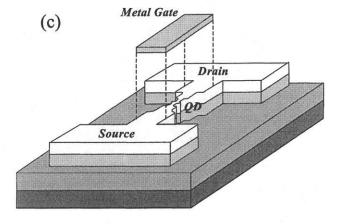

Figure 1 (a) shows the schematic diagram of the wafer grown in a molecular beam epitaxy system. A 0.5  $\mu$ m thick GaAs buffer layer, a 10 nm n<sup>+</sup> GaAs channel layer with the doping density of  $3 \times 10^{18}$  cm<sup>-3</sup>, and a 30 nm GaAs cap layer were grown on a semi-insulating GaAs substrate. We used electron beam lithography and simple wet etching process to fabricate the QD and the tunnel barriers. Figure 1 (b) shows the scanning electron microscope (SEM) image of the active region. After the formation of active region we evaporated the Ti/Au gate on top of the active region for potential control of the QD. Figure 1 (c) shows the schematic of the fabricated final device structure.

#### 3. Result and Discussion

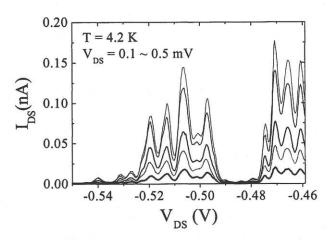

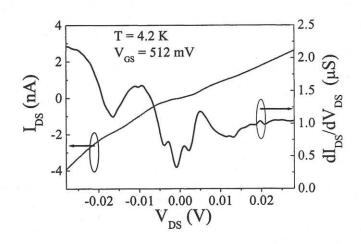

Figure 2 shows a typical result of the drain current control gate voltage (I<sub>DS</sub>-V<sub>CG</sub>) characteristics measured at 4.2 K. The value of the drain-source bias (V<sub>DS</sub>) changes from 0.1 mV to 0.5 mV with 100 µV steps. There are clear Coulomb oscillations and they beat with two different periods (4.5 and 41 mV). Most probably, there will be an unintentional dot in the channel layer mainly due to random distribution of dopants, which often occurred in highly doped channel layers [3]. Figure 3 shows the 4.2 K IDS-VDS and the differential conductance  $(dI_{DS} / dV_{DS})$ -V<sub>DS</sub> curves at V<sub>GS</sub> = - 512 mV. Clear Coulomb staircases can be seen both in the IDS-VDS and in the  $dI_{DS}/dV_{DS} - V_{DS}$  curves. Small staircases in the middle of the staircase are probably caused by the unintentional dot. Figure 4 shows the Coulomb

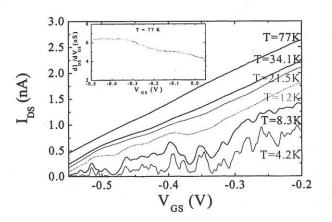

oscillations measured in the range 4.2 < T < 77 K. The oscillations with the large period (41 mV) are clearly seen at T < 10 K and they persist up to 77 K. The observed periodicity and the T dependence are consistent with the diameter with the fabricated dot. From the larger oscillation period observed in Fig. 2 ( $\Delta V_{GS} = 41$ mV), the gate capacitance  $(C_G)$  between the gate and the dot is estimated to be 3.9 aF. From the Coulomb gap the junction capacitance  $C_D+C_S$  is estimated to be 16.2 aF. Then the total capacitance of the dot ( $C_{\Sigma}$ =  $C_D+C_S+C_G$ ) is 20.1 aF. This leads to a dot diameter of 43.3 nm. This value is consistent with the lithographic dimension of the fabricated dot considering the depletion width of 6.7 nm. From the simple Coulomb blockade model, the charging energy was estimated to be 7.96 meV, which corresponds to the T of 92.2 K.

## 4. Conclusions

This paper reported the fabrication and the characterization of the SET fabricated from a thin layer of  $n^+$  GaAs. We used electron beam lithography and one step wet etching process to obtain the small quantum dot. Clear coulomb oscillations were observed and they persisted up to 77 K. The periodicity and the *T* dependence are consistent with the fabricated dot diameter. There are beatings in the Coulomb oscillations at low *T* and they are explained by the existence of unintentional dots due to random impurity distribution in the  $n^+$  layer.

## Acknowledgments

This work was supported by the Korea Ministry of Science and Technology through Creative Research Initiative Program under contract No. M1-0116-00-0008. The work at Korea University was supported by Brain Korea 21 Project in 2002. The work at KIST was supported by the KRCF Project on the technology for quantum dots – functional devices with contract No. 2N22850 and QSRC program at Dongguk University.

## References

- See, for example, Proceedings of the advanced study Institute on Mesoscopic Electron Transport, KLUWER 1997.

- [2] R. Blick, R. Haug, J. Weis, D. Pfannkuche, K. Klitzing, and K. Eberl, Phys. Rev. B. 53, 7899 (1996).

- [3] P. Hendriks, A. Staring, R. van Welzenis, J. Wolter, W. prost, K. Heime, W. Schiapp, and G. Weimann, Appl. Phys. Lett. 54, 2668 (1989).

Fig. 1 (a) Schematic diagram of the wafer used in this experiment. (b) SEM photo of magnified image of the active region. (c) Schematic of the fabricated final device structure.

Fig 2 The  $I_{DS}$ - $V_{GS}$  characteristics measured at 4.2 K and at several different  $V_{DS}$  Values.

Fig 3 The  $I_{DS}$ - $V_{DS}$  and the  $dI_{DS}/dV_{DS}$ - $V_{DS}$  characteristics at 4.2 K.

Fig 4 Temperature dependence of I<sub>DS</sub> from 4.2 K to 77 K.