# P9-3

# Schottky Source/Drain SOI MOSFET with Shallow Doped-Extension

# Mika NISHISAKA, Sumie MATSUMOTO and Tanemasa ASANO

Center for Microelectronic Systems, Kyushu Institute of Technology 680-4 Kawazu, Iizuka, Fukuoka 820-8502, Japan Phone: +81-948-29-7589, Fax: +81-948-29-7586, E-mail: mika@cms.kyutech.ac.jp

## 1. Introduction

We have proposed the use of the Schottky barrier contacts at the source and drain in SOI MOSFET for nearfuture very-short-channel devices.<sup>1-3</sup>) The device has the advantage of the drain breakdown and the drain induced barrier lowering(DIBL). This is because the potential barrier at the source Schottky contact for majority carrier of body is smaller than that of pn-junction and approximately insensitive to the drain field.

However, the Schottky barrier MOSFETs have a large source resistance caused by the spacer between silicide contact and the inverted channel and by the potential barrier at the source for channel carrier. Moreover, the device acts as an ambipolar device, which is unfavorable for such applications as CMOS. Addition of metal fieldplate has been shown to be effective in reducing the ambipolar characteristic.<sup>4</sup>)

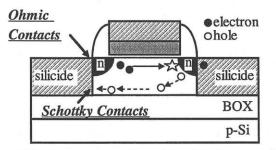

In this work, we report characteristic of the Schottky source/drain SOI MOSFET with shallow doped source and drain extensions (SSD) shown in Fig. 1. The incorporation of SSD reduces the effective potential barrier for transportation of channel carriers, while the effect of the Schottky contact at the source is maintained. Increase in current drive of n-channel SOI MOSFET and suppression of the floating body effect is experimentally demonstrated.

#### 2. Experimental

SOI MOSFETs were fabricated using a self-aligned Co silicide process. The active layer of the SIMOX wafer was p-type, 200 nm in thickness, and 30  $\Omega$ -cm in resistivity. The gate oxide thickness was 12 nm. After gate patterning, extension implantation ( $P^+$ , 25 keV) and spacer formation, a 100 nm-thick Co film was deposited using vacuum evaporation in UHV. The wafer was then annealed in vacuum at 450°C for 30 min to form Co silicide. Unreacted Co on the side walls was removed with nitric acid. For comparison, SOI MOSFETs having conventional n<sup>+</sup>/p junction at the source and drain were also fabricated.

# 3. Switching Characteristic

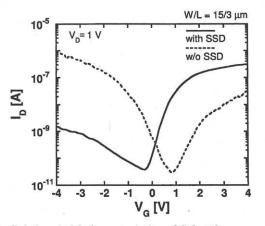

Figure 2 show the subthreshold characteristic of the Co silicide Schottky source/drain MOSFET with and without SSD. The channel length of the MOSFET tested was 3  $\mu$ m. In case of Schottky S/D without SSD, a typical ambipolar operation is observed. In the n-channel operation (positive gate bias), however, the subthreshold slope is small and the drain current contains large noise. In the p-channel operation (negative gate bias), drain current (in other words, leakage current for n-channel operation) flows and is larger than the current in the n-channel operation. On the contrary, the Schottky MOSFET that has n-SSD steeply turns on when the gate is positively

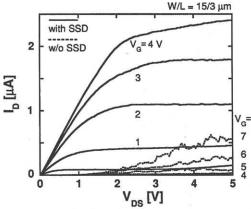

biased and leakage current under negative gate bias is remarkably reduced. Drain characteristics of these devices shown in Fig. 3 show the source resistance is reduced and that the current drive in n-channel operation can be remarkably increased by introducing the SSD into Schottky SOI MOSFET.

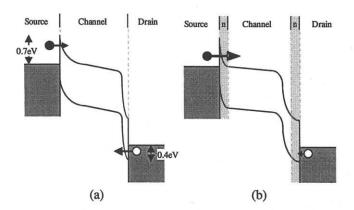

From the measured Schottky barrier height  $\Phi_B$  = 0.70 eV of Co-silicide/n-type-Si, we can draw the band diagrams of n-channel operation Schottky MOSFET as shown in Fig. 4. For the Schottky S/D without SSD structure (Fig. 4(a)), the field emission of electrons from the source dominates because of the relatively high (0.7)eV) potential barrier between the source and channel. In addition a distance of the spacer is present between the contact and the channel. Therefore the current drive is very much reduced. At the reverse-biased drain contact, the holes can flow into the body through the relatively low (0.4 eV) barrier, causing the leakage current. For the device with SSD structures, the tunneling Ohmic contact forms between the source contact and the SSD and, therefore, effective potential barrier at the source is reduced. Moreover, at the drain, the hole injection from the drain contact is reduced because the high field is induced not at the Schottky contact but at the junction between the SSD and the body.

#### 4. Lateral Bipolar Action

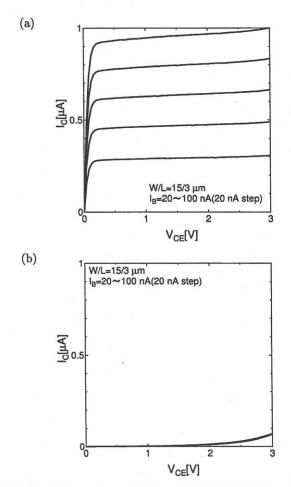

We also fabricated SOI MOSFETs of these Schottky S/D that have p<sup>+</sup>-body contact. In order to investigate the effect of Schottky contacts on the floating body effect, lateral bipolar characteristics of these devices have been examined. Figures 5(a) and 5(b) show the output characteristics of the conventional pn-junction SOI MOS-FET and Co-silicide Schottky SOI MOSFET when they are operated as a bipolar transistor using the body as the base. The pn-junction MOSFET operates as a bipolar transistor with the current gain  $h_{FE}$  of about 8. On the contrary, the Schottky SOI MOSFET with SSD does not show bipolar action. In case of Schottky device, a fixed barrier height exists between the source (emitter) and the body (base). It interrupts the injection of electrons from emitter to base, while the back injection of holes is enhanced. Thus, the Schottky S/D, even with SSD, is effective in reducing the floating body effect .

### 5. Conclusion

Incorporation of shallow extensions into Schottky source and drain SOI MOSFET can increase the current drive owing to reduction of the series resistance, and can decrease the leakage current owing to the reduced field at the drain Schottky contact, while it maintains the effect of suppressing the floating body effect owing to the Schottky contact at the source. Similar effects can be expected in p-channel devices.

## Acknowledgements

This work was partially supported by Special Coordination Funds for Promoting Science and Technology of the Ministry of Education, Culture, Sports, Science and Technology of Japan.

## References

1) M. Nishisaka and T. Asano, Jpn. J. Appl. Phys. 37(1998) 1295.

- 2) M. Nishisaka, et al., Device Research Conf. Dig., p. 74(1998).

- 3) G. Nakagawa, et al., Proc. Int. Display Workshops, p. 43(2001).

- 4) K. Yeh, et al., SSDM Ext. Abst., p. 278(2001).

Fig. 1: Schematic cross-section of a Schottky source/drain SOI MOSFET with SSD structures.

Fig. 2: Subthreshold characteristics of Schottky source/drain SOI MOSFET with SSD (solid line) and without SSD (dashed line).

Fig. 3: Drain characteristics of Schottky SOI nMOSFET with SSD (solid line) and without SSD (dashed line).

Fig. 4: Band diagrams for n-channel operation of Co-silicide Schottky source/drain SOI MOSFET. (a) without SSD. (b) with SSD.

Fig. 5: Output characteristics of SOI MOSFETs when they are operated as bipolar transistor using the body contact as the base electrode. (a)pn-juction SOI MOSFET. (b) Co-silicide Schottky SOI MOSFET.