## Influence of Carrier Velocity Related Parameters on the Propagation Delay Time of CMIS Inverters with High-k Gate Dielectrics

Mizuki Ono and Akira Nishiyama

Advanced LSI Technology Laboratory, Corporate R&D Center, Toshiba Corporation 8 Shinsugita-cho, Isogo-ku, Yokohama 235-8522, Japan Phone: +81-45-770-3693, Fax: +81-45-770-3578, E-mail: m-ono@amc.toshiba.co.jp

### Abstract

It has been reported that the mobility ( $\mu_{\text{eff}}$ ) in MISFETs with high-k gate dielectrics is lower than that in the conventional MOSFETs <sup>[1,2]</sup>. We investigated the influence of carrier velocity related parameters (CVRP) on propagation delay time ( $\tau_{pd}$ ) of CMIS inverters. It is shown that  $\tau_{pd}$  is strongly affected by shapes of mobility curves. This is explained by the fact that  $\tau_{pd}$  is strongly affected by  $\mu_{eff}$  in the high effective field (E<sub>eff</sub>) region, around V<sub>G</sub> = V<sub>DD</sub>, and that  $\mu_{eff}$  in the low  $E_{eff}$  region, around  $V_G = V_{TH}$ , and saturation velocity (V<sub>SAT</sub>) have a relatively small influence on  $\tau_{pd}$ . These observations are then explained based on physical considerations.

### . Introduction

The trend toward miniaturization has resulted in gate dielectrics being thinned, and it is estimated that they will soon be 1 nm for 35-nm MOSFETs <sup>[3]</sup>. In order to avoid the drastic leakage current increase that is inherent in SiO<sub>2</sub> gate dielectrics, high-k materials for gate dielectrics are being intensively investigated <sup>[4]</sup>. It has been reported that  $\mu_{\text{eff}}$  in MISFETs with high-k gate dielectrics is lower than that in the conventional MOSFETs <sup>[1,2]</sup>. However, the  $E_{\text{eff}}$ region, in which the influence of  $\mu_{eff}$  on  $\tau_{pd}$  is the maximum, and the importance of the influence of VSAT are not obvious. We therefore investigated the influences of these parameters on  $\tau_{\text{pd}}$  using an in-house circuit simulator with a simplified transistor model and quantified each influence. 2. Model in Simulation

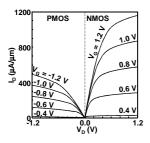

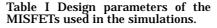

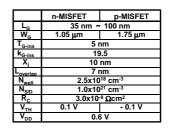

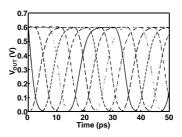

We used a transistor model based on the gradual channel approximation, taking the source/drain resistances into consideration. The effects of drain induced barrier lowering (DIBL), channel length modulation (CLM)<sup>[5-7]</sup>, and velocity overshoot were also taken into consideration. Figure 1 shows the  $I_D$ - $V_D$  characteristics of 50-nm gate length n- and p-MOSFETs with 1.3-nm-thick SiO<sub>2</sub> gate dielectrics. These characteristics agree well with those reported by Y.W.Kim et al <sup>[8]</sup>. Load capacitance was modeled by the sum of the junction capacitance at the bottom of the source/drain and the capacitances between the gate electrode and channel region and the source/drain, in which the Miller effect was region and the source/drain, in which the Miller effect was considered. From the time dependences of the output voltages of CMIS inverters in a 7-stage ring oscillator (Fig. 2),  $\tau_{pd}$  was calculated to be 2.36 ps. Here, the universal curve (UC) <sup>[9]</sup> was used for the mobility. This  $\tau_{pd}$  is used as a reference value ( $\tau_{pd0}$ ). The design parameters for MISFETs in this and the following simulations are summarized in Table I. The influence of  $E_{eff}$  on  $\mu_{eff}$  was modeled by the occuration equation

$$\mu_{\rm eff} = \mu_0 / (1 + \theta (V_{\rm G} + V_{\rm TH}))^{[10,11]},$$

where  $\mu_0$  and  $\theta$  were determined by fitting. Scattering by impurities in the substrate were not taken into consideration. The impurity profile in the channel region was uniform, and its concentration (N<sub>well</sub>) was chosen so that short channel effects were sufficiently suppressed. Virtually, super steep retrograde profiles were assumed. An influence of neglecting scattering by impurities in substrates is quite small, as it will be shown in the section 4. VSAT values were set 8x10<sup>6</sup> and 6x10<sup>6</sup> cm/s for electrons and holes (V<sub>SAT0</sub>), respectively <sup>[7]</sup>. **3. Simulations for High-k Gate Dielectric MISFETs**

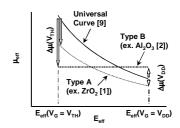

The mobility curves in the literature can be broadly classified into 2 groups (Fig. 3). Those in the first group are approximately equivalent to UC multiplied by a number less than 1 (type A), examples of which include the curves for  $ZrO_2/Si$  systems <sup>[1]</sup>. Those in the other group are almost independent of  $E_{eff}$  (type B), examples of which include the curves for in Al<sub>2</sub>O<sub>3</sub>/Si systems <sup>[2]</sup>. As for the other parameters, the values mentioned above were used. The results of a MISFET of  $L_G = 35$  nm are summarized in Table II, which shows that  $\tau_{pd}$  increases whenever  $\mu_{eff}$  is degraded in the case of type A. In contrast, in the case of type B,  $\tau_{pd}$  decreases for  $\Delta\mu(V_{TH})$  = -30% or lower (not shown) in spite of the decrease in  $\mu(V_{TH})$ . This fact shows that  $\tau_{\text{pd}}$  decreases when the amount of the decrease in  $\mu(V_{TH})$  and the increase in  $\mu(V_{DD})$  is comparable.  $\tau_{pd}$  increases for  $\Delta\mu(V_{TH}) = -40\%$ , however the amount of increase is quite small although the decrease in  $\mu(V_{TH})$  is larger than the increase in  $\mu(V_{DD})$ .

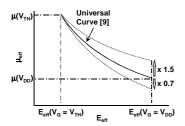

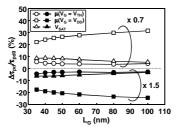

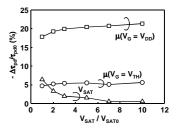

4. Influences of Carrier Velocity Related Parameters on  $\tau_{pd}$ The  $\mu_{eff}$  values at  $V_G = V_{TH} (\mu(V_{TH}))$  and  $V_{DD} (\mu(V_{DD}))$  were changed to 0.7 or 1.5 times of the UC value and  $\mu_{eff}(E_{eff})$ curves were generated tuning  $\mu_0$  and  $\theta$  in (1) (Fig. 4).  $V_{SAT}$  was also changed to 0.7 or 1.5 times the reference value. In each simulation, only one of these 3 parameters was changed. Figure 5 shows the  $L_G$  dependence of the change in  $\tau_{pd}$  induced by the changes of CVRP. It can be seen that the influence of  $\mu(V_{DD})$  is the largest and that those of  $\mu(V_{TH})$  and  $V_{SAT}$  are small. This is the reason for a decrease in  $\tau_{pd}$  in the case of type B in spite of decrease in  $\mu(V_{TH}).$  It can also be seen that as L<sub>G</sub> decreases, the influence of  $\mu(V_{DD})$  decreases while those of V<sub>SAT</sub> and  $\mu(V_{TH})$  increase. Simulations changing other design parameters, such as  $X_j$ ,  $L_{overlap}$ ,  $R_{S/D}$ ,  $T_{G-ins}$ , and  $V_{DD}$ , were also carried out and qualitatively equivalent results were obtained.

In order to study the effects of velocity overshoot, V<sub>SAT</sub> was increased in the calculations of  $\tau_{pdo}$ . The dependence of decrement in  $\tau_{pd}$  for an inverter with  $L_G=35$  nm on  $V_{SAT}$  in  $\tau_{pd0}$  calculation are shown in Fig. 6, which is induced by increasing CVRP to 1.5 times those in  $\tau_{pd0}$  calculations. It can be seen that the influences of  $\mu(V_{TH})$  and  $V_{SAT}$  are small for all the V<sub>SAT</sub> values studied and that the influence of  $\mu(V_{DD})$  is further increased by the velocity overshoot. However, the effect of velocity overshoot is not large. 5. Discussion

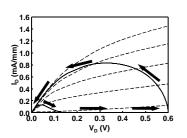

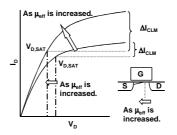

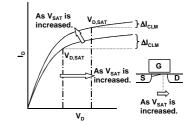

Figure 7 shows the current trajectory of an n-MISFET in the ring oscillator. It can be seen that only a small portion of the trajectory passes through the region where both  $V_G$ and  $V_D$  are low. Hence the influence of  $\mu(V_{TH})$  on  $\tau_{pd}$  is small. It can also be seen that a large portion of the trajectory passes through the region where the device operates in a saturation region. Hence, the influence of  $V_{SAT}$  appears to be the largest. However, this is not correct. When  $\mu_{eff}$  is increased, the electric field strength, at which carrier velocity is equal to V<sub>SAT</sub> (E<sub>SAT</sub>), decreases. Hence, the drain saturation voltage (V<sub>D,SAT</sub>) also decreases. This means that the increment of I<sub>D</sub> due to CLM ( $\Delta$ I<sub>CLM</sub>) increases, i.e., I<sub>D</sub> increases significantly (Fig. 8(a)). When V<sub>SAT</sub> is increased, E<sub>SAT</sub> and V<sub>D,SAT</sub> increase. This means that  $\Delta$ I<sub>CLM</sub> decreases, i.e., ID increases only slightly (Fig. 8(b)). Hence, the influence of  $\mu_{eff}$  on  $I_D$  is large while that of  $V_{SAT}$  is small, i.e., the influence of  $V_{SAT}$  on  $\tau_{pd}$  is small compared with that of μ(Vdd)

Next, the physical reasons for the L<sub>G</sub> dependences of the influences are considered. As  $L_G$  decreases, the parallel electric field in the channel region increases. This means that the carrier velocity approaches VSAT. Hence, the

influence of  $V_{SAT}$  increases and that of  $\mu_{eff}$  decreases. The influence of  $\mu(V_{TH})$ increases slightly in the short  $L_G$  region due to DIBL, because the phenomenon reduces  $E_{eff}$ . Hence, the degradation of µeff in low Eeff region should also be suppressed. 6. Summary and Conclusion

Our study showed that the influence of mobility in the high effective field region on  $\tau_{pd}$  is quite large. Therefore, improvement of the quality of the between high-k interface gate dielectrics and the substrate is indispensable and an increase in carrier mobility, especially in high effective field region, is also essential.

## Acknowledgements

We would like to thank Dr. K.Matsuzawa for useful discussion and comments.

# References

[1] T.Yamaguchi et al., IEDM Tech. Dig. p.663 (2001)

[2] K.Torii et al., Tech. Dig. VLSI Symp. p.188 (2002)

Fig.1 Simulated ID-VD characteristics of 50-nm gate length n- and p-MOSFETs with 1.3-nm-thick gate SiO<sub>2</sub>.

Fig.4 Schematic figure showing how to generate µeff(Eeff) curves.

Fig.7 Current trajectory in an n-MISFET in a ring oscillator.

- [3] The International Roadmap for Semiconductors 2001.

- [4] G.D.Wilk et al., J. Appl. Phys. 89 p.5243 (2001)

[5] Z.-H.Liu et al., IEEE Trans. ED-40 p.86 (1993)

- [6] M.E.Banna et al., Solid State Elec. 31 p.269 (1988)

- [7] Y.Taur, et al. Cambridge Univ. Press 1998

- [8] Y.W.Kim et al., IEDM Tech. Dig. p.69 (2002)

- [9] S.Takagi et al, IEEE Trans. ED-41 p.2357 (1994)

- [10] Y.Cheng et al., Kluwer Academic Pub. 1999

- [11] K.Chen et al., Solid State Elec. 39 p.1515 (1996)

Fig.2 Time dependence of the voltages of output CMIS inverters in a ring oscillator.

Fig.5 Gate length dependence of changes in  $\tau_{\text{pd}}$  induced by changes in the velocity related parameters.

Fig. 8(a) Schematic figure of the changes when  $\mu_{\text{eff}}$  is increased.

Table II  $\Delta \tau_{pd}$  values for the  $\Delta \mu_{eff}$ values obtained in simulations with mobility curves of type A and type B in Fig. 3.

|                                                  | Δμ(V <sub>TH</sub> ) | Δμ(V <sub>DD</sub> ) | $\Delta \tau_{pd}$ |

|--------------------------------------------------|----------------------|----------------------|--------------------|

| Type A<br>ex. ZrO <sub>2</sub> [1]               | - 10%                | - 10%                | + 7%               |

|                                                  | - 20%                | - 20%                | +17%               |

|                                                  | - 30%                | - 30%                | +28%               |

|                                                  | - 50%                | - 50%                | +65%               |

| Type B<br>ex. Al <sub>2</sub> O <sub>3</sub> [2] | - 30%                | + 36%                | - 8%               |

|                                                  | - 40%                | + 17%                | + 2%               |

|                                                  | - 50%                | - 3%                 | +16%               |

|                                                  | - 70%                | - 42%                | +69%               |

Fig.3 Schematic figure showing the 2 groups of reported mobility for MISFETs with high-k gate dielectrics.

Fig.6 Dependence of the change in  $\tau_{pd}$  on V<sub>SAT</sub> for an inverter with L<sub>G</sub> = 35 nm.

Fig. 8(b) Schematic figure of the changes when V<sub>SAT</sub> is increased.