# High-ĸ /Oxynitride Gate Dielectric - Searching for Serendipitous Materials -

Masahiko Hiratani, Shin-ichi Saito<sup>1</sup>, Yasuhiro Shimamoto<sup>1</sup>, Shimpei Tsujikawa<sup>1</sup>, Yuichi Matsui<sup>1</sup>, Osamu Tonomura<sup>1</sup>, Kazuyoshi Torii<sup>1</sup>, Jiro Yugami<sup>1</sup> and Shinichiro Kimura<sup>1</sup>

Advanced Research Laboratory, Hitachi, Ltd., Hatoyama, Saitama 350-0395, Japan Phone: +81-49-296-6111 E-mail: hiratani@rd.hitachi.co.jp <sup>1</sup>Central Research Laboratory, Hitachi, Ltd., Kokubunji, Tokyo 185-8601, Japan

## 1. Introduction

The development of high- $\kappa$  gate stacks, in which the gate length is less than 50 nm and the thickness is only a few nanometers, is the cutting-edge of material science and nanotechnology. It is particularly critical to integrate transition metal oxides (which need a high-temperature oxidation process) into sophisticated high-density devices. This is because a DRAM capacitor dielectric of Ta<sub>2</sub>O<sub>5</sub> is the only successful application of the metal oxide in the past two decades with the exception of low-density FeRAMs. In this paper, we discuss the approach to developing high- $\kappa$  gate materials.

#### 2. Approach to material selection

## Interface and degraded mobility

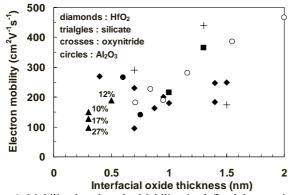

The oxide layer grown between the high- $\kappa$  dielectric and the substrate was less focused on at the beginning of high- $\kappa$  research in 2000 than it is today. This is because the growth of interfacial oxide was regarded as a negative effect for the exclusive purpose of reducing EOT. However, we realized that the interfacial oxide would eventually play a crucial role, similar to the interface of the Ta<sub>2</sub>O<sub>5</sub> capacitor. We benchmarked the reported mobility against the thickness of the interfacial oxide and concluded that 2-nm-thick interface was required to attain electron mobility comparable to that of SiO<sub>2</sub> dielectric [1].

Fig. 1 Mobility benchmark. Mobility is defined by maximum values (solid). Triangles and open symbols denote silicates and our original data, respectively.

The mobility benchmark shown in Fig. 1 has been revised to include data newly reported in 2002 [2,3,6]. (The comparison was made semi-empirically, since the mobility was defined by a maximum value in a plot of mobility vs. electric field irrespective of dopant concentrations.)

Positive correlation is seen independent of what high-k materials were applied.

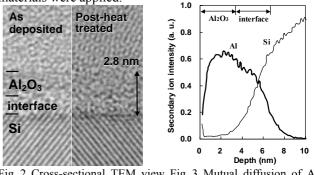

Fig. 2 Cross-sectional TEM view Fig. 3 Mutual diffusion of Al showing mixed interface. and Si at substrate interface.

We do not always adhere to a mechanism of remote-charge scattering due to a fixed charge which we believe to be the origin of the degraded mobility. Dopant diffusion from the substrate, inter-reaction, and local strain cannot be ruled out as multiple origins. In fact, when the post-heat treatment was done at temperatures above  $1000^{\circ}$ C, the Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface became indistinguishable (Fig. 2), and the depth profile showed distinct mutual diffusions across the interface (Fig. 3). We think this mixed interface fluctuates the electric potential in the vicinity of the channel. *Inhomogeneous silicate*

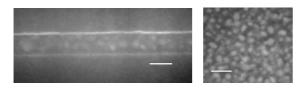

Non-uniform morphology is often seen in silicate dielectrics that are in a glassy state. However, the glass transition is the second-order transition accompanied by kinetics. Therefore, the crucial factors in the process are time and temperature. The quenching process produces a metastable and uniform amorphous dielectric. However, gradual heating and/or cooling relax the glassy film, change the volume, and may precipitate crystalline nano-spheres, because the chemical system is moving towards thermal equilibrium (depending on the chemical composition), especially near the glass transition temperature (800-600°C). The morphology of a  $Hf_{0.15}Si_{0.85}O_2$  film that was deposited by sputtering and then post-heat treated in N<sub>2</sub> is shown in Fig. 4. Spherical particles are clearly visible, because their thickness was as large as 100 nm, and the film was post-heat treated above 1000°C.

The silicate dielectric is liable to phase-separate as the concentration of guest elements is increased. The significantly degraded mobility of silicate dielectrics (triangles) shown in Fig. 1, suggests that the gate dielectric consists of nano spheres dispersed throughout the silicate glass. Taking account of a higher glass transition temperature and namely a stable amorphous state, aluminate is preferable to silicate.

Fig. 4 Phase-separated Hf-silicate dielectric after high-temperature post-heat treatment (SEM photo, scale length = 100 nm).

## Interfacial oxide and gate leakage current

How thick must the interfacial oxide layer be in order to suppress the interfacial reaction and to eliminate the effect on mobility? The chemical potential of oxygen ions is a guideline for estimating the oxide interface. The chemical potential is constant within a uniform oxide, but at the interface adjacent to a non-oxide layer, a concentration gradient, that is, a chemical potential gradient of oxygen ions will result. Therefore, the high- $\kappa$  oxide should be adjacent to a different oxide, in this case the interfacial oxide, in order to minimize the oxygen deficiency at the interface. A typical transition layer between SiO<sub>2</sub> and Si is 0.5 nm thick, which results in a 0.5-to-1.0-nm transition layer, including the interfacial oxide at the high- $\kappa$ /Si interface.

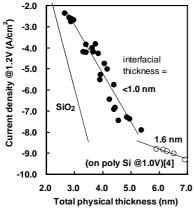

Fig. 5 Gate leakage current plotted against total thickness of high- $\kappa$  dielectric and interfacial oxide.

The first objective of applying a high- $\kappa$  dielectric is to thicken the gate dielectric layer and thus to reduce the gate leakage current. In Fig. 5, the leakage current is plotted against the total physical thickness of the Al<sub>2</sub>O<sub>3</sub> dielectric and the interfacial oxide. Note that the leakage current is higher in the high- $\kappa$  dielectric than in a conventional SiO<sub>2</sub> dielectric with the same total thickness. Decreasing the interfacial thickness from 1.6 to 1.0 nm [4] changes the slope of the thickness dependence and further increases the leakage current. We think that the resulting defective interface lowers the barrier height and increases the leakage current when the interfacial thickness is small. This will be proven if Fowler-Nordheim tunneling through interfacial SiO<sub>2</sub> became predominant, as seen in the Ta<sub>2</sub>O<sub>5</sub> capacitor [5]. The minimum thickness of the interfacial  $SiO_2$  is approximately 1.5 nm while maintaining high mobility and low leakage.

## Nitridation and nitrided interface

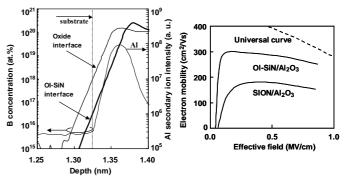

A high-temperature process may crystallize the amorphous film and provide filamentary leakage paths along the grain boundaries. Partially nitrided HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> [6] are thought to be analogous to oxynitride glass, which has glass-transition temperatures and crystallization temperatures higher than those of silicate glasses. Another approach is by surface and/or interface nitridation. We applied an interfacial SiON with an enriched oxygen concentration at the substrate interface (OI-SiN) [7] to the Al<sub>2</sub>O<sub>3</sub> gate stack. The OI-SiN interface suppressed dopant diffusion (Fig. 6) and recovered mobility (Fig. 7). This is likely due to the effect of the increased physical thickness of the interface.

Fig. 6 Suppressed inter-diffusion Fig via oxynitrided interface.

Fig. 7 Mobility recovered in Al<sub>2</sub>O<sub>3</sub>/SiON gate stack.

### 3. Conclusions

If we apply a simple combination of  $Al_2O_3$  dielectric (1.5 nm) and an oxynitrided interface (1.5 nm) to conventional structures, the total thickness of 3.0 nm and EOT of 1.8 nm will enable low stand-by power applications. An alternative would be a nitrided aluminate having a higher  $\kappa$ . The serendipitous materials emerging from the above discussion are simple, although a variety of materials, structures and processes are currently being explored.

#### Acknowledgements

I would like to thank Matty Caymax, Stefan De Gendt and Marc Heyns of IMEC, and Jan Willem Maes of ASM for their collaboration.

#### References

- [1] M. Hiratani et al., Jpn. J. Appl. Phys. 41, 4521 (2002).

- [2] A. L. P. Rotondaro et al., 15-2, VLSI Symp. Tech. (2002).

[3] B. Guillaumot et al., 14-1, B. Tavel et al., 17-1, Y. Morisaki et

al., 34-4, IEDM (2002)

- [4] M. Gutsche et al., IEDM (2001) 18-6.

- [5] H. Miki et al., VLSI Symp. Tech. (1999) T8A-2.

- [6] C. H. Choi et al., 34-3, and C. S. Kang et al., 34-5, IEDM (2002).

[7] S. Saito et al., VLSI Symp. Tech. (2003) 10B-4.