# Reliability characteristics of an HfO<sub>2</sub>/SiO<sub>2</sub> stack gate dielectric annealed in a deuterium ambient

Hokyung Park, Hyundoek Yang, Hyunjun Sim and Hyunsang Hwang Department of Materials Science and Engineering, Kwangju Institute of Science and Technology, #1, Oryong-dong, Puk-gu, Kwangju 500-712, Korea Phone: +82-62-970-2314 Fax: +82-62-970-2304 E-mail: hwanghs@kjist.ac.kr

## 1. Introduction

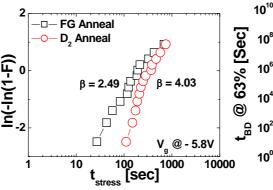

Due to the excess direct tunneling current and reliability limitations of Ultrathin SiO<sub>2</sub>, the development of a high-k gate dielectric is necessary in achieving an effective oxide thickness of less than 1.5nm.[1] One of the major problems in using a High-K gate dielectric is its thickness independent low weibull slope  $\beta(\approx 1-2)$  values. This low weibull slope  $\beta$  values in a high-K oxide are explained by extrinsic factors such as process induced defects. [2,3] In this presentation, we report on the improved reliability characteristics of HfO<sub>2</sub>/SiO<sub>2</sub> stack gate dielectrics annealed in a D<sub>2</sub> ambient. The excellent reliability characteristics of deuterium annealed sample can be explained by the heavier mass effect.[4]

#### 2. Experimentals

After the standard cleaning of a p-type silicon wafer, an approximately 1-nm thick layer of silicon dioxide(SiO<sub>2</sub>) on 8-inch p-type silicon wafer was grown by the rapid thermal processing (RTP) in a pure O<sub>2</sub> ambient. These samples were transferred to an atomic layer deposition (ALD) system where a 12-nm thick Hafnium oxide(HfO<sub>2</sub>) layer was deposited. MOS capacitors with 100nm-thick platinum gate(Pt) electrode were fabricated using a conventional photolithography process. After MOS capacitor fabrication, post metalization annealing(PMA) was performed at 450°C for 30 min in forming gas(4% H<sub>2</sub>). For comparison, D<sub>2</sub> annealing was also performed at 450°C for 30min. The deuterium annealed sample contained deuterium, which was confirmed by time of flight - secondary ion mass spectroscopy (TOF-SIMS) using an 8kV Cs<sup>+</sup> primary ion beam.

## 3. Results & Discussion

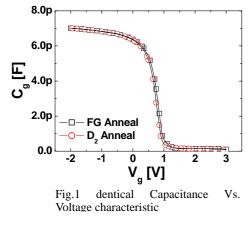

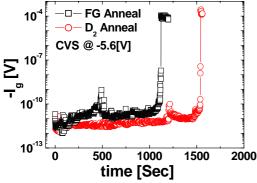

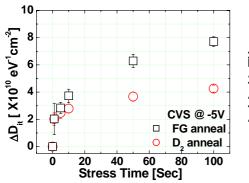

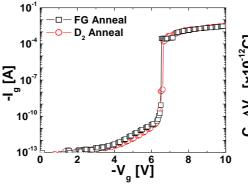

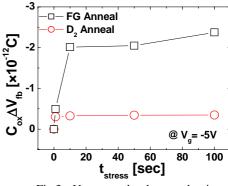

Fig. 1 and 2 show capacitance versus gate voltage (C-V) and current versus gate voltage (I-V) for a MOS capacitor with a HfO<sub>2</sub>(12nm)/SiO<sub>2</sub>(1nm) stack film. The dispersion at various frequencies and hysteresis characteristics were negligible for both samples. Considering the identical I-V and C-V characteristics of both samples, we are able to confirm that the post metalization annealing in a D<sub>2</sub> ambient has no effect on the effective oxide thickness or the barrier height. To evaluate the charge trapping characteristics in the bulk oxide, flatband voltage shift  $(\Delta V_{fb})$  was monitored under a stress gate bias of -5V. Fig. 3 shows net-trapped charge density ( $C_{ox} \times \Delta V_{fb}$ ) versus stress time for both samples. Both samples show a negative flatband voltage shift, indicating a net positive charge generation in the oxide bulk. This positive charge trap can be explained by hydrogen-release at the HfO<sub>2</sub> and SiO<sub>2</sub> interfaces.[5] Fig.4 shows the typical breakdown behavior of HfO<sub>2</sub>(12nm)/SiO<sub>2</sub>(1nm) stack, reduced soft breakdown characteristics are shown in deuterium annealed sample. Because of the heavy mass of

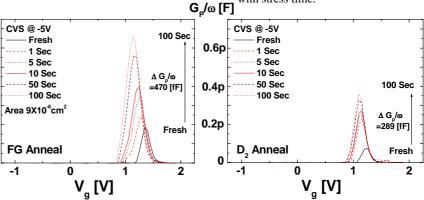

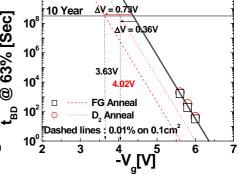

deuterium, sample annealed in a D<sub>2</sub> ambient show less charge trapping characteristics and reduced soft breakdown characteristics. The generation of interface state density( $\Delta D_{it}$ ) was monitored by a conductance method as shown in Fig.6.[6] Both samples were stressed at a gate bias of -5V. As shown in Fig.5 (a) and (b), the deuterium annealed sample shows a lower conductance loss peak( $G_p/\omega$ ) under the same stress conditions. We confirmed that the D<sub>2</sub> annealed sample shows significantly less interface trap generation under an electrical stress. The reduced charge trapping and interface trap generation under the same electrical stress can be attributed to the large deuterium kinetic isotope effect.[4] Fig. 7 shows a weibull plot of time-to-breakdown (t<sub>BD</sub>) at a stress bias of -5.8V. Table 1 shows the weibull slope  $(\beta)$  and time-to-breakdown (t<sub>BD</sub> @ 63%) for various stress bias conditions. From the table, the weibull slope for the deuterium annealed sample is approximately 80% higher than that of the control sample. The improvement in the weibull slope for the deuterium annealed sample can be explained by a decrease in hydrogen-induced defects and neutral traps.[5] We estimated the time-to-breakdown(t<sub>BD</sub>) as a function of the gate voltage as shown in Fig.8. The solid lines correspond to 63% failure values, as measured at an area of 9x10<sup>-6</sup>cm<sup>2</sup>. In addition, the dashed lines estimate the  $t_{BD}$  for a device area of 0.01% and a cumulative failure probability of 0.01%. Due to the higher weibull slope, the deuterium annealed sample shows a significant improvement in device lifetime and operating bias voltage.

### 4. Summary

The effect of  $D_2$  post-metal annealing on the reliability characteristics of  $HfO_2/SiO_2$  stack films was investigated. Compared with a forming gas annealed sample, the  $HfO_2/SiO_2$  stack film that was annealed in a  $D_2$  ambient exhibit excellent reliability characteristics such as less charge trapping, less generation of interface states density, and improved weibull slopes. By employing deuterium annealing, it is possible to the operating bias up to 0.4V on 0.1cm<sup>2</sup> and 0.01% without any degrading device reliability. This improvement can be attributed to a large deuterium kinetic isotope effect.

## Acknowledgments

This work was supported by system IC 2010 project.

#### References

- [1] G. Wilk et al., J. Appl. Phys, 89, 5243 (2001)

- [2] R. Degreave et al., MRS Bulletin, 222 (2002)

- [3] T. Kauerauf et al., Electron. Device Lett., 23, 215 (2002)

- [4] K. Hess, Trans. Electron devices, 45, 406 (1998)

- [5] M. Houssa et al., Appl. Phys. Lett., 79, 3134 (2001)

- [6] E. H. Nicollian, and J. R. Brews, "MOS physics and

- Technology," John Wiley & Sons, New York, 1982

Fig. 4 Typical breakdown characteristics under the constant voltage stress. Reduced soft breakdown behavior is shown in  $D_2$  annealed sample.

Fig. 6 Interface trap density shift( $\Delta D_{it}$ ). The reduced interface trap generation under the same electrical stress is shown in  $D_2$  annealed sample.

Fig.2 Leakage current Vs. gate voltage characteristic

Fig.3 Net-trapped charge density  $(C_{ox} \times \Delta V_{fb})$  characteristics varying with stress time.

Fig. 5 Conductance loss peak( $G_p(\omega)$ ) Vs. gate voltage( $V_g$ ) curve in (a) FG annealed and (b)  $D_2$  annealed samples.  $D_2$  annealed sample shows less interface trap generation than FG annealed sample under same electrical stress.

Fig. 7 Weibull distribution of FG and  $D_2$ annealed samples. Deuterium annealed samples exhibited improved Weibull slope  $\beta$ values.

Fig. 8 10 year life time projection of FG and  $D_2$  annealed samples. Solid lines represent 63% failure on 900  $\mu$ m<sup>2</sup> and dashed lines represent 0.01% failure on 0.1cm<sup>2</sup>.

|                                | $V_{g}$               | -5.6V | -5.8V | -6.0V |

|--------------------------------|-----------------------|-------|-------|-------|

| β<br>(Weibull<br>slope)        | FG Anneal             | 2.76  | 2.49  | 3.24  |

|                                | D <sub>2</sub> Anneal | 5.60  | 4.03  | 5.82  |

| t <sub>BD</sub> @ 63%<br>[Sec] | FG Anneal             | 1673  | 193   | 32    |

|                                | D <sub>2</sub> Anneal | 1977  | 329   | 43    |

Table 1 Weibull slope( $\beta$ ) and time-to-breakdown (t<sub>BD</sub> @ 63%) for various stress bias conditions. The weibull slope of deuterium annealed sample is approximately 80% higher than that of control sample.