# The Effect of Boron and Fluorine Incorporation in SiON Gate Insulator on NBTI

Takaoki Sasaki, Fumio Ootsuka, Hiroji Ozaki, Mitsuhiro Tomikawa Mitsuo Yasuhira and Tsunetoshi Arikado

Semiconductor Leading Edge Technologies Inc. 16-1 Onogawa, Tsukuba, Ibaraki 305-8569 JAPAN

E-mail: sasaki2@selete.co.jp

#### I. Introduction

In order to improve the device performance, thinner gate insulators are required for deep sub-micron MOSFETs. In the situation where a thinner gate insulator is required, nitridation is effective in suppressing boron penetration. Furthermore, a larger physical thickness for thin nitridated oxide insulators is achieved while reducing the equivalent oxide thickness (EOT).

However, the nitrogen used in the nitridation process has a great influence on certain transistor characteristics. In particular, negative bias temperature instability (NBTI) has become more serious for generations less than 130 nm. Generally, it is believed that the electrochemical reaction between interface states and holes triggers NBTI [1, 2] and it has been reported that the degradation of NBTI can be controlled by the interface state density and the fixed charge in the gate insulator [3]. In order to reduce the interface state density, some research deals with the influence of hydrogen and fluorine [1, 4].

In this paper, we report that the relationship between interface state density and NBTI depends on the nitirdation process. Furthermore we have found that fluorine incorporation at the interface reduces NBTI, which shows an adverse effect to nitrogen incorporation in the bulk SiON.

## II. Experiments and Measurements

#### A. Experiments

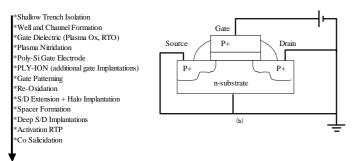

P+MOSFETs were fabricated using a nitridation technology with the process flow shown in Fig.1(a). The gate insulator thickness of P+MOSFETs that had various nitrogen concentrations was around 1.5 nm or 2.0 nm when measured ellipsometrically. In order to evaluate the effect of the boron penetration, boron was doped at the dose of  $1 \times 10^{15}$  to  $1 \times 10^{16}$  cm<sup>-2</sup> to the gate electrode. After patterning the gate electrode, the S/D (source/drain) was implanted with BF<sub>2</sub> or boron and annealed at  $1050^{\circ}$ C. This implantation was performed at the gate electrode simultaneously.

#### **B.** Measurements

Fig.1(b) is a schematic arrangement for NBTI stress. The stress time was 10000 sec, and the stress bias was -10 MV/cm at  $125^{\circ}\text{C}$ . We discuss using a differential value for initial and subsequent stress plotted as Stress Time vs.  $\Delta \text{Vth}$ . Nit (the average interface state density) was measured by the charge pumping method.

#### III. Results and Discussions

# A. Effect of plasma nitridation on NBTI

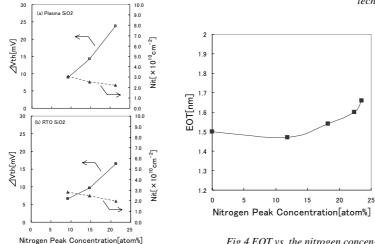

Fig.2 shows the time dependence of NBTI for two types of base  $\mathrm{SiO}_2$  fabrication. Each graph shows the nitrogen incorporation effect on the gate insulator. The gate insulator using the plasma oxidation process has a weaker resistance for NBTI than that using the RTP process. The relationship between Nit measured from the charge pumping technique and  $\Delta V$ th(NBTI after 10000 sec stress) was plotted as a

function of nitrogen incorporation (Fig.3) . Previous studies [5] have reported that the interface state causes a significant degradation of NBT stability. However we observed the decrease in Nit and the enhancement of NBTI for each base  ${\rm SiO}_2$  with increased nitrogen from this figure. It can be expected that the effect of relaxation of the interface occurred at the nitridation process.

Fig.4 shows EOT versus nitrogen peak concentration. We found that a nitrogen incorporation around 10% is effective in reducing EOT. Nitrogen incorporation over 10% showed an increase of EOT for each base SiO<sub>2</sub> film. The relationship between NBTI and Nit suggests that nitrogen incorporation at the interface is not the main reason for the degradation mechanism of NBTI, because NBTI data show a strong dependence of nitrogen concentration in spite of the slight decrease of Nit. We propose that the electrochemical reaction between Si-H and the hole is enhanced by the presence of nitrogen in the bulk SiON.

### **B.** Effect of Fluorine on NBTI

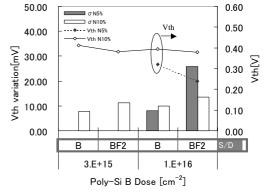

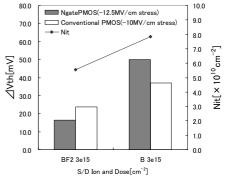

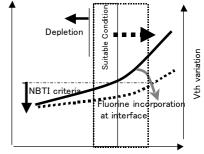

Boron penetration was evaluated for various device fabrications. Fig.5 shows the enhancement of boron penetration for the case of BF, ion impurity. This result is consistent with the previous literature [6]. The SIMS profile (using ion sputtering from the substrate) as shown in Fig.6(b) has detected boron in the substrate slightly. In addition, fluorine exists at the SiON interface region, and the peak concentration is over 1x10<sup>20</sup> cm<sup>-3</sup> for the case of the BF<sub>2</sub> S/D implantation. Fig. 7 shows the effect of BF, implantation to the gate electrode on NBTI and Nit. It has been found that these values are reduced in case of BF, for S/D implantation. Evaluation results of N type gate PMOS in Fig.8 prove the influence of incorporated boron or fluorine. Boron causes a defect in the gate insulator by the diffusion process, and fluorine in the gate electrode enhances the boron diffusion velocity, whereas fluorine reduces the interface defect and NBTI. To optimize gate fabrication of PMOS, it is required to control boron and fluorine from the viewpoint of the interface state. It was found that there is a most suitable relation between the boron dose and fluorine to minimize boron penetration and gate electrode depletion (Fig.9).

#### **IV. Conclusion**

A study of the effects of the boron penetration and fluorine in gate SiON fabrication has been presented. The interface trap generation in the SiON can be significantly decreased by incorporating fluorine at the interface region. However the boron penetration due to the fluorine in the gate electrode was strongly enhanced. From the viewpoint of NBTI and reduction of boron penetration, the most suitable fluorine into the interfacial region can widen the NBTI criteria at a minimized nitrogen quantity.

100 (b) Plasma SiO2 (a) RTO SiO2 Nitride Cond ДVth[mV] 0.1 1000 10000 100000 1000 10000 100000 100 Tstress[sec]

Fig.1 (a) Fabrication process flow (b) Schematic arrangement for NBTI stress: While stress (Tj=125 °C, Vg=-10MV/cm) is being applied

Fig.2 Time dependence of NBTI as a function of the nitridation condition, for RTO SiO<sub>2</sub>(a) and Plasma SiO<sub>2</sub>(b). Plasma nitridation technology was applied for each base SiO2.

1.E+10

Fig.3  $\Delta Vth(NBTI)$  and Nit as a function of the nitrogen concentration for various gate fabrications. (a)Plasma SiO, (b)RTO base SiO, .

Fig.4 EOT vs. the nitrogen concentration (using Plasma SiO<sub>2</sub>)

Fig.5 Relationship between PMOS Vth variation and dose for gate implantation. Additional source / drain deep ion was implanted to the gate electrode simul-

Fig.6 SIMS profile of boron and fluorine (a) Boron was doped for source / drain (b) BF, was implanted.

Fig. 7 Relationship between  $\Delta Vth(NBTI)$  and Nit as a function of boron dose for the gate electrode.(a)Boron was applied to S/D deep region. (b) BF, was implanted. Impurity species for S/D implantation was doped for gate electrode for each.

Fig.8 Comparison of boron with BF<sub>2</sub> for S/D deep region.

state

and Interface

**JBTI**

Gate electrode impurity (Boron)

Fig.9 Model for effect of fluorine and boron in SiON gate dielectric system.

1.E+22

- [1] N. Kimizuka et al., Symposium On VLSI Technology, 2000, p. 92 [2] W. W. Abadeer et al., IEEE Trans. Electron Devices, vol. 42, p. 360, 1995 [3] S.Ogawa, M.Shimaya, N.Shiono, J.Appl.Phys. 77 (3), p. 1137, 1995 [4] C.H. Liu, M.T. Lee, C.Y. Lin, Jpn. J. Appl. Phys. Vol. 41, p. 2423, 2002 [5] M.Terai, T.Yamamoto, K.Watanabe et al., SSDM, Nagoya 2002, p. 752

- [6] T. Aoyama et al., IEEE Trans. Electron Devices, vol. 49,(3), p. 473, 2002