# Selective Dry Etching of HfO<sub>2</sub> in CF<sub>4</sub>, Cl<sub>2</sub> and HBr Based Chemistry

Takeshi Maeda, Hiroyuki Ito, Riichiro Mitsuhashi, Atsushi Horiuchi, Takaaki Kawahara, Akiyoshi Muto, Takaoki Sasaki, Kazuyoshi Torii and Hiroshi Kitajima

> Semiconductor Leading Edge Technologies, Inc. 34 Miyukigaoka, Tsukuba, Ibaraki 305-8501, Japan Phone: +81-29-863-6323, Fax: +81-29-856-3482, E-mail: maeda@selete.co.jp

## 1. Introduction

High-k gate dielectrics have been investigated for low power CMOS applications in the 65 nm technology node and beyond. Among several candidates, HfO2 is being extensively studied because of its modest dielectric constant and thermal stability at the interface with Si [1, 2]. To integrate HfO<sub>2</sub> with conventional CMOS processes, a controllable patterning process of the etch resistant film is essential. In particular, selective etching to remove HfO<sub>2</sub> on SiO<sub>2</sub>/Si is extremely important in order to maintain the controllable formation of shallow junctions. There have been reports of high-k etching using BCl<sub>3</sub>/Cl<sub>2</sub> based plasma [3] or with a combination of oxygen plasma and subsequent DHF treatment [4]. However, the highly selective etch of HfO<sub>2</sub> on SiO<sub>2</sub>, with the damaged layer removable in subsequent wet etch step, has not yet been achieved satisfactorily. In this study, we investigated HfO<sub>2</sub> etching characteristics in conventional Si gate etching chemistries, in which a low SiO<sub>2</sub> etching rate is easily obtained, thus achieving the required HfO2 : SiO2 selectivity. CF4 is expected to reduce HfO<sub>2</sub>, while Hf- chloride or bromide have relatively high vapor pressure, therefore these chemistries are expected to etch HfO2. Moreover, the etchability of dry-etched HfO<sub>2</sub> using a wet treatment was also investigated.

### 2. Experiments

HfO<sub>2</sub> films (3 - 7 nm) were deposited by Atomic Layer Deposition (ALD) onto 1-nm thick SiO<sub>2</sub> interfacial layers formed by In-Situ Steam Generation (ISSG) on 300 mm Si wafers. Films were then annealed at 800°C for 5 s, followed by 150-nm thick poly-Si deposition. After P<sup>+</sup> ion implantation, TEOS masks were fabricated for gate patterning.

Poly-Si gates were etched in a conventional Si etch system with an Inductively Coupled Plasma (ICP) source. HfO<sub>2</sub> films were then etched subsequently in the same chamber with a two-step process (a main etch step (a):  $CF_4$  and an etch completion step (b):  $CI_2/HBr/O_2$  chemistries).

After ashing the etch by-product, samples were spin-etched in dilute HF (DHF).

Film thicknesses were measured using X-ray Fluorescence (XRF) for blanket or ellipsometry for patterned samples. Etch profiles were examined by cross sectional Scanning Electron Microscope (SEM).

### 3. Results and Discussion

Wet etching of previously dry-etched HfO<sub>2</sub>

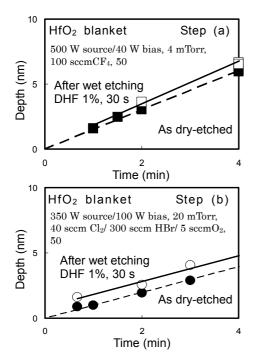

Figure 1 shows the etched depth by dry etching using steps (a) and (b) as a function of time for  $HfO_2$  blanket wafers.  $HfO_2$  etching in  $CF_4$  was assisted by the high ion and/or neutral density in the ICP discharge, even though Hf-fluoride has relatively low vapor pressure. The depths after a subsequent 30 s DHF etch were also plotted. The layer thicknesses removed in the wet etching step were almost independent of dry etch time in the range examined in this study.

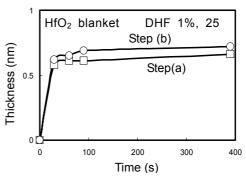

Figure 2 indicates the layer thickness removed in wet etching step as a function of time for  $HfO_2$  blanket wafers which had been subjected to two minutes of a dry etch step of either type (a) or (b). Etching stopped after approximately 2 minutes at about 0.6 nm. These layers may be regarded as the plasma damaged layers remaining after dry etching. The depth of plasma damage under our dry etching conditions is considered to be in the range of several nm [5]. Only highly damaged layers were thought to be etched away in the wet etch step because the damaged layer thickness removed in our experiments was smaller than expected.

### *Etching rate of HfO*<sub>2</sub> *for a patterned sample*

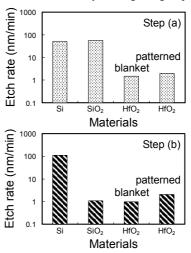

We performed the same experiments for patterned samples as Fig. 1 and defined the etch rate as the slopes of depths after DHF etching. Figure 3 shows the HfO<sub>2</sub> etch rates for step (a) and (b), co-plotted with Si and SiO<sub>2</sub> etch rates. The etch rates for patterned samples were higher than those for blanket samples. The mechanism for this etch rate enhancement is under investigation. Adequate etch rates of 2.0 nm/min were obtained for patterned samples using either etch steps (a) or (b). A selectivity of 1.9 over underlying SiO<sub>2</sub> was obtained for step (b).

### Patterning of poly-Si/HfO2 stacks

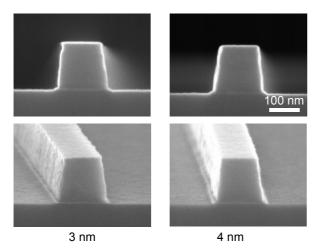

We selected etch step times to permit complete etching of the HfO<sub>2</sub> layers, whilst suppressing both the loss of TEOS mask in step (a) and the formation of the HfO<sub>2</sub> tapered feature at the bottom of the gate in step (b). Moreover, we optimized step (b) to improve the uniformity of etch rate and to suppress HfO<sub>2</sub> tapered feature. Satisfactorily etched surfaces were obtained over a whole 300 mm wafer without any HfO<sub>2</sub> residue nor etch-pitting as shown in Fig. 4. The HfO<sub>2</sub> tapered feature is considered to be caused by side etching of poly-Si gate and/or foot formation by the deposition of etch by-product at the bottom of the gate. It became more pronounced as the  $HfO_2$  etch time was extended. This feature needs further suppression, though the situation would be less serious at the final target thickness of less than 3 nm.

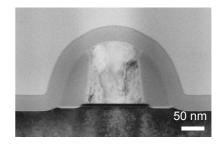

Using the etching process developed in this study, a MOSFET with  $HfO_2$  as gate dielectric was successfully fabricated as shown in Fig. 5.

#### 4. Conclusions

Using  $CF_4$ ,  $Cl_2$ , HBr based chemistries, we obtained an adequate rate of etch and selectivity of 2.0 nm/min and 1.9, respectively. Moreover, it was clarified that the top portion of the highly damaged layer created by HfO<sub>2</sub> dry etch step can be removed by a subsequent wet etching. Based on

Fig. 1 Etched depths by dry etching using step (a) and (b) as a function of dry etching time for HfO<sub>2</sub> blanket wafers. Depths after wet etching are also plotted.

Fig. 4 Etch profiles for 3 nm and 4 nm HfO<sub>2</sub> patterned wafers.

these results, patterning of poly-Si/HfO<sub>2</sub> gate stacks were successfully demonstrated.

#### References

- [1] K. J. Hubbard, D. G. Schlom, J. Mater. Res. 11, 2757 (1996).

- [2] B. H. Lee, L. Kang, W.-J Qi, R. Nieh, Y. Jeon, K. Onishi, and J. C. Lee, Tech. Dig. IEDM '99, 133, 1999.

- [3] K. Pelhos, V. M. Donnelly, A. Kornblit, M. L. Green, R. B. Van Dover, L. Manchanda, Y. Hu, M. Morris, and E. Bower, J. Vac. Sci. Technol. A **19**, 1361 (2001).

- [4] K. L. Saenger, H. F. Okorn-Schmidt, and C. P. D'Emic, Mat. Res. Soc. Symp. Proc. 745, (2003).

- [5] T. Arikado and Y. Horiike, Jpn. J. Appl. Phys. 22, 799 (1983).

Fig. 2 Removed layer thickness in the wet etching step as a function of wet etching time for HfO<sub>2</sub> blanket wafers preceded by two minutes of dry etching using step (a) or (b).

Fig. 3  $HfO_2$  etch rates for step (a) and (b) co-plotted with Si and  $SiO_2$  etch rates.

Fig. 5 Cross sectional TEM image of a MOSFET with 4 nm  $HfO_2$  gate dielectric.