# P-channel Vertical Double-Gate MOSFET Fabrication by Ion-Bombardment-Retarded Etching

Meishoku Masahara, Takashi Matsukawa, Shinichi Hosokawa, Kenichi Ishii, Yongxun Liu, Hisao Tanoue, Kunihiro Sakamoto, Hiromi Yamauchi, Seigo Kanemaru and Eiichi Suzuki Nanoelectronics Research Institute, National Institute of Advanced Industrial Science and Technology (AIST) 1-1-1 Umezono, Tsukuba, Ibaraki 305-8568, Japan, Tel: +81-29-861-3488, E-mail: m.masahara@aist.go.jp

### 1. Introduction

Double-gate (DG) MOSFETs offer great potential in terms of their scalability in nanoscale CMOS technology [1][2]. Among DG MOSFET family, a vertical type has attracted much attention due to its controllability of channel length independently of lithography and its suitability with bulk Si substrates [3,4]. The critical issue is fabrication technology for the ultra-thin vertical channel ensuring DG MOSFET performance.

Recently, we discovered a unique phenomenon that an as-implanted Si substrate is barely etched by a hot TMAH solution which is known as an anisotropic etchant of Si [5]. This newly-discovered process, that is, ion-bombardment -retarded etching (IBRE), can successfully be applied to fabrication of an ultra-thin vertical channel beyond the lithographic limit on a bulk Si substrate. By using the IBRE, actually, we succeeded in fabricating the n-channel vertical DG MOSFET (named "IMOSFET" from its resemblance to the letter "I") with a 15-nm-thick vertical channel [6]. In this paper, we report p-channel IMOSFETs fabricated by using the same IBRE, demonstrating the suitability of the IMOSFETs as a future double-gate CMOS technology.

#### 2. Ion-Bombardment-Retarded Etching (IBRE)

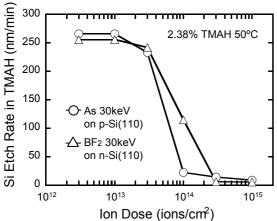

It is well known that the hot TMAH solution etches a Si substrate anisotropically. The etch rate of Si(110) surfaces is significantly higher than that of Si(111). We found that an as-implanted Si substrate is hardly etched independently of the surface orientation. As shown in Fig. 1, the etch rate of a Si(110) substrate in TMAH is markedly decreased at a dose over  $3 \times 10^{13}$  cm<sup>-2</sup> for both As and BF2 implantation. This phenomenon (IBRE) arises from the suppression of the electrochemical reaction between the Si substrate and TMAH solution as a result of the surface amorphization by ion irradiation. Thus, the IBRE is not affected by ion species at all, as can be seen in Fig. 1. This nature is favorable to form both p- and n-channel MOSFETs. By utilizing the IBRE, we can easily form an etch-stopper in/on Si substrates against the hot TMAH.

## **3. IMOSFET Fabrication by IBRE**

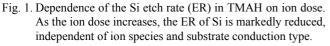

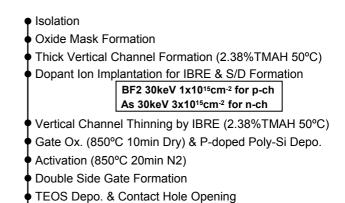

The process flow of the IMOSFET is simple as summarized in Fig. 2. We used a p-type Si(110) wafer with high resistivity of 15  $\Omega$ cm for both p- and n-IMOSFETs. Both the wet etching for a thicker vertical channel (VC) formation and thinning of the VC by the IBRE were performed in 2.38% TMAH at 50°C. 30 keV BF2 ions were used for the VC thinning and S/D formation for p-IMOSFETs, while 30 keV As ions for n-IMOSFETs. Thinning of VC for the vertical channel of IMOSFETs was performed by the IBRE as depicted in Fig. 3. First, keV ions are perpendicularly implanted onto the thicker VC. As a result, ion implantation damages appear only at the top

and bottom regions of the VC, while the side walls remain unexposed. Then the sample is dipped in the hot TMAH solution, where the damaged top and bottom regions of the VC act as etch-stoppers, and the unexposed side walls are horizontally etched by TMAH. The top and bottom regions of the VC, turn into the drain and source automatically after the following oxidation process. Next, 5-nm-thick gate oxide is grown on the (111)-oriented side walls. In-situ P-doped poly-Si is deposited conformally and etched-back by RIE to form double side gates. After TEOS-CVD SiO2 deposition, contact holes are opened self-aligned to the top of the VC. The height and length of the fabricated VC were 160 nm and 24  $\mu$ m, respectively.

## 4. Device Results

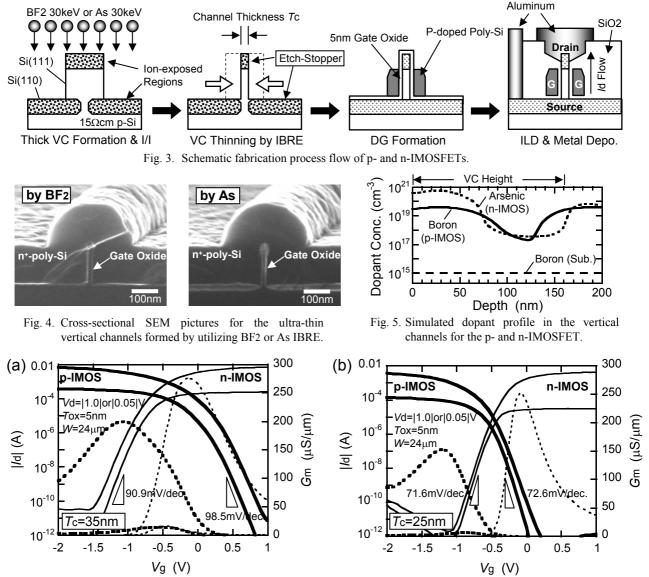

Cross-sectional SEM images of the VCs formed by the BF2 IBRE and As IBRE are shown in Fig. 4. It should be noted that the VC thickness Tc is to be less than 25 nm for both cases. Since no channel engineering was employed, the channel type is estimated to be p-type for p-IMOSFETs and n-type for n-IMOSFETs by the simulation [7] as shown in Fig. 5. It is obvious from Fig. 6 that short channel effects, e.g. Vth lowering, DIBL and increase of s-slope, are dramatically improved for both the p- and n-IMOSFETs with decreasing Tc from 35 to 25 nm. These experimental results precisely demonstrate the unique nature of the DG MOSFET structure. In addition, relatively good current drive is achieved thanks to double channels, even for the case of a thick gate oxide of 5 nm. Further improvement in the current drive can be attained by gate oxide thinning, optimization of dopant profile, and series resistance reduction by salicidation. The inadequate threshold voltage for both the p- and n-IMOSFETs due to the n<sup>+</sup>-poly Si gate can be adjusted by taking advantage of asymmetric n<sup>+</sup>-p<sup>+</sup>-poly Si gate structure [8].

#### 5. Summary

We experimentally demonstrated that the IBRE technology enables us to easily fabricate high performance p-channel vertical DG MOSFETs (p-IMOSFETs) on a bulk Si substrate.

Acknowledgements: We would like to thank Dr. T. Sekigawa, Dr. M. Nagao, Dr. H. Hiroshima and Mr. H. Takashima of AIST. This work was supported in part by the Industrial Technology Research Grant Program in '02 from NEDO of Japan

**Reference:** [1] T. Sekigawa, et al., Solid-State Electron., 27 (1984) 827. [2] H-S. P. Wong, et al., IEDM (1997) 427. [3] C. P. Auth, et al., IEEE-ED 45 (1998) 2381. [4] T. Schulz, et al., IEEE-ED 48 (2001) 1783. [5] M. Masahara, et al., SSDM (2002) 426. [6] M. Masahara, et al., IEDM (2002) 949. [7] ATHENA User's Manual, SILVACO Int'l Inc. 1996. [8] T. Tanaka, et al., IEEE EDL 15 (1994).

- Metallization & PMA

- Fig. 2. Fabrication process flow of IMOSFETs. The processes are the same for p- and n-IMOSFETs, except the dopant ion implantation species.

Fig. 6. Id-Vg (solid line) and Gm-Vg (dotted line) plots of the fabricated p-IMOSFETs (thick line) and n-IMOSFETs (thin line) with (a) Tc=35nm, and (b) Tc=25nm. As the channel thickness Tc decreases, the SCEs, such as Vth lowering, DIBL and increase of s-slope, are successfully improved for both the p- and n-IMOSFET.