# Thermal Instability of Poly-Si Gate Al<sub>2</sub>O<sub>3</sub> MOSFETs

W.S. Kim, T. Kawahara, H. Itoh, H. Horiuchi, A. Muto T. Maeda, R. Mitsuhashi, K. Torii, H. Kitajima

Semiconductor Leading Edge Technologies, Inc. 34 Miyukigaoka, Tsukuba, Ibaraki, 305-8501, Japan Phone: +81-29-863-6315 E-mail: kim6@selete.co.jp

### 1. Introduction

For low standby power and high performance logic applications, high-k gate dielectrics are required as an alternative to  $SiO_2$  or SiON because of their low gate leakage current and higher dielectric constant. But despite of much work, critical issues such as the thermal stability, mobility degradation and reliability still remain unsolved.

It has been reported that an interfacial SiO<sub>2</sub> layer is effective in suppressing the mobility degradation of  $Al_2O_3$  MOSFETs [1]. However, the effects of the stability of SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> on the MOSFET characteristics have not been studied. In this paper, we address the thermal stability of poly-Si gate SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> MOSFETs under high temperature post deposition annealing (PDA) and activation annealing (RTA).

#### 2. Device Fabrication

We have fabricated capacitors and transistors using a poly-Si/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> gate stack. An interfacial 0.9nm-thick SiO<sub>2</sub> (or SiON) layer and an ALD Al<sub>2</sub>O<sub>3</sub> were grown on 300mm wafer with recessed LOCOS. After PDA (O<sub>2</sub> 0.2%), a 150nm a-Si layer was deposited. After gate definition, RTA was applied. Finally H<sub>2</sub> sintering was performed. For transistors, conventional CMOS processes were applied.

#### **3. Results and Discussion**

### PDA temperature dependence: interface instability

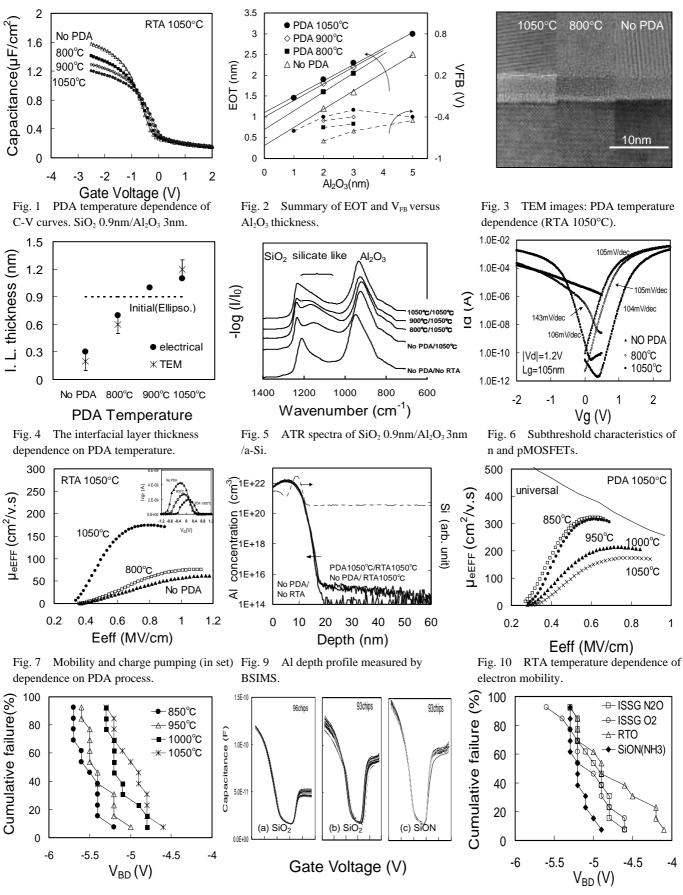

The PDA temperature dependence of the C-V characteristics is shown in Fig. 1. As the PDA temperature decreases, the capacitance increases (Fig. 1). As shown in Fig. 2, the electrical thickness of the interfacial SiO<sub>2</sub> layer decreases in the case of low temperature PDA or when no PDA was carried out. In spite of the fact that the initial SiO<sub>2</sub> thickness was about 0.9nm, the interfacial layer thickness after processing became about 0.3nm for the case in which no PDA was done. The variation in the interfacial layer thickness with PDA temperature was confirmed by TEM (Fig. 3), and good agreement between the electrical and physical thicknesses was obtained (Fig. 4).

The ATR spectra suggest that an Al-silicate layer is formed after RTA and the amount of silicate increases with decreasing PDA temperature (Fig. 5). The process for the formation of silicate is considered to be as follows [2],

| $SiO_2 + Si \rightarrow 2SiO$      | (1) |

|------------------------------------|-----|

| $Al_2O_3 + SiO \rightarrow AlSiOx$ | (2) |

Although a lower EOT is obtained with a low temperature

PDA, the pMOSFET subthreshold characteristic is degraded (Fig. 6). It is believed to be due to the penetration of B from the poly-Si gate to the channel because there is little change of swing in the nMOSFET. Charge pumping measurements indicate the occurrence of defect generation and/or interfacial roughening during reduction of the SiO<sub>2</sub> [3] and Al-silicate formation in case of low temperature PDA, which results in degradation of the mobility (Fig. 7). Al diffusion into the channel was reported to be another cause of mobility degradation [4]; however, it was shown to be not significant in our samples (Fig. 8).

## RTA temperature dependence

Although good mobility (>300cm<sup>2</sup>/V.s) was obtained with high temperature PDA, the mobility was degraded if the RTA temperature was higher than 1000°C (Fig. 9). This is believed to be mainly due to diffusion of dopant into the gate dielectric. The time zero dielectric breakdown (TZDB) characteristics accord with the mobility data (Fig. 10). *Interfacial oxide layer dependence*

The high temperature thermal treatment significantly affects the uniformity of the MOSFET characteristics. With a SiO<sub>2</sub> interfacial layer, there is a large variation in the C-V curves after high temperature PDA/RTA (Fig. 11). A SiON interfacial layer is effective in improving the uniformity of the C-V curves even after a 1050°C PDA/RTA. Similarly, the TZDB characteristics with a SiON interfacial layer are better than those with a SiO<sub>2</sub> interfacial layer (Fig. 12). This indicates that the reliability of the Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> (or SiON) depends on the quality of the interfacial oxide.

## 4. Conclusions

A SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> dielectric stack is found to be unstable under high temperature RTA (1050°C) after poly-Si gate deposition. The PDA temperature should be higher than RTA temperature in order to suppress the reaction at the interface, which severely degrades the MOSFET characteristics. As a result of interfacial oxide degradation by diffusion of dopant, the mobility and reliability of the MOSFET are degraded. We have demonstrated that high mobility and good uniformity can be obtained with a 1050°C PDA and a 950°C RTA on 130nm CMOSFETs.

#### References

- [1] S. Saito, et al., SSDM, 704(2002)

- [2] T.S. Jeon, et al., Appl. Phys. Lett. 78, 368(2001)

- [3] M. Copel, et al., Appl. Phys. Lett. 78, 2670(2001)

- [4] S. Guha, et al., Appl. Phys. Lett. 81, 2956(2002)

Fig. 10 RTA temperature dependence of TZDB (PDA 1050°C).

Fig. 11 C-V curves: (a) PDA 800°C /RTA 850°C, (b)(c) 1050°C PDA/RTA

Fig. 12 Interfacial layer dependence of TZDB.