# Si/SiGe Heterojunction Collector for Low Loss Operation of Carrier Stored Trench-Gate Bipolar Transistor

Tsugutomo Kudoh and Tanemasa Asano

Center for Microelectronic Systems, Kyushu Institute of Technology 680-4 Kawazu, Iizuka, Fukuoka 820-8502, Japan Phone: +81-948-29-7589, Fax: +81-948-29-7586, E-mail: tsugu@cms.kyutech.ac.jp

## 1. Introduction

IGBT (Insulated Gate Bipolar Transistor) is a key device for future power electronics and, therefore, the demand on reducing power-loss and increasing operation frequency is rapidly increasing. Most of the device proposed to improve these characteristics have been modifying the geometrical structure and junction structure inside the device made of Si. We have proposed a new concept of IGBT using SiGe<sup>(1)</sup>. SiGe is used as the collector to suppress the tail-current which is the major cause of the power loss and limits the operation speed of the device. In the previous report<sup>(1)</sup>, we have analyzed the operation of trench IGBT with SiGe collector using device simulation. In this paper, we report, for the first time, experimental results carried out to ascertain the effect of the use of SiGe collector. Effects of SiGe collector are investigated also by analyzing the switching recovery of SiGe/Si heterojunction diode.

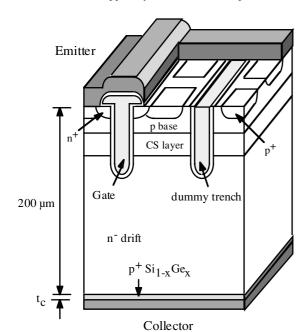

#### 2. Device structure and Operation

The schematic cross-sectional of proposed vertical trench IGBT is shown in Fig. 1. This device fabricated for the experiment has the structure called Carrier Stored Trench-Gate Bipolar Transistor (CSTBT)<sup>(2)</sup>, in which a CS (Carrier Stored) layer was formed to accumulate minority carrier in n<sup>-</sup> drift region under p base of conventional trench IGBT. Although CSTBT was used in the experiment, effects of SiGe collector is not peculiar to CSTBT but applicable to conventional IGBT. The device has a p<sup>+</sup> SiGe collector layer at the backside of the device having the thickness of 200 µm. In the conventional Si IGBT, the p<sup>+</sup> collector layer is made of Si.

The basic concept of the device operation with SiGe collector is as follows: When the device is turned on, holes are injected from the  $p^+$  collector to the n<sup>-</sup> drift region to neutralize the charge of electrons flowed from the n<sup>+</sup> emitter to the n<sup>-</sup> drift region through the n-channel. Therefore, in the turn-off operation, undesirable current flows until the injected holes are completely swept away from the n<sup>-</sup> drift region to the collector or recombines in the n<sup>-</sup> drift region. This causes the switching loss and limits the operation speed of the device. By using SiGe as the p<sup>+</sup> collector, since the barrier for holes flowing out from the n<sup>-</sup> drift region to the p<sup>+</sup> SiGe is lower than that of the Si/Si junction of the conventional IGBT, holes can be quickly swept away<sup>(1)</sup>.

The device was designed to have threshold voltage of about 6.5 V and breakdown voltage of 1200 V. After completing the

top surface process up to Al metallization, the wafer was thined to 200  $\mu$ m. Then SiGe collector was epitaxially grown at the backside of the wafer by using a high-vacuum sputtering system with boron-doped p<sup>+</sup> Si and undoped Ge targets. The substrate temperature during SiGe growth was 550 °C. The composition of SiGe was controlled by adjusting the RF power applied to the sputtering targets. The composition of SiGe and boron concentration in the film were measured with AES and SIMS. The thickness of the SiGe layer was set at the critical thickness<sup>(3)</sup>.

#### 3. Experiment and Results

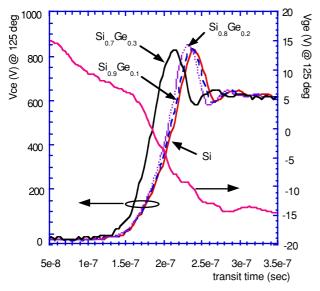

The turn-off waveforms of the proposed SiGe IGBTs and a conventional Si IGBT measured at 125 °C are shown in Fig. 2. The applied collector voltage was 600 V and an inductive load of 1mH was used. We can see that the use of SiGe collector can reduce the turn-off time and the turn-off time decreases with increasing Ge contents in the SiGe collector layer.

It has also been found that the power dissipation is also reduced from 0.947 mJ of Si collector to 0.864 mJ of  $Si_{0.7}Ge_{0.3}$ collector. Thus, the SiGe collector can very much increase the operation speed and reduce the switching power loss.

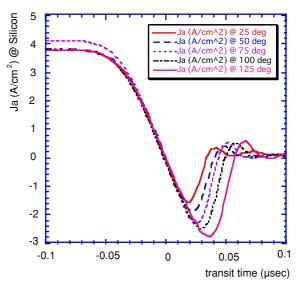

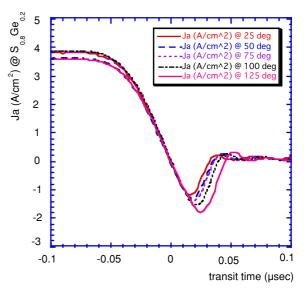

In order to ascertain the effect of the p<sup>+</sup> SiGe collector, p<sup>+</sup> SiGe/n-Si/n<sup>+</sup>-Si heterojunction diodes were fabricated and its reverse recovery was investigated. The reverse recovery characteristics of fabricated Si/Si junction diode and Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si heterojunction diode at 25 °C~125 °C are shown in Fig. 3 and Fig. 4, respectively. Measurements were carried out by inputting  $\pm$  5 V rectangular wave with a frequency of 1.4 MHz. We can see that SiGe/Si heterojunction diode. Table 1 shows the reverse recovery than Si junction diode. Table 1 shows the reverse recovery charge Q<sub>rr</sub>, reverse recovery time t<sub>r</sub> and forward voltage V<sub>f</sub>. The reverse recovery charge Q<sub>rr</sub> of the SiGe diodes is about 1/5 of the Si/Si junction diode. These results demonstrate that the SiGe/Si heterojunction reduces is effective in reducing the turn-off time.

### 4. Conculsion

It has been experimentally shown that the use of SiGe as the collector of trench IGBT is very useful to reduce the turn-off time and switching loss. This can greatly contribute to the development of high-speed and low-loss IGBT. Sputter-deposited epitaxial SiGe can be used for this application.

#### Acknowledgment

The authors gratefully thank Mr. Y. Tomomatsu and Dr. Y. Hagino of Fukuryo Semicon Engineering Corporation for help in CSTBT fabrication and useful discussion. This work was partially supported by Special Coordination Funds for Promoting Science and Technology of the Ministry of Education, Culture, Sports, Science and Technology.

#### References

- T. Kudoh and T. Asano "Si/SiGe heterojunction collector for low loss operation of Trench IGBT", ISTDM'03, pp 95-96

- [2] H. Takahashi, H. Haruguchi, et al "Carrier Stored Trench-Gate Bipolar Transistor (CSTBT) - A Novel Power Device for High Voltage Application-", Proc. of ISPSD'96, pp 349-352

- [3] R. People and J.C. Bean , "Calculation of critical layer thickness versus lattice mismatch for  $\text{Ge}_x \text{Si}_{1-x}/\text{Si}$  strained-layer heterostructures", Appl. Phys. Lett., 47 (1985) p. 322.

Fig. 1 Cross-sectional view of the proposed SiGe CSTBT.

Fig. 2 Experimental turn-off waveforms of SiGe CSTBT at 125 °C.

Fig. 3 Reverse recovery characteristics of fabricated Si/Si junction diode at 25 °C~125 °C.

Fig. 4 Reverse recovery characteristics of fabricated  $Si_{0.8}Ge_{0.9}/Si$  heterojunction diode at 25 °C~125 °C.

Table 1 Device operation paramters obtained from the reverse recovery characteristics of each diode.

| Si/Si junction diode   |        |        |         |  |

|------------------------|--------|--------|---------|--|

| temprature             | 25 deg | 75 deg | 125 deg |  |

| Q <sub>rr</sub> (nC)   | 0.166  | 0.308  | 0.475   |  |

| t <sub>rr</sub> (µsec) | 0.018  | 0.022  | 0.029   |  |

| V <sub>f</sub> (V)     | 1.9    | 2.2    | 1.9     |  |

| Si <sub>0.8</sub> Ge <sub>0.2</sub> /Si heterojunction diode |        |        |         |  |

|--------------------------------------------------------------|--------|--------|---------|--|

| temprature                                                   | 25 deg | 75 deg | 125 deg |  |

| Q <sub>rr</sub> (nC)                                         | 0.117  | 0.148  | 0.235   |  |

| t <sub>rr</sub> (µsec)                                       | 0.016  | 0.018  | 0.022   |  |

| V <sub>f</sub> (V)                                           | 1.92   | 1.98   | 1.82    |  |