# Fabrication of High-Density Wiring Interposer for 10 GHz 3D Packaging Using a Photosensitive Multiblock Copolymerized Polyimide

Katsuya Kikuchi, Shigemasa Segawa<sup>1</sup>, Eun-Sil Jung, Yoshihiko Nemoto<sup>2</sup>, Hiroshi Nakagawa, Kazuhiko Tokoro, and Masahiro Aoyagi

National Institute of Advanced Industrial Science and Technology (AIST)

NeRI, Tsukuba Central 2, 1-1-1 Umezono, Tsukuba, Ibaraki 305-8568, Japan

Phone: +81-29-861-5531 E-mail: k-kikuchi@aist.go.jp

<sup>1</sup>PI Research and Development Co., Ltd.

12-5 Torihama, Kanazawa, Yokohama, Kanagawa 236-0002, Japan

<sup>2</sup>Electronic System Integration Technology Research Development, Association of Super-Advanced Electronics Technologies (ASET)

Room C-B-5, Tsukuba Center Inc., 2-1-7 Sengen, Tsukuba, Ibaraki 305-0047, Japan

## 1. Introduction

By advancement in the operational speed and integration density of LSI chips, high performance computing systems have been realized until now. The clock frequency in a CPU-LSI chip is exceeding the GHz range. However, in order to realize a computing system with a higher performance, it is required performance up of not only components of computing systems but also LSI packagings and interconnects.

Polyimide is one of the most stable organic polymers because it has a glass transition temperature higher than 400 °C. Good electric properties of a high breakdown voltage of more than 1 MV/cm and a low dielectric constant of about 3.0 were already performed. Therefore, polyimide is used in an extensive applications, particularly electronic packaging and LSI passivation layers. However, conventional photosensitive polyimide has the drawback that it must be handled carefully at a temperature lower than 10 °C to avoid an exchange reaction, because the polyimide precursor of polyamic acid is highly unstable.

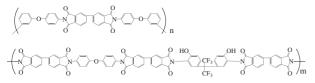

A new photosensitive polyimide is synthesized directly by block copolymerization using a catalyst in solvent at 180 °C. It is possible to synthesize various polyimides of many functional structures by copolymerization [1][2]. A photosensitive material is a diazonaphtoquinone (DNQ) compound. This polyimide has the attractive feature of high temperature thermal curing free, and thus offers the possibility of a low-temperature process. We have reported an interlayer dielectric process for semiconductor LSI circuits with another photosensitive polyimide synthesized using aromatic materials, to provide high thermal resistance [3]. Figure 1 shows the chemical structure of multiblock copolymerized polyimide. This polyimide structure is designed to have a low relative

Fig. 1. Chemical structure of multiblock copolymerized polyimide.

dielectric constant of 2.85 and a low tangent loss of 0.014 at 10 GHz (measured values).

We proposed a strip-line structure using the photosensitive polyimide with the aim of developing a high-density multilayer wiring package for IC packaging [4]. Impedance control can be performed in the strip-line structure to improve the high-speed signal transmission performance.

In this paper, we demonstrate high-density wiring interposer in which the photosensitive multiblock copolymerized polyimide is used as the insulator with the aim of developing a 10 GHz 3D packaging technology. By introducing a new polyimide, high-density wiring interposer with micron-sized transmission line was fabricated.

## 2. Fabrication

We fabricated the high-density wiring interposer using the multilayer structure of the photosensitive polyimide for the 10 GHz 3D packaging. The fabrication process of the interposer is described as follows. The process flow is shown in Fig. 2.

First, a gold groundplane 1 is formed on a silicon substrate using lift-off method (Fig. 2(a)). The photosensitive polyimide layer 1 is spin coated on the substrate, and is pre-baked at 100 °C for the photolithography process (Fig. 2(b)). Then the photosensitive polyimide layer 1 provides insulation between the groundplane 1 and the signal line layer. A g-line and h-line stepper is used to expose the lower via pattern (Fig. 2(c)). After exposure, the polyimide layer 1 developed in an alkaline solution of is N-methyl-2-phyrrolidone, 2-amino-ethanol and purified water (Fig. 2(d)) [5]. The polyimide layer 1 is post-baked at 290 °C. After post-baking, the polyimide layer 1 is treated by the Ar plasma irradiation (Fig. 2(e)). For the Ar plasma treatment, Ar gas pressure was 1.0 Pa, RF power was 1.2 W/cm<sup>2</sup>, and discharge time was 1 min. A signal line photoresist pattern is formed on the polyimide layer 1. The signal line layer is fabricated by the deposition of gold metal film using a lift-off method (Fig. 2(f)). Next, the substrate is spin coated again by photosensitive polyimide to provide insulation between the signal line layer and

Fig. 2. Fabrication process.

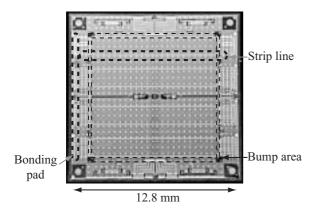

Fig. 3. Photograph of the high-density wiring interposer with micron-sized strip-line structures.

groundplane 2, and is pre-baked at 100 °C (Fig. 2(g)). A g-line and h-line stepper is used to expose the upper via pattern (Fig. 2(h)). After exposure, the polyimide layer 2 is developed and is post-baked at 290 °C and is treated by the Ar plasma irradiation (Fig. 2(i)(j)). Finally, the gold metal layer of groundplane 2 is deposited on the polyimide

layer 2 using a lift-off method (Fig. 2(k)).

Figure 3 shows a photograph of the fabricated high density interposer. A size of this interposer is 12.8-mm square. Bonding pads and strip-line ( $Z_0 = 50 \Omega$ ) structures exist on the chip for GHz signal transmission testing. A width of main strip-lines is 12.5 µm. Widths of other strip-lines are 7.5 µm and 17.5 µm for test pattern. This interposer is capable of a 20-µm-pitched flip-chip connection at the bump area for 3D stacked LSI chips [6]. A size of the 3D stacked chips mounted on the interposer is 10.4-mm square. Thicknesses of gold signal line and gold groundplane 1 and 2 layers are 1 µm, respectively. 20 nm Titanium layer exists under gold layer for a barrier metal layer. In order to realize steady adhesion between the gold metal layer and polyimide layer, a thin Aluminum metal layer and a silane-coupling agent are coated on gold metal layer. The polyimide layer of about 8-µm thickness exists as insulation layer after development.

The micron-sized high-density wiring interposer was successfully fabricated using the photosensitive multiblock copolymerized polyimide as shown in Fig. 3.

# 3. Summary

By optimizing the method of multilayer photosensitive polyimide fabrication, we successfully demonstrated high-density wiring interposer in which the photosensitive multiblock copolymerized polyimide was used as the insulator with the aim of developing the 10 GHz 3D packaging technology. The electrical results of the fabricated interposer will be carry out by the time domain reflectometry (TDR) measurement and the vector impedance measurement.

### Acknowledgements

The authors would like to thank M. Umemoto, M. Shirai, Y. Yamaji, M. Hoshino, T. Matsui, K. Kojima, K. Ito, H. Terao, and K. Takahashi for design of the high-density wiring interposer. They would also like to thank J. Itoh and T. Ohsaki for encouragement and support during the course of this study.

## References

- [1] H. Itatani et al, U. S. P. 5. 502. 143, (1996).

- [2] T. Fukushima, T. Oyama, T. Iijima, M. Tomoi, H. Itatani, J. Polymer Science, Part A, Polymer Chemistry, 39, (2001) p. 3451.

- [3] M. Aoyagi, S. Segawa, E. Jung, T. Itatani, M. Komuro, T. Sakamoto, H. Itatani, M. Miyamura, S. Matsumoto, *Proc. SPIE*, 4345, (2001) p. 1073.

- [4] K. Kikuchi, S. Segawa, E. Jung, H. Nakagawa, K. Tokoro, H. Itatani, M. Aoyagi, Proc. The 6th VLSI Packaging Workshop of Japan, (2002) p. 43.

- [5] E. Jung, S. Segawa, T. Itatani, M. Komuro, H. Itatani, M. Miyamura, S. Matsumoto, M. Aoyagi, *Photopolymer Sci. and Tech.*, 14, (2001) p. 61.

- [6] K. Takahashi, H. Terao, Y. Tomita, Y. Yamaji, M. Hoshino, T. Sato, T. Morifuji, M. Sunohara, M. Bonkohara, *Jpn. J. of Appl. Phys.*, 40, (2001) p. 3032.