# High-Speed III-V HEMT and HBT Devices and Circuits for ETDM Transmission beyond 80 Gbit/s

Ruediger Quay, Michael Schlechtweg, Arnulf Leuther, Manfred Lang, Ulrich Nowotny, Otmar Kappeler, Willi Benz, Manfred Ludwig, Martin Leich, Rachid Driad, Wolfgang Bronner, and Günter Weimann

Fraunhofer Institut für Angewandte Festkörperphysik Tullastrasse 72, D-79108 Freiburg, Germany Phone: +49-(0)761-5159-843 E-mail: ruediger.quay@iaf.fraunhofer.de

#### **1. Introduction**

This work presents an overview of the current status on devices and circuits for electronic time division multiplexing (ETDM) applications with data rates beyond 80 Gbit/s. This paper covers mainly III-V based approaches and highlights the current state-of-the-art, especially with respect to the activities in Europe and with a glimpse on Si(Ge) results.

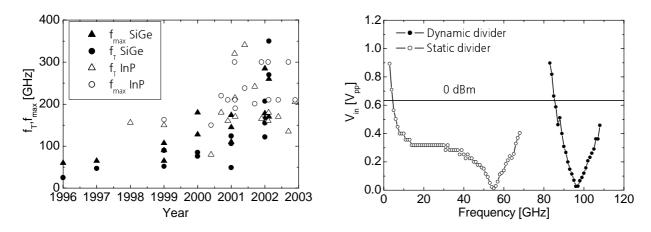

Several device technologies are currently compeeting for high-speed low-power applications at and beyond 80 Gbit/s. These include conventional InP based (D)HBTs [1], InAlAs/InGaAs HEMTs [2], GaAsSb based HBTs [3], and SiGe HBTs [4,5]. Fig. 1 gives an overview of the evolution of the cut-off frequencies of both SiGe and InP HBT technologies over time. It can be seen, that speed levels beyond 300 GHz are within reach by an increasing number of both III-V and SiGe HBT technologies. In Europe, Infineon [5] showed strong activities towards SiGe HBT [5]. Former Opto+, now Alcatel, demonstrated initial results for 80 Gbit/s operation [9].

# 2. Frequency Dividers and Ring Oscillators

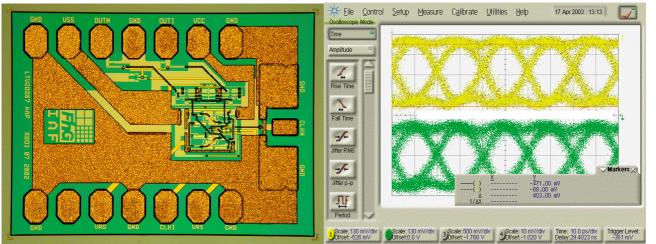

Both HEMT and HBT static dividers have been published suitable for circuit operation at or beyond 100 Gbit/s [6,7]. Fig. 2 gives the input sensitivity curves for a 2:1 static (up to 66 GHz) and a 2:1 dynamic frequency divider in the W-band up to 108 GHz. The chip image of the dynamic divider is given in Fig. 3. The dividers are based on metamorphic InAlAs/InGaAs technology on 4 inch GaAs with a gate lengths of 100 nm similar to the technology in [6]. Recent progress of ring oscillators yields gate delay times of 2.0 ps per stage in InP HBT technology in [8].

# 3. Multiplexers and Demultiplexers

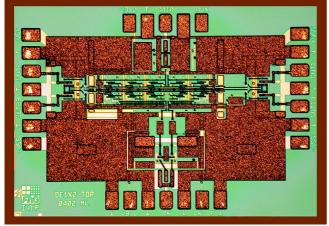

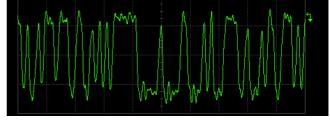

Several selector type multiplexer circuits have been published suitable for >80 Gbit/s operation: In [2], a 100 Gbit/s selector circuit is demonstrated based on InP HEMT technology from NTT. In [9], a similar circuit is given based on InP DHBT technology from Alcatel. Our own HEMT based MUX activities so far yielded on-wafer operation at 70 Gbit/s. Based on recent InP DHBT activities at Fraunhofer IAF, Fig. 4 shows the eye diagram of a 2:1 MUX core at 50 Gbit/. For the receiver side, Fig. 5 gives the chip image of 1:2 demultiplexer based on 100 nm HEMT technology with about 270 active transistors. Fig. 6 gives the output signal of channel 1 of the HEMT demultiplexer at an input signal of 80 Gbit/s.

## 4. Driver Circuits

For applications beyond 80 Gbit/s, both InP HEMT and HBT circuits are currently considered. GaAsSb HBTs [3] promise even more output voltage swing at increased speed beyond 100 GHz. A concise overview of the various activities is given in the full paper.

## 5. Conclusions and Acknowledgements

Despite of the ongoing baisse of the telecom industry, devices and circuits for data rates beyond 80 Gbit/s see strong progress based on both SiGe and III-V semiconductor technologies.

The authors acknowledge the continuous support of the German Ministry of Education and Research (BMBF).

#### References

- [1] Y. Yang, J. Frackoviak, C.T. Liu, C.J. Chen, L.L. Chua, W.J. Sung, A. Tate, J. Tong, R. Reyes, R. Kopf, R. Ruel, D. Werder, V. Houtsma, G. Georgiou, J.S. Weiner, Y. Baeyens, Y.K. Chen, *High-Performance and High-Uniformity InP/InGaAs/InP DHBT Technology for High-Speed Optical Communication Systems, GaAs-IC, (2002)*, pp. 269-272.

- [2] K. Murata, K. Sano, H.Kitabayashi, S. Sugitani, H. Sugahara, T. Enoki, 100-Gbit/s Logic IC Using 0.1-µm-Gate-Length InAlAs/InGaAs/InP HEMTs, IEDM, (2002), pp. 937-939.

- [3] S.S. Yi, S.J. Chung, H. Rohdin, M. Hueschen, D. Bour, N. Moll, D.R. Chamberlin, J. Amano, *Growth and Device Performance of InP/GaAsSb HBTs*, *IPRM*, (2003) pp. 380-383.

- [4] J.S. Rieh, B. Jagannathan, H. Chen, K. Schonenberg, S.J. Jeng, M. Khater, D. Ahlgren, G. Freeman, S. Subbanna, *Performance and Design Considerations for High Speed SiGe HBT of fr/fmax* = 375 GHz/ 210 GHz, *IPRM*, (2003), pp. 374-377.

- [5] J. Böck, H. Schäfer, H. Knapp, D. Zöschg, K. Aufinger, M. Wurzer, S: Boguth, M. Rest, R.Schreiter, R. Stengl, T.F. Meister, *Sub 5 ps SiGe Bipolar Technology, IEDM (2002)*, pp. 763-767.

- [6] M. Lang, A. Leuther, W. Benz, U. Nowotny, O. Kappeler M. Schlechtweg, 66 GHz 2:1 Static Frequency Divider Using 100 nm Metamorphic Enhancement HEMT Technology, Electron. Lett., 38 (14), 2002, pp.716-17.

- [7] M. Mokhtari, C. Fields, R.D. Rajavel, 100+ GHz Static Divide-By-2 Circuit in InP-DHBT Technology, GaAs IC, (2002), pp. 291-293.

- [8] N.K. Srivastava, G. Raghavan, R. Thiagarajah, M.G. Case, E. Arnold, C.W. Pobanz, S.O. Nielsen J.C. Yen, R.A.Johnson, *InP HBT Ring Oscillator with 2.0 ps/stage Gate Delay, GaAs-IC (2002)*, pp. 171-174.

- [9] A. Konczykowska, P. Andre, F. Jorge, J. Godin, *High Quality 80 Gbit/s InP DHBT Selector and its Use for NRZ-RZ Conversion, Electron. Lett.*, 39 (1), 2003, pp.49-51.

Fig. 1: Cut-off frequencies  $f_T$  and  $f_{max}$  over time for SiGe Fig. 2: Input sensitivity of a static and dynamic frequency divider and InP HBTs.

100 nm metamorphic HEMT technology.

of 1.75 mm×1.25 mm based on MHEMT technology.

Fig. 3: 108 GHz 2:1 dynamic frequency divider based on Fig. 4: Eye diagram of a 50 Gbit/s InP DHBT multiplexer core.

based on 100 nm metamorphic HEMT technology.

Fig. 5: Chip image of a 1:2 demultiplexer with a chip area Fig.6: Output signal of channel 1 at 80 Gbit/s input signal of the demultiplexer based on 100 nm MHEMT technology.