# Improvement in Read Endurance of Ferroelectric Gate Field-Effect Transistor Memory with an Intermediate Electrode

Tran Dang Khoa and Susumu Horita

Japan Advanced Institute of Science and Technology (JAIST), 1-1 Asahidai, Tatsunokuchi-machi, Nomi-gun, Ishikawa-ken, 923-1292, Japan. Phone: +81-761-51-1566 E-mail: khoa@jaist.ac.jp

# 1. Introduction

Ferroelectric gate field-effect transistor memory (F-FET) has been widely investigated because of its novel features of non-destructive reading, high operation speed and high packing density. However, F-FET has not been commercialized due to some technological difficulties such as short retention time, high operation voltage and unstable performance. As an attempt to put F-FET into practical, Shimada et al. and Horita et al. proposed a new operation of F-FET with an intermediate electrode between the ferroelectric film and the MOSFET [1]. The memory cell consists of a ferroelectric capacitor C<sub>f</sub> with typical polarization – electric field (P-E) hysteresis loop as in Fig. 1, connected to the gate of a MOSFET, as illustrated in Fig. 2. For data writing, a writing voltage  $V_W$  is applied only to  $C_{f}$ . If the  $C_{f}$  with positive remanent polarization  $P_{r}^{+}$  is positively biased, the ferroelectric capacitance C<sub>fl</sub> is small. If the  $C_f$  with negative remanent polarization  $P_r^{-}$  is positively biased, the ferroelectric capacitance C<sub>fh</sub> is large. Therefore, when a positive reading voltage  $V_R$  is applied to both the Cf and MOSFET, corresponding to the polarization states of C<sub>f</sub>, the intermediate voltage V<sub>I</sub> is different, leading to a different drain current I<sub>D</sub>. By detecting the I<sub>D</sub>, the memory state is decoded.

Fig. 2. Experimental circuit and conditions.

However, the new F-FET encounters a decrease of  $V_I$  during a consecutive reading which may lead to a short read endurance. The origin of the decrease of  $V_I$  was found to be a small leakage current through the writing MOSFET (W-FET) which is connected between the intermediate electrode and the source of the reading MOSFET (R-FET). The W-FET is used as a switch for integration. This configuration is termed source-connected configuration (SCC). To enhance the read endurance, we change one end of the W-FET from the source to the drain of the R-FET. This arrangement is termed drain-connected configuration (DCC). In this conference, we show that the read endurance is much improved with DCC, then the results are analyzed and theoretically verified.

## 2. Theoretical consideration

The V<sub>I</sub> is decreased due to electrons flowing into the intermediate electrode through the W-FET from the source. So, more reading cycles make  $V_I$  decreased and  $V_f$  (the voltage on  $C_f$ ) increased because  $V_R = V_I + V_f = constant$ . This means that the  $C_f$  dependent on  $V_f$ , is varied with reading cycle, in particular, for the P<sub>r</sub> state. On the other hand, when the applied V<sub>R</sub> changes from high to zero at the first reading pulse, the V<sub>I</sub> falls not to zero as normally predicted but to a voltage  $V_p$  [1], in which  $V_f = -V_p \neq 0$ . Also, from the second reading pulse, the V<sub>I</sub> is added by the V<sub>p</sub> regardless of V<sub>R</sub>. The V<sub>p</sub> originates from the polarization domains which do not return to their virgin remanent polarization states once switched by V<sub>R</sub>. Consequently, positive charges are induced in the intermediate electrode and produces Vp.. The non-returning domains may be produced when the  $V_{\rm f}$  during a reading is over the maximum V<sub>f</sub> during the adjacent previous reading. Also, as mentioned above, since the V<sub>f</sub> is increased with the reading cycle, the  $V_p$  is possibly increased with it. Defining  $\Delta V_f$  as the increment of  $V_{\text{f}}$  the increment of  $V_{\text{p}}, \, \Delta V_{\text{p}},$  can be expressed by  $\Delta V_p = k \Delta V_f \Delta C_f (C_f + C_0)^{-1}$  (1), where  $\Delta C_f =$  $C_f(V_f) - C_f(V_f=0)$ ,  $C_0$  is the input capacitance of R-FET and k is the non-returning domain ratio. Also,  $k\Delta V_f \Delta C_f$  is the non-returning domain charge added to Q<sub>I</sub> at the intermediate electrode.

We calculate the time dependent  $V_I(t)$  for the DCC where t is a time from the start of measurement. Because a unipolar reading square pulse voltage  $V_R$  is a superposition of a bipolar square pulse with a square wave function  $S(t)=\pm 1$  as AC part and a DC offset. The  $V_I$  has an AC part,  $V_{IAC}$ , due to AC part of  $V_R$  and a transient term,  $V_{IT}$ , with a time constant  $\tau$  of the circuit. The  $V_{IT}$  consists of three parts. The first one is generated by the DC offset of  $V_R$ , which is decreased exponentially with  $t/\tau$ . The second one is  $V_p$  which is also decreased exponentially with  $t/\tau$  and the third one is from the  $V_D$  bias which increases with  $[1-exp(-t/\tau)]$ . For a linear analysis, the whole range up to the total reading cycle is divided into M regions with linear systems. Within the i<sup>th</sup> region with N<sub>i</sub> reading cycles, the intermediate voltage  $V_{Ii}(t)$  is calculated as the following equation

$$V_{Ii}(t) = V_{IAC} + V_{IT} = 0.5 (V_{I0i} - V_{p(i-1)}) S(t) + V_D + (2) + [0.5 (V_{I0i} - V_{p(i-1)}) + V_{p(i-1)} - V_D] exp[-(t - \sum_{s=1}^{i-1} N_s T) \tau_i^{-1}].$$

In (2),  $V_{I0i}$  is the  $V_I$  at the first reading cycle of the i<sup>th</sup> region. Also,  $\tau_i$  is the time constant given by  $\tau_i = (C_{fi} + C_0)R$  and  $C_{fi}$  is a mean ferroelectric capacitance between  $C_f (V_R = high)$  and  $C_f (V_R = 0)$  at the first reading cycle of the i<sup>th</sup> region. Furthermore,  $V_{p(i-1)}$  is a sum of  $V_I$  at the end of the  $(i-1)^{th}$  region with S(t)=-1 and  $\Delta V_p$  due to  $\Delta V_f$  generated in  $(i-1)^{th}$  region according to (1). The calculation for the SCC can be obtained by setting  $V_D = 0$  in (2).

#### 3. Experimental

The experimental circuit used to investigate the consecutive read endurance is shown in Fig. 2. The  $C_f$  was a 200-nm-thick epitaxial grown PZT film on a Si substrate. Details of preparation of the film can be found in [2]. The R-FET is a self-made MOSFET. To simulate the W-FET in OFF state, a twin diode formed by connecting two identical diodes back to back was used for both the SCC and DCC (the dashed line in Fig. 2). The leakage current of the twin diode was about 1 pA at 1V.

## 4. Experimental results and discussions

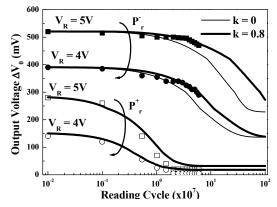

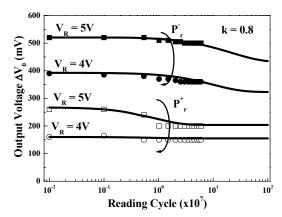

Fig. 3 shows output voltage  $\Delta V_0=I_DR_D$  as a function of reading cycle for the SCC. For the P<sup>-</sup><sub>r</sub> state, the  $\Delta V_0$  starts decreasing with reading cycles of more than  $3.0 \times 10^7$ . For the P<sup>+</sup><sub>r</sub> state, the  $\Delta V_0$  is even decreased faster and finally reached to a saturation of nearly zero. Fig. 4 shows  $\Delta V_0$  as a function of reading cycles for the DCC. Contrary to Fig. 3, for the P<sup>+</sup><sub>r</sub> state,  $\Delta V_0$  is almost constant with the reading cycle up to  $6 \times 10^7$ . For the P<sup>+</sup><sub>r</sub> state, the  $\Delta V_0$  is slightly decreased or unchanged.

To carry out the simulation, the differential capacitance C<sub>f</sub> is to be determined from a corresponding P-V hysteresis loop. For the SCC and DCC, the simulated results are plotted together with the experimental data for a comparison in Figs. 3 and 4 where the bold lines are for k =0.8 and the fine lines are for k = 0. It can be seen that the simulation results are in good agreements with the experimental data for k=0.8, which means that our model is physically acceptable. Also, we can recognize that the non-returning domains contribute to  $\Delta V_0$ . For the SCC, the difference in behavior of  $\Delta V_0$  between the P<sup>-</sup><sub>r</sub> and P<sup>+</sup><sub>r</sub> states can be explained as follows. There are three factors contributing to  $\Delta V_0$ : the non-returning domain charge as origin of the  $\Delta V_p$  in the simulation, the  $C_{\rm f}$  and the time constant  $\tau = (C_f + C_0)R$ . The larger  $\Delta V_0$  in the P<sub>r</sub> state than in the  $P_r^+$  state are attributed to 1)  $C_{fh}$  larger than  $C_{fl}$  and 2) larger  $\Delta V_p$  for the former state. This larger  $\Delta V_p$  is due to larger  $C_{fh}$  which has many ferroelectric domains subject to switching. The slower decrease of  $\Delta V_0$  in the P<sub>r</sub> state than in the P<sup>+</sup><sub>r</sub> state are attributed to 1) larger  $\tau$  and 2) non-zero  $\Delta V_p$  in the former state. The larger  $\tau$  is due to  $C_{fh}$  larger than  $C_{fl}$ , and  $\Delta V_p=0$  in the P<sup>+</sup><sub>r</sub> state is due to  $C_{f\approx}$  const. and  $\Delta C_f=0$ . These discussions are also acceptable for the DCC.

**Fig. 3.** Dependences of  $\Delta V_0$  on reading cycle for SCC.

**Fig. 4.** Dependences of  $\Delta V_0$  on reading cycle for DCC.

According to the simulation, for both cases, the  $\Delta V_0$  finally reaches a saturation value corresponding to a saturation value of  $V_I$ ,  $V_I(t{\rightarrow}\infty){=}C_{f\infty}V_R[2(C_{f\infty}{+}C_0)]{+}V_D$ , where the  $C_{f\infty}$  is  $C_f$  at a saturated  $V_f$ . Because the  $C_{f\infty}$  for the  $P^+_r$  state is different from the one for the  $P^-_r$  state,  $V_I(t{\rightarrow}\infty)$  is also different from each other. Therefore,  $\Delta V_0$  saturates at much higher value for the DCC than for the SCC.

# 5. Conclusions

Physical phenomena and mechanisms of a new F-FET memory operation have been investigated. It is experimentally and theoretically verified that the DCC is a good solution to achieve high read endurance.

#### References

- S. Horita and T.D.Khoa, Jpn. Appl. Phys. 42, 2003, pp. L365-L368.

- [2] S. Horii, S. Yokoyama, T. Kuniya, S. Horita, Jpn. J. Appl. Phys., 39, 2000, pp. 2114-2118.