# Dynamic Thermal Characterization and Modeling of Silicon Bipolar Junction Transistors using Pulsed RF Measurement System

Guo-Wei Huang, An-Sam Peng, Kun-Ming Chen, and Li-Hsin Chang

<sup>1</sup>National Nano Device Laboratories, 1001-1 Ta Hsueh Road, Hsinchu 300, Taiwan Phone: +886-3-5726100 E-mail: gwhuang@ndl.gov.tw

## 1. Introduction

Classical approaches make use of DC and S-parameters measurements in order to obtain I-V and high frequencies chracteristics of the transistors. However, DC measurements suffer from several drawbacks regarding the control of working parameters of the transistor. Especially for field -effect transistors (FETs) steady-state DC characteristics don't provide the correct RF characteristics due to trapping effects. Moreover, with the increasing current density of bipolar junction transistors (BJTs), the rise in junction temperature due to the dissipated power is becoming significant. To overcome these problems, pulsed measurement systems[1,2] were developed to pulse the bias of a device and measure the DC and RF characteristics before trapped charge or junction temperature can change appreciably. In this way, the measured data will not contain the trapping effect and self-heating effect. In this paper, DC and high-frequency characteristics of power Si BJTs with different emitter sizes will be shown based on pulsed DC and pulsed S-parameters measurements.

#### 2. Device Characterization and Modeling

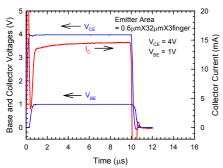

Pulsed DC and pulsed S-parameters measurements were performed using the Agilent 85124A pulsed RF modeling system.[2] The emitter areas of multi-finger Si BJTs under characterization are 0.6µm×32µm×3finger and 0.6µm×16µm×6finger and (0.6µm×16µm×1finger)×6cell. Measurements were made with Cascade microwave probes in the common-emitter mode. These devices were measured on wafer with G-S-G (Ground-Signal-Ground) microwave probes up to 15GHz using standard SOLT calibration procedure. The parasitics associated with the metal pads were removed by measuring both the dummy (metal without device) and the device and subtracting one result from the other in the y-domain. Figure 1 displays the pulsed profile of a BJT. The quiescent biases for base and collector were set to 0, while base and collector pulse biases were 1V and 4V, respectively. The base voltage and collector voltage were kept at constant value in the pulse duration. However, the collector current increases gradually with measured time due to self-heating effect. In the pulsed measurement, the device is allowed to cool down during the off time of the pulse period. So the self-heating effect can be eliminated as current sampled at short measurement delay time ( $\leq 1\mu s$ ). As measurement time is long enough, the current saturates and the value approaches to that at static condition, so the self-heating almost reaches to static-state. To obtain stable signal and reduce the junction heating as low as possible, we choose 1µs as the measurement

delay for isothermal measurement.

In this paper, the VBIC model parameters was extracted similar with Ref.[3] excepts the thermal resistance  $R_{th}$  and the thermal capacitance  $C_{th}$ . In this study,  $R_{th}$  can calculated by following formula :

$$R_{th} = \frac{Y_{22, SH} - Y_{22, noSH}}{D_2(I_C^2 + Y_{22, SH} P)}$$

(1)

where  $Y_{22,SH}$  is the output conductance measured under CW(continuous wave) measurement which includes self-heating effect,  $Y_{22,noSH}$  is the output conductance measured under pulsed mode measurement which includes self-heating effect, P is the power consumption,  $D_2=(\partial I_C/\partial T)/I_C$  can be extracted from Gummel Plot measured under different temperature. Finally,  $C_{th}$  can be calculated based on the shape of collector current (as shown in Fig. 1), here collector current can be expressed as: [4]

$$I_{C}(t) = I_{C,i} + (I_{C,s} - I_{C,i}) \left[ 1 - \exp\left(-\frac{t}{\tau_{th}(I_{C,s}/I_{C,i})}\right) \right]$$

(2)

where  $I_{C,i}$  and  $I_{C,s}$  is the initial value and stable value, respectively.

#### 3. Results and Discussion

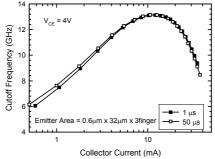

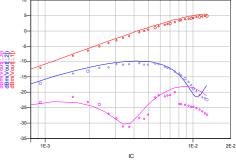

Figure 2 shows the cutoff frequency  $f_T$  of a Si HBT as a function of collector current at different measurement delays. Because of the bandgap narrowing effect in heavily doped emitter region, the bandgap difference  $\Delta E_g$  between emitter and base is negative. Since the current gain is proportional to  $\exp(\Delta E_{s})/kT$ , where k is Boltzman's constant and T is temperature, the higher junction temperature will make a increase of the current gain, As a result, the measured cut-off frequency at 50µs is higher than that at 1µs when the applied current is relatively small. However, the thermal effect reduces the saturation velocity and the critical current at which the Kirk effect takes place [5], the fall-off of the cut-off frequency begins earlier for 50 µs measurement delay. That is the reason measured cut-off frequency at 50 µs is higher than that at 1µs in the high current region. Table 1 summarized the collector current density difference  $\Delta J_{\rm C}$ , the cutoff frequency difference  $\Delta f_T$ , and the maximum oscillation frequency difference  $\Delta f_{max}$  of three different Si BJTs biased at  $V_{CE} = 4V$ ,  $V_{BE} = 1.1V$ between CW and pulsed-mode measurement. It seems that the thermal interaction between fingers makes higher  $\Delta J_{\rm C}$  thus higher junction temperature in devices with more fingers. To reduce the thermal interaction in a multi-finger BJT and thus reduce the saturation velocity and the critical current at which the Kirk effect takes place, we can divide all the emitter

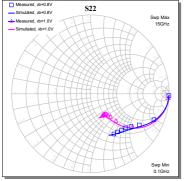

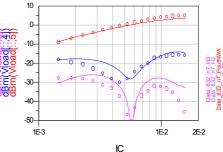

fingers into several sub-cells. As shown in Table 1, transistor with six sub-cells has lowest  $\Delta J_C$ ,  $\Delta f_T$ , and  $\Delta f_{max}$  than those without sub-cells at same emitter area. Table 2 summarized the extracted R<sub>th</sub> and C<sub>th</sub> of three Si BJTs with the same emitter area. Transistor with sub-cells has lower thermal resistance than those without sub-cells. Hence, parallel interconnected sub-cells are preferable to large multi-finger layouts for Si BJTs. Figures 3 and 4 compare the VBIC modelling results of DC and AC data for the Si BJT with emitter area =  $0.6\mu m \times 32\mu m \times 31$  finger. Measurement using ATN LP1 Load-Pull system and HB simulation using Agilent ADS are also adopted for VBIC model validation in linearity analysis and the results are shown in Fig.5 and Fig.6. All the simulation results show very good agreement with the measured data.

### 5. Conclusions

Electrical characteristics of the Si BJTs with different emitter design are shown and discussed based on static and pulsed-mode measurements. Parallel interconnected sub-cells are preferable to large multi-finger layouts for Si BJTs. DC, AC and linearity performance of the Si BJT is also validated using VBIC model and the simulation results shows good agreement with the measured data.

#### References

- J.F. Vidalou, F.Grossier, M. Camiade, J. Obregon, "On-wafer large signal pulsed measurements," IEEE MTT-S Digest, pp.831-834, 1989.

- [2] B. Schaefer, M. Dunn, "Pulsed measurements and modeling for electro-thermal effects" IEEE BCTM, pp. 110-117, 1996.

- [3] G.W. Huang K.M. Chen, J.F. Kuan, Y. M. Deng, S. Y. Wen, D. Y. Chiu, and M.T. Wang, "Silicon BJT Modeling Using VBIC Model", APMC, p.240-243,2001

- [4] P. Palestri, A. Pacelli, and M. Mastrapasqua, IEEE BCTM, p.98-101, 2001.

- [5] D.A. Sunderland and P.L. Dapkus, "Optimizing N-p-n and P-n-p heterojunction bipolar transistors for speed," IEEE Trans. Electron Devices, Vol. ED-34, pp. 367-377, 1987.

Table 2: Thermal resistance  $R_{th}$  and thermal capacitance  $C_{th}$  of three Si BJTs with the same emitter area.

| Emitter Area              | $R_{th}(L/W)$ | $C_{th} (nJ/L)$ |

|---------------------------|---------------|-----------------|

| 0.6µm×32µm×3              | 286           | 8.07            |

| 0.6µm×16µm×6              | 290           | 7.43            |

| (0.6µm×16µm×1)×6sub-cells | 254           | 7.43            |

Table 1: Collector current density difference  $\Delta J_{\rm C}$ , cutoff frequency difference  $\Delta f_T$ , and maximum oscillation frequency  $\Delta f_{max}$  of Si BJTs with different emitter design. V<sub>CE</sub> = 4V, V<sub>BE</sub> = 1.1V.

| Emitter Area              | J <sub>C</sub> (CW) | J <sub>C</sub> (pulse) | $\Delta J_{\rm C}$ | f <sub>T</sub> (CW) | f <sub>T</sub> (pulse) | $\Delta f_{\mathrm{T}}$ | f <sub>max</sub> (CW) | f <sub>max</sub> (pulse) | $\Delta f_{\text{max}}$ |

|---------------------------|---------------------|------------------------|--------------------|---------------------|------------------------|-------------------------|-----------------------|--------------------------|-------------------------|

|                           | (μA/μm²)            | (μA/μm <sup>2</sup> )  | (μA/μm²)           | (GHz)               | (GHz)                  | (%)                     | (GHz)                 | (GHz)                    | (%)                     |

| 0.6µm×32µm×3              | 452.1               | 424.3                  | 27.8               | 13.2                | 14.2                   | 7.3                     | 18.4                  | 19.2                     | 4.3                     |

| 0.6µm×16µm×6              | 458.3               | 433.3                  | 25.0               | 9.5                 | 10.3                   | 8.1                     | 15.3                  | 16.0                     | 4.5                     |

| (0.6µm×16µm×1)×6sub-cells | 411.5               | 396.7                  | 14.8               | 17.3                | 18.2                   | 5.1                     | 19.4                  | 19.9                     | 2.5                     |

Fig. 1. Base voltage, collector voltage and collector current pulse shapes of a BJT.

Fig. 4 The modeling results of S11 and S22 traces for the Si BJT biased at  $V_{BE} = 1V$  and  $V_{CE} = 2V$ . The emitter area is  $0.6\mu m \times 32\mu m \times 3finger$ .

16 14 V<sub>BE</sub>=1V 0.95V 0.95V 0.99V 0.95V 0.95V

Fig. 2 Cutoff frequency as a function of collector current for a Si BJT under different pulsed-mode measurement.

Fig. 5 Modeled and measured current dependence of the output power at the fundamental (2.4GHz),  $3^{rd}$ order and  $5^{th}$  order inter-modulation frequencies.  $V_{CE}$ = 3V, Pin = -7dBm,Tone spacing = 1MHz. The emitter area of the Si BJT is 0.6µm×32µm×3finger.

Fig. 3 Measured and simulated current-voltage characteristics under forward operation of the Si BJT with emitter area =  $0.6 \mu m \times 32 \mu m \times 35 \mu m$

Fig. 6 Modeled and measured current dependence of the output power at the fundamental(2.4GHz), second and third harmonic frequencies. $V_{CE}$  = 3V, Pin=-7dBm. The emitter area of the Si BJT is 0.6µm×32µm×3finger.