# Efficient Improvement of Hot-Carrier-Induced Degradation for Sub-0.1µm CMOSFET

Chieh-Ming Lai<sup>1</sup>, Chia-Che Hu<sup>2</sup>, Jung-Chun Lin<sup>3</sup>, Shing-Tai Pan<sup>2</sup>, Wen-Kuan Yeh<sup>4</sup>

Institute of Microelectronics, National Cheng Kung University, Taiwan.

Department of Computer Science Information Engineering, Shu-Te University, Taiwan.

Department of Electrical Engineering, National University, Taiwan.

Department of Electrical Engineering, National University, Taiwan.

No. 700, Kaohsiung University Rd., Nan-Tzu. Dist. 811, Kaohsiung, Taiwan. Tel: 886-7-5919372, Fax: 886-7-5919374, E-mail: wkyeh@nuk.edu.tw

Abstract - The effect of post-thermal annealing (PA) after halo implantation on the reliability of sub-0.1 $\mu$ m CMOSFETs was investigated. We found that the control of annealing time is more efficient than that of annealing temperature with respect to improving the hot-carrier-induced device degradation. The best results of device performance were obtained with post-annealing treatment performed at medium temperatures for a longer time.

### Introduction

Engineering channel dopant profiles obtained by localized halo implantation have been extensively used in sub-0.1 $\mu$ m CMOSFETs [1]. Owing to low diffusion constant, indium (In) has been successfully used in fabricating abrupt and shallow halo profiles for deep submicron nMOSFETs. Unfortunately, interstitial Si caused by the In ion implantation results in the increase of leakage current and the degradation of device performance [2]; thus, a post-thermal annealing (PA) treatments after In-halo implantation are proposed to solve these problems. Besides, the PA will also affect pMOSFET's performance. In this work, the effect of PA on hot-carrier-induced device degradation was investigated for the sub-0.1 $\mu$ m CMOSFETs.

## **Experiments**

Sub-0.1µm CMOSFET was fabricated with 2nm nitride gate oxide using dual gate twin-well process. After gate patterning, n/p source/drain extension were formed with arsenic (As) as well as Boron (B) implantations in respectively. Then tilted-angle halo-implantation at 20~30 degree with B (at 10~30KeV, 2~5 x 10<sup>13</sup> cm<sup>-2</sup>) as well as In (at 120~180KeV, 1~3 x 10<sup>13</sup> cm<sup>-2</sup>) for nMOSFET, and As (at 110~130KeV, 2~4 x 10<sup>13</sup> cm<sup>-2</sup>) for pMOSFET. After halo implantation, various post annealing were employed at 900 to 1050°C with various annealing time. Then n<sup>+</sup>/p<sup>+</sup> deep source/drain junction was formed with As and B ion implantation in respectively. Finally, wafers were processed through CoSi<sub>2</sub> salicidation process and a standard backend flow to completion. To investigate the HCE, device stressing and measurements were made on a probe station at various drain voltages ( $|V_G| = 1.2~2.0V$ ) and gate voltages ( $|V_G| = 0~1.8V$ ) with a stressing time ranging from 0 to100min.

#### **Results and Discussions**

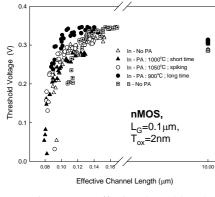

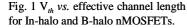

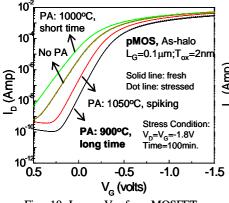

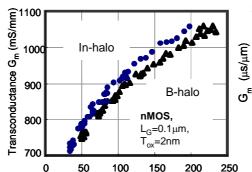

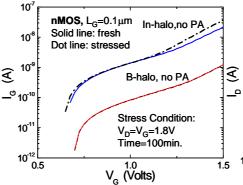

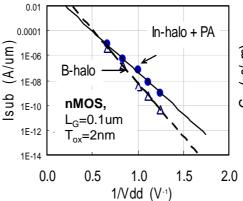

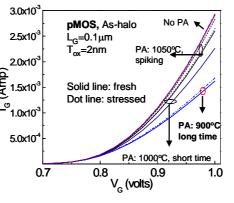

As shown in previous study [3], in comparison with B-halo structure, the margin of device's punch-through can be improved with In-halo structure because of the localized junction profile; thus, In-halo is able to suppress the nMOSFET's SCE down to sub-0.1µm channel length, as shown in Fig. 1. Figure 2 shows intrinsic transconductance (G<sub>m</sub>) versus with DIBL distribution, it is worth noting that the mobility of In-halo nMOSFET was better than that of B-halo device especially as  $L_{eff}$  less than 0.1µm. Since a large amount of Si interstitial, which generated by As-extension implantation and enhanced by In-halo implantation, can react with In dopant more efficiently, resulting in a more pronounced deactivation and causing an accelerated V<sub>th</sub> roll off for short-channel devices. Thus, PA was proposed to remove these Si interstitial and suppress the TED phenomena. In this work, Si interstitial can be removed by an annealing especially at lower temperature and longer time without degrades device's SCE. Although the localized In-halo dopant located only around extension junction without degrading the device's driving capacity [3], the hot-carrier effect of In-halo device was still a problem and became more serious as device dimension decreases. In comparison with B-halo nMOSFET, the hot-carrier-induced G<sub>m</sub> degradation of In-halo nMOSFET becomes more serious after hot-carrier stress especially at higher gate voltage, as shown in Fig. 3. For In-halo nMOSFET, the abrupt and shallow junction profile increases drain electric field and enhances high impact-ionization rate of channel carrier, thus aggravates the hot-carrier effect. It is apparently that B-halo device

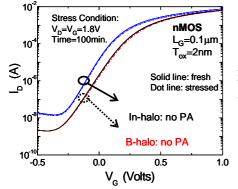

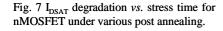

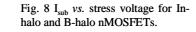

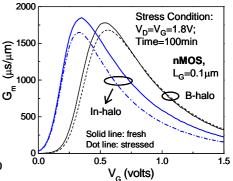

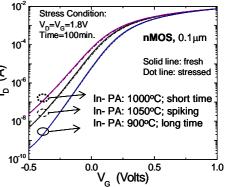

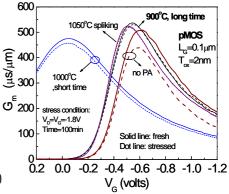

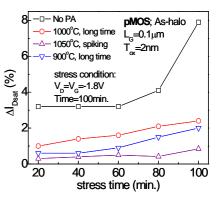

shows lesser junction leakage than In-halo device, as shown in Fig. 4. According to the results of B. Yu et.al [1], B-halo nMOSFET shows normal recombination-generation junction leakage happen, while high localized dose of In-halo nMOSFET indicates that the drain to halo (body) band-to-band tunneling current starts to present. This tunneling leakage can be considerable contributor to the device's off-state leakage current (Ido), resulting in higher device's Ido with In-halo structure. The swing degradation indicates the creation of interface traps resulting in a threshold voltage shift [4]. The gate-induced drain leakage (GIDL) in both nMOSFETs at a negative gate bias of  $V_G = -0.5V$  was also increased. It has been reported that GIDL is a direct result of the generation of interface states; thus, the largest degradation in I<sub>Dsat</sub> coincides with the largest increase in interface state density. In comparison with B-halo nMOSFET, the In-halo nMOSFET subthreshold characteristic shows larger Ido and GIDL. Furthermore, the gate leakage of In-halo device was larger than that of B-halo device, and will be enhanced after hot carrier stress, as shown in Fig. 5. With appropriate PA, the In-halo device's subthreshold characteristic can be improved and GIDL was suppressed apparently, as shown in Fig 6. The device's subthreshold swing and Ido can be improved especially at 900°C with longer time annealing. Fig. 7 reveals that the hot-carrier-induced saturated drain current (Idsat) degradation of In-implanted nMOSFETs was more serious than that of B-implanted nMOSFETs. With an appropriate PA, the I<sub>dsat</sub> degradation of all In-implanted devices was improved and lowers than that of B-implanted devices. For In-halo nMOSFET, very low drain degradation (<3%) can be obtained by PA at medium temperature with enough annealing time. Because the impact ionization caused by electron can be suppressed with appropriate PA, In-halo shows longer lifetime than B-halo nMOSFET especially at stress voltage larger than 1.5V, as shown in Fig. 8. For pMOSFET, Si interstitial still happens after As-halo implantation. These interstitial will degrades device performance and enhances hot carrier effect. Fig. 9 shows G<sub>m</sub> of pMOSFET was decayed apparently after hot carrier stress. Thus, PA is necessary to improve this problem. However, pMOSFET's characteristic will be degraded during PA due to the out-diffusion of channel doping-profile, causing threshold voltage  $(V_t)$  shift especially at  $1000^{\circ}C$  annealing. In this work, hot-carrier-induced  $G_{\rm m}$  degradation can be improved especially with PA using 900°C and longer time without Vt shifting. And the devices subthreshold swing as well as gate leakage were also improved and has no degradation apparently after hot carrier stress, as shown in Fig. 10 and 11 respectively. With appropriate PA, the hot-carrier-induced Idsat degradation of As-halo pMOSFET can be improved, as shown in Fig. 12. Very low drain degradation (<1%) was obtained by PA at 900°C with enough annealing time.

#### Conclusion

In this work, post thermal annealing effect impact on hot-carrier-induced reliability of 0.1µm CMOSFET was inspected. For In-halo nMOSFET as well as As-halo pMOSFET, hot-carrier-induced device degradation can be improved by post annealing especially at medium temperature with long time annealing without degrading device's performance.

## Acknowledgement

The authors would like to thank UMC TD/Logic Advanced Device Group for helpful comment. The National Science Council of Taiwan, R.O.C., under Contract NSC 90-2215-E-390-001, supported this work.

#### References

- 1) B. Yu et. al, IEEE IEDM Tech. Dig., 1999, pp.653-657.

- 2) Y. Taur et. al, IEEE, EDL-13. pp. 267-269, 1992.

- 3) W.-K. Yeh et. al., IEEE ED, vol. 48, pp.2357-2362, 2001.

- 4) P. T. Lai, et al., IEEE ED, vol.45, pp. 521-528, 1998.

Fig. 4  $I_D$  vs.  $V_G$  for In-halo and B-halo nMOSFETs before and after hot carrier stress.

Fig. 10  $I_D$  vs.  $V_G$  for pMOSFETs before and after hot carrier stress.

Drain Induced Barrier Lowing DIBL (mV/V)

Fig. 2  $G_m$  vs. DIBL for In-halo and B-halo nMOSFETs.

7

Fig. 5  $I_G vs. V_G$  for In-halo and B-halo nMOSFETs.

Fig. 11  $I_G vs. V_G$  for pMOSFETs under various post annealing.

Fig. 3  $G_m$  vs.  $V_G$  for In-halo and B-halo nMOSFETs before and after hot carrier stress.

Fig. 6  $I_D vs. V_G$  for In-halo and B-halo nMOSFETs before and after hot carrier stress with various post annealing.

Fig. 9  $G_m$  vs.  $V_G$  for pMOSFETs before and after hot carrier stress.

Fig. 12  $I_{DSAT}$  degradation *vs.* stress time for pMOSFET under various post annealing.