## Impact of Ti/TiN (Glue/Barrier Layer) Formation on Ultra-thin Gate Oxide Reliability (HCI and NBTI) for Deep Sub-micron CMOS Transistors

Chuan H. Liu<sup>\*</sup>, M.G. Chen, Y.R. Yang, and Y.T. Loh

United Microelectronics Corp., No. 3, Li-Hsin Rd. II, Science-Based Industrial Park, Hsin-Chu City, Taiwan, R.O.C. \*Tel: 886-3-5782258 Ext. 39157; Fax: 886-3-5642150; E-mail: chuan\_h\_liu@umc.com

## 1. Introduction

Use of a low temperature Ti/TiN (glue/barrier) layer is essential in producing deep sub-micron CMOS transistors with high performance and excellent reliability. TiN has been widely used in the IC industry as a diffusion barrier and adhesion layer material for tungsten (W) and aluminum (Al) interconnects. Because the step coverage and conformality of TiN becomes increasingly important as device dimensions shrink, CVD TiN is preferred compared to PVD TiN. In general, the CVD TiN process has been developed to achieve high step coverage, low resistivity, and low defect density. CVD TiN can be deposited using TiCl<sub>4</sub> and NH<sub>3</sub>[1]:

$6\text{TiCl}_4 + 8\text{NH}_3 \Longrightarrow 6\text{TiN} + 24\text{HCl} + \text{N}_2, \tag{1}$

in which the deposition temperature ranges from 450 to 750°C. It should be noted that chlorine (Cl) is always incorporated in the TiN film through this  $TiCl_4$ -based CVD process and the amount increases as the deposition temperature decreases, which may increase the resistivity. However, it will be shown that an appropriate amount of Cl introduced by this process can improve HCI and NBTI reliability. The TiN film can also be deposited by means of metal organic precursors [2]. One popular example is to thermally deposit TiN from TDMAT, i.e.  $Ti[N(CH_3)_2]_4$ , carried by helium (He) carrier gas:

$Ti[N(CH_3)_2]_4 => TiN(C,H) + HN(CH_3)_2$

+ other hydrocarbons, (2)

where the deposition temperature is 400 to 500 °C. In this MOCVD TiN process, hydrogen and carbon impurities are contained in the film, which can be reduced by a subsequent in-situ  $N_2$ -H<sub>2</sub> plasma treatment.

Although TiN is an excellent diffusion barrier material, TiN directly in contact with silicon results in a high contact resistance. A Ti layer below the TiN is usually utilized as a glue layer to ensure good contact resistance [3]. The Ti layer can be formed by ion metal plasma (IMP) PVD technique [4]. In brief, IMP Ti process is to ionize the sputtered atoms from the Ti target and then deposit the sputtered atoms. The Ti layer can also be deposited by TiCl<sub>4</sub>-based PE (plasma enhanced) CVD process [5] as follows:

$$TiCl_4 + 2H_2 + 2Si \Longrightarrow TiSi_2 + 4HCl,$$

(3)

in which the deposition temperature ranges from 400 to 700°C.

In this work, we investigate the impact of different Ti/TiN deposition processes on HCI and NBTI reliability, and it's found that IMP Ti / TiCl<sub>4</sub>-based CVD TiN layer exhibits low contact resistance and excellent HCI & NBTI reliability.

#### 2. Experimental

All the devices used in this study were simultaneously processed using a standard CMOS fabrication technique as briefly summarized in Fig. 1, in which different Ti/TiN deposition methods were processed as listed in Table I. A HP4284 LCR meter in parallel mode was used for capacitance-voltage (C-V) measurement, and a HP4156 semiconductor parameter analyzer was utilized for the measurement of electrical properties and reliability characteristics.

## 3. Results and Discussions

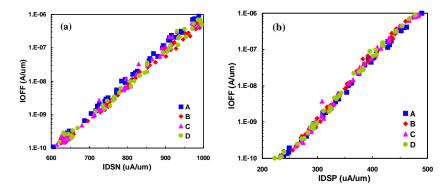

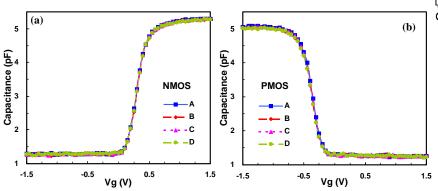

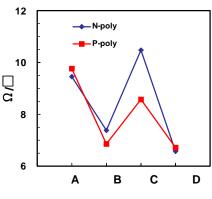

Figure 2 and Fig. 3, respectively, show the Ion-Ioff characteristics and gate to inversion channel C-V characteristics of (a) nMOSFETs and (b) pMOSFETs for different deposition methods of the Ti/TiN layer. It is apparent that the Ion-Ioff characteristics or C-V characteristics is independent of Ti/TiN formation technique. On the other hand, the contact resistance of N-poly and P-poly is shown in Fig. 4, in which condition B (TiCl<sub>4</sub>-based CVD Ti/TiN) and condition D (IMP Ti/ TiCl<sub>4</sub>-based CVD TiN) demonstrate lower contact resistivity. The higher contact resistivity for condition A (IMP Ti/MOCVD TiN) and condition C (TiCl<sub>4</sub>-based CVD Ti/MOCVD TiN) can be explained by the organic material impurities in the film as indicated in (2).

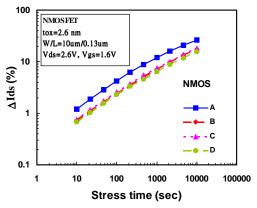

Figure 5 shows the hot carrier degradation for nMOSFETs at the maximum substrate current (Isub,max) stress condition. It is clear that condition A has the worst hot carrier immunity, and condition D exhibits slightly better hot carrier reliability characteristics than condition B and C.

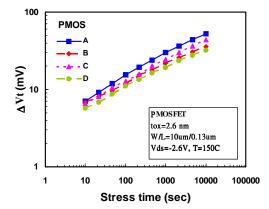

Figure 6 compares the threshold voltage shift versus stress time for pMOSFETs during a typical NBTI stress [6] at a stress bias of -2.6V and an elevated temperature of 150 °C. As seen in Fig. 6, condition D has the best NBTI immunity. It should be mentioned here that Fig. 5 and 6 represent the typical HCI and NBTI reliability characteristics for twelve samples tested.

#### 4. The Effect of Chlorine

Among four different formation methods, the glue/barrier layer formed by IMP Ti/ TiCl<sub>4</sub>-based CVD TiN demonstrates the best HCI and NBTI reliability for the first time. A model has been proposed to explain the phenomena as follows. Some of the chlorine contained in the TiN film formed by TiCl<sub>4</sub>-based CVD process diffuses to gate dielectrics through IMP Ti film (columnar structure) and poly-Si gate. The presence of chlorine in the gate dielectrics can passivate dangling bonds in the gate oxide transition region by forming Si-Cl bonds, and accordingly improve HCI and NBTI reliability because Si-Cl bonds are more difficult to break than Si-H bonds under HCI or NBTI stress.

#### Acknowledgment

The authors would like to acknowledge the personnel of UMC/FabCRD for device fabrication, and all the engineering and management support from CRD and Q&RA.

#### References

- M.J. Buiting, A.F. Otterloo, and A.H. Montree, J. Electrochem. Soc., vol. 138, p. 500, 1991.

- [2] C.M. Wu, M.Y. Wang, S.L. Shue, C.H. Yu, and M.S. Liang, Symp. on VLSI-TSA, p. 261, 2001.

- [3] C.Y. Chang and S.M. Sze, ULSI Technology, McGraw-Hill, 1996.

- [4] G.A. Dixit et al., IEDM, p. 357, 1996.

- [5] S.B. Kang et al., ITC, p. 70, 2000.

- [6] C.H. Liu et al., IEDM, p. 861, 2001.

Table I: Ti/TiN (glue/barrier layer) formation methods.

| Conditions         | Α  |     | В  |     | С  |     | D  |     |

|--------------------|----|-----|----|-----|----|-----|----|-----|

| glue/barrier layer | Ti | TiN | Ti | TiN | Ti | TiN | Ti | TiN |

| MOCVD              |    | Χ   |    |     |    | Χ   |    |     |

| IMP                | Χ  |     |    |     |    |     | Χ  |     |

| TiCl4-based CVD    |    |     | Χ  | Χ   | Χ  |     |    | Χ   |

# Fig. 2 Ion versus Ioff characteristics of (a) nMOSFETs and (b) pMOSFETs for different deposition methods of the Ti/TiN layer.

## • STI

- Well and channel implantation

- Dual gate oxynitride (2.6 & 6.5nm)

- Gate poly-Si deposition

- Offset spacer formation

- Extension implantation

- SiN sidewall spacer deposition

- S/D implantation and activation

- Co salicide formation

- Metallization

Fig. 1 CMOS fabrication process flow.

Fig. 4 Contact resistance of N-poly and P-poly for four Ti/TiN formation methods as listed in Table I.

Fig. 3 C-V characteristics of (a) nMOSFETs and (b) pMOSFETs for different deposition methods of the Ti/TiN layer.

Fig. 5 Hot carrier injection (HCI) degradation for nMOSFETs at maximum substrate current stress condition.

Fig. 6 Threshold voltage shift versus stress time under negative bias temperature instability (NBTI) stress.