# **P7-5** Observation of current modulation in SAM-FET fabricated by an air-bridge structure

Kazuki Sasao, Yasuo Azuma, Naotaka Kaneda, Eiji Hase, Yasuyuki Miyamoto, and Yutaka Majima

Department of Physical Electronics, Graduate School of Science and Engineering,

Tokyo Institute of Technology

We report on the study of SAM-FET made with a new fabrication process using an air-bridge structure. We measured 3-terminal current-voltage characteristics, and found that drain current increased exponentially with drain voltage, and was modulated with gate bias. The observed largest modulation amplitude of 30 pA was larger than the noise/leakage current of  $\pm 4$  pA. The fabrication process and detailed measurement result will be described.

## 1. Introduction

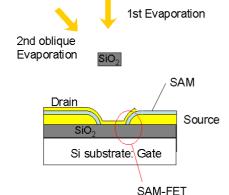

High-speed electronic devices are in great demand these days. The key technology to make faster devices is miniaturization, but it is expected to slow down due to a limitation in lithography technique such as critical dimension control. In order to overcome this limitation, we employ an device molecule organic made with а self-assembled monolayer (SAM) molecule. This substance is particularly interesting because single layer can be formed easily on a metal surface by immersing a substrate into a SAM solution. [1][2] Thus it enables us to produce uniform gate channel of 1 to 2[nm]. We previously reported the study on Au/SAM/Au junctions made by EB lithography. [3] In the present study we employed an air-bridge structure to isolate source from drain electrodes. (See Fig.1) It enabled much easier device fabrication. We used benzene-1, 4-dithiol as material of SAM.

### 2. Fabrication process

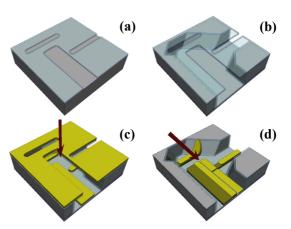

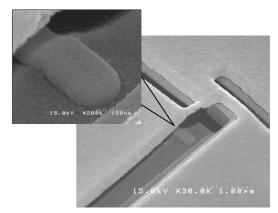

We first cleaned an n-Si (100) substrate with RCA solution, and made a 70nm-thick SiO<sub>2</sub> layer by thermal oxidation. Then we made a pattern shown in Fig.2 (a) by EB lithography and transferred it into SiO<sub>2</sub> by BHF wet etching. After the process, approximately 700nm-thick Si layer was etched by tetra methyl ammonium hydroxide, and a 50nm-thick SiO<sub>2</sub> gate layer was made by thermal oxidation. As shown in Fig.2 (b), a  $SiO_2$ air-bridge is structured. Then we formed a 100nm-thick Au source electrode by EB evaporation, and annealed it at 325°C for 45min to realize atomically flat surface. (Fig.2 (c)) We immersed the substrate in acetonitrile with 5mM benzene-1, 4-dithiol for 12 hours to fabricate a SAM layer. Immediately after this process, an Au drain electrode was deposited by EB evaporation. (Fig2 (d)) During this process, we kept the sample at low temperature (-110°C) in order to prevent it from damaging. In addition, the evaporation angle was chosen to be small against the sample, and the deposition rate was kept low (0.1nm/s). Fig.3 shows the SEM image of our actual device.

### 3. Measurement results and Discussions

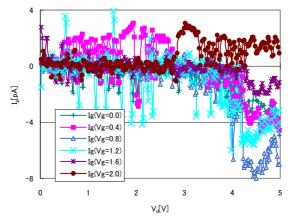

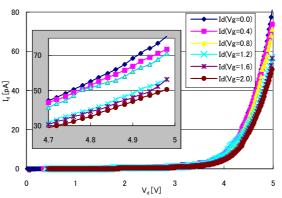

Three terminal current-voltage characteristics were observed at room temperature. To confirm modulation of drain current by gate bias, gate leakage must be smaller than modulated drain Unfortunately, strong noise in gate current. current was observed. The largest amplitude of the noise was  $\pm 8$  pA. Because the noise was periodic and half of the period was equal to period of measurement coincidently, simple smoothing by average of three points, i.e., gate current of k th point after smoothing equal was to  $I_{g}(k-1) + 2I_{g}(k) + I_{g}(k+1)$ , reduced the noise 4

drastically. The gate currents after the simple smoothing are shown in Fig. 4(a). The amplitude of the noise after the smoothing was less than  $\pm 4$ pA. Figure 4(b) shows common-source drain current-voltage characteristics after the smoothing. With increase of drain voltage, exponential increase of drain current was observed. Modulation of drain current by gate bias was observed. However, amount of the modulation was changed by the gate bias. As shown in inset of Fig. 4(b), large modulation was observed when gate bias was changed from 0.8 to 1.2 V, while modulation was very weak when gate bias was changed from 0.4 to 0.8 V and from 1.2 to 1.6 V. When gate bias was changed from 0 to 2V at drain voltage of 5 V, total modulated drain current of 30 pA was larger than observed gate current clearly. At successive measurement with same bias conditions, modulated magnitude was changed by each measurement, although the decrease of drain current by increase of gate bias was observed. We also carried out the same measurements with negative gate bias from 0 to -2 V, and similar modulation of drain current was observed, although the modulation rate was weaker. The no reproducibility of the measurements might be due to some changes in the property and/or number of the SAM molecules contributing to the current flow. When we applied negative drain voltage, the drain current did not show the exponential change and the device was suddenly broken by large current when the drain voltage was around -5 V.

Observed largest drain current was 80 pA. This amplitude was too small compared with previous report [4]. This might be due to no chemical bonding between Au upper electrode does and thiol-end group. We have a plan to increase drain current by choosing other SAM molecules in the future.

#### 4. Conclusion

We fabricated a SAM-FET device with the air-bridge structure. We measured 3-terminal current-voltage characteristics, and found drain current increased exponentially with drain voltage, and was modulated with gate bias. The observed largest modulation amplitude of 30 pA was larger than the noise/leakage current of  $\pm 4$  pA. However, the magnitude of drain current was too small compared with previous report. Other SAM molecules capable of producing larger drain current are required in the future.

#### Acknowledgements

The authors would like to thank Professors K.Furuya, S.Arai, M.Asada and Associate Professor M.Watanabe of the Tokyo Institute of Technology for their useful discussions and encouragement. This work was supported by Nanotechnology Support Project and Grants-in-Aid for Fundamental Reserch (#15310103) of the Ministry of Education, Culture, Sports, Science and Technology.

### Reference

[1] J. Chen, M. A. Reed, A. M. Rawlett, and J. M. Tour, "Large on-off ratios and negative differential resistance in a molecular electron device", Science, **286**, 1550-1552, 1999.

[2] P. S. Damle, A. W. Ghosh, S. Datta, "Unified description of molecular conduction: From molecules to metallic wires", Phys. Rev. B, **64**, 201403, 2001.

[3] Y. Majima, K. Sasao, Y. Azuma, and Y. Miyamoto, "Fabrication and I-V characteristics of metal/SAM/metal devices", 2002 International Microprocesses and Nanotechnology Conference 6B-3-7, Tokyo, Oct., 2002.

[4] M.A. Reed, C. Zhou, C.J. Muller, T.P. Burgin, and J.M. Tour,"Conductance of a molecular junction", Science, **278**, 252-254, 1997.

SAM-FET Fig.1 Schematic cross section of fabricated device

Fig.2 Schematic pictures of fabrication process

Fig.3 SEM image of actual device

Fig.4 (a) Gate current-drain voltage characteristics

Fig.4 (b) Drain current-drain voltage characteristics