# High-Perfection Approaches to Si-based Devices through Strained Layer Epitaxy

J.C. Sturm<sup>1</sup>, Haizhou Yin<sup>1,2</sup>, R L. Peterson<sup>1</sup>, K.D. Hobart<sup>3</sup>, and F.J. Kub<sup>3</sup>,

<sup>1</sup>Princeton Institute for the Science and Technology of Materials and Department of Electrical Engineering,

320 Bowen Hall, Princeton University, Princeton, NJ 08544, USA, Phone: +1-609-258-5610

Fax: +1-609-258-1177 E-mail: sturm@princeton.edu

<sup>2</sup>Current address: IBM Watson Research Center, Yorktown Heights, NY 10598

<sup>3</sup>Naval Research Laboratory, Washington, DC 20357 USA

## 1. Introduction

In developing materials and processes for VLSI, the demands of high manufacturing yield make it necessary to consider approaches which are inherently capable of creating structures without defects. For example, the success of the well-known Si/SiGe/Si HBT relies on pseudomorphic strained layers below critical thickness to avoid misfit dislocations. Similarly, since the role of strain was first made clear in altering the band alignment in Si/SiGe heterostructures [1], there has been a nearly 20-year search for technological approaches to achieve virtual substrates layers with in-plane lattice constants different than those of the Si substrates, on top of which pseudomorphic layers could be grown with low defect densities. The usual approaches for such virtual substrates involve growing a "relaxed" layer such as SiGe by lattice-mismatched epitaxy. The mismatch must be taken up by misfit dislocations, and their inevitable interaction leads to threading defects which reduce the quality of such layers. Typical densities in modern approaches are still  $\sim 10^5$  cm<sup>-2</sup>.

In this work, we describe an approach for achieving relaxed SiGe layers and strained Si based on transferring a fully-strained pseudomorphic layer to a borophosphorosilicate (BPSG) layer, which can then allow the strain to relax at elevated temperature due to BPSG softening. Unique aspects of the process are that:

(i) in principle no dislocations of any sort are required, so that low-defect virtual substrates can be achieved

(ii) the method allows a true compliant substrate, where the strain in all layers in a structure change at the same rate

(iii) strained Si-on-insulator (without SiGe) with Si thicknesses as thin as 10 nm are possible

(iv) unstrained and strained Si can be easily integrated on a single substrate, and

(v) in contrast to all other strained Si or strained Si-on-insulator approaches, one can create structures with *uniaxial* (instead of the usual *biaxial*) strain.

### 2. Process Overview and Critical Features

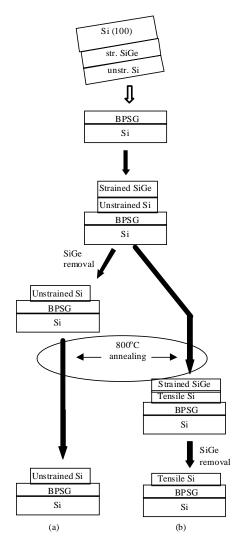

The process begins with the epitaxial growth of a pseudomorphic strained SiGe layer (or strained SiGe/unstrained Si multilayers) on a sacrificial wafer and the deposition of BPSG (0.2 to 1.0 um) on top of a handle wafer (Fig. 1). The wafers are joined by low-temperature bonding, and the sacrificial wafer is removed by the Smart-cut ©

process and selective etching, to leave the strained SiGe (or strained SiGe/unstrained Si layers) on the BPSG layer [2]. Because the SiGe layers are thin (e.g at most 30 nm in thickness for x=0.3), they can be grown without defects. The silicon layers can be grown without defects because they have no strain. The Smart-cut process does not affect the strain levels.

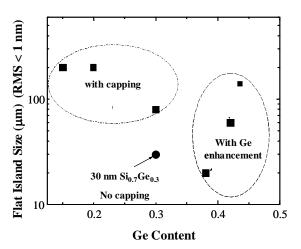

After transfer, at temperatures as low as 800 °C, the viscosity of the BPSG drops quickly, and when the viscosity is on the order of  $10^{10}$  Ns/m<sup>2</sup>, a single SiGe layer can expand laterally to relieve its compressive strain. The relaxation is accomplished via the plastic flow of the amorphous BPSG, so that the process is not mediated by and does not require dislocations. There is a possible parasitic buckling process, which also relieves strain, however, and it is mainly prevention of this phenomena which requires that the SiGe be patterned into islands (~100-500 microns in size at present) [3]. The initial Ge level is limited by critical thickness constraints during the original epitaxy (for low defect densities), but it can be subsequently raised to x=0.6 via oxidation [4,5] (Fig. 2).

### 3. Stress Balance and Anisotropic Effects

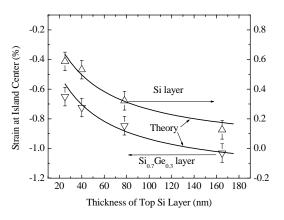

In a bilayer SiGe/Si structure (Fig. 1), as the SiGe expands it creates tensile strain in the Si. Removing the SiGe then yields an SOI layer as thin as 10 nm with strain levels ~1% and high n-channel FET mobilities [6]. As in Fig. 2, with the addition of a single masking step, strained and unstrained Si can be integrated onto the same substrate. The critical step is the coherent relaxation of the Si/SiGe bilayer - what is desired is that the two layers relax together without the introduction of misfit dislocations between the layers, since misfits could lead to threading defects. Fig 3 shows the final strain in both the SiGe and Si layers (in a structure with the Si over the SiGe) as the thickness of the Si was varied. As the silicon becomes thicker, the final strain in the Si is lower and that in the SiGe is higher, but the results are always in very close agreement with the ideal stress balance condition assuming no dislocations between the layers [7]. Most critically, for all Si thicknesses, the difference in the strain between the two layers does not change (within our <0.05% resolution in strain, as measured by Raman scattering [8]). This further confirms the true compliant nature of the BPSG.

The lateral relaxation of square strained islands depends on the square of the island size  $(L^2)$  [3], and leads to biaxially strained Si (strained in all in-plane directions). Rectangular islands will relax in the short direction before they can relax in the long direction. With this approach, we have succeeded in realizing uniaxially-strained Si (which is strained in one direction only) with strain levels as high as 1%. This presents further opportunities for device engineering [9].

### 4. Summary

The relaxation of transferred Si/SiGe layers on BPSG layers offers new possibilities for engineering the strain in Si-based heterostructures with very low defect densities, with strained Si-on-insulator without any SiGe layers as a technological driver. Novel features are the true compliant nature of the substrate which enables coherent relaxation of multilayers and the ability to achieve uniaxially strained films.

The authors thank T. Duffy and S. Shieh of Princeton University for their expert assistance with Raman microprobe characterization, and the group of Z. Suo for modeling and physical insight. The support of ARO and DARPA/ONR is greatly appreciated.

Fig. 1. Process flow for ultrathin (a) unstrained and (b) strained Si on insulator.

[1] G. Abstreiter, H. Burgger, T. Wolf, H. Jorke, and H.J. Herzog, Phys. Rev. Lett. **54**, 2442-2444 (1985).

[2] K.D. Hobart, F.J. Kub, M. Fatemi, M.E. Twigg, P.E. Thompson, T.S. Kuan and C.K. Inoki, J. Electron. Mater. **29**, 897 (2000).

[3] H. Yin, R. Huang, K.D. Hobart, J. Liang, Z. Suo, S.R. Shieh, T.S. Duffy, F.J. Kub, and J.C. Sturm, J. Appl. Phys. **94**, 6875 (2003).

[4.] Haizhou Yin, K.D. Hobart, F. J. Kub, S. R. Shieh, T.S. Duffy, and J. C. Sturm, Appl. Phys. Lett. **84**, 3624-3626 (2004)

[5.] T. Tezuka, N. Sugiyama, T. Mizuno, M. Suzuki, and S. Takagi, Jpn. J. Appl. Phys. 40, 2866 (2001)

[6] H. Yin, K.D. Hobart, R.L. Peterson, S.R. Shieh, T.S. Duffy, F.J. Kub, and J.C. Sturm, Tech. Dig. International Electron Device Meeting IEDM, pp. 53-56 (2003).

[7] H. Yin, K.D. Hobart, F.J. Kub, S.R. Shieh, T.S. Duffy, and J.C. Sturm, Appl. Phys. Lett. **82**, 3853-3855 (2003)

[8] J. C. Tsang, P. M. Mooney, F. Dacol, and J. O. Chu, J. Appl. Phys. 75, 8098 (1994).

[9.] T. Ghani, M. Armstrong, C. Auth, et al,. IEDM (2003).

Fig. 2. Achievable island sizes and Ge content levels for relaxed single  $Si_{1-x}$  Ge<sub>x</sub> layers with flatness of 1 nm or better, showing improvement of basic method of Ref. [2] through of capping [3] and Ge enhancement [4,5] techniques.

Fig. 3. Strain in both Si and SiGe after annealing at 800  $^{\circ}$ C of a bilayer 30 nm Si<sub>0.3</sub>Ge<sub>0.7</sub>/Si as a function of silicon thickness, showing consistent tracking between the two strains and coherency between the two layers [7].