# InGaP/InGaAs DCFETs with Drain and Source Recess Process

Feng-Tso Chien<sup>1</sup>, Jin-Mu Yin<sup>1</sup>, Shin-Tzung Su<sup>2</sup>, Ming-Hung Lai<sup>2</sup>, Kou-Way Tu<sup>2</sup>, Ching-Ling Cheng<sup>2</sup>

<sup>1</sup>Dept. of Electronic Engineering, Feng Chia University, Taichung, Taiwan 32054, R.O.C

Phone: +886-4-24517250 ext 4579 E-mail: ftchien@fcu.edu.tw

<sup>2</sup>R&D Dept., Chino-Excel Technology Corp., Chung-Ho, Taiwan, R.O.C.

### 1. Introduction

Doped-channel FETs (DCFETs) have demonstrated better device linearity, higher current density, and higher gate breakdown as well as higher turn-on voltages compared to HEMTs and MESFETs [1]. However, the main drawback of DCFETs is the high contact and sheet resistances of devices in the undoped Schottky access region between alloyed contact and gate electrode, which results in an increasing saturation voltage as well as thermal noise [2].

In this study, we proposed a drain-source ohmic contact recess doped-channel InGaP/InGaAs FET's (OR-DCFETs), and compared it with the conventional process in terms of dc, rf and power performances. The ohmic recess process can reduce the parasitic ohmic contact resistance, which cause by an undoped Schottky layer, and therefore, improve the device performance.

### 2. Device design

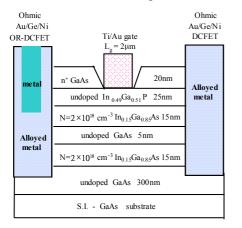

The OR-DCFETs and conventional DCFET structures, shown in Fig. 1, were grown in a Riber-32p molecular beam epitaxy (MBE) system on (100)-oriented semi-insulating GaAs substrate.

Fig. 1 The cross section of OR-DCFETs and DCFETs

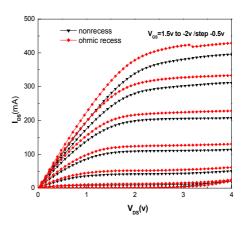

Here, double doped channel structures have been used for better device performances [3]. The process of these two structures are all the same except a ohmic recessed process on OR-DCFETs to reduce the undoped schottky layer alloy metal resistance. The threshold voltages for both devices are -2 V. The drain-to-source current (I<sub>DS</sub>) against voltage (V<sub>DS</sub>) characteristics with 2 µm-long gate devices were shown in Fig. 2.

Fig.2 IDS-VDS characteristics of OR-DCFET/DCFET

It is obvious that the ohmic contact resistances of OR-DCFETs are improved by the ohmic recess design. Fig.3 shows the transconductance  $(g_m)$ ,  $I_{DS}$ - $V_{GS}$  transfer characteristics. Both devices have the same  $g_m$  of 200mS/mm. We express the FETs  $I_{DS}$ - $V_{GS}$  curves by a 6th order polynomial form to describe the output characteristics as following [1], and the an's are listed in Table 1.  $I_{ds} = a_0 + a_1 V_{gs} + a_2 V_{gs}^2 + a_3 V_{gs}^3 + a_4 V_{gs}^4 + a_5 V_{gs}^5 +$

$I_{ds} = a_0 + a_1 V_{gs} + a_2 V_{gs} + a_3 V_{gs} + a_4 V_{gs} + a_5 V_{gs} + a_6 V_{gs}^6$ (1)

where an's are independent variables, which can determine the linearity associated with  $I_{DS}$ - $V_{GS}$  transfer characteristics. In table 1, we find that the

values an's/ $a_1$  for OR-DCFETs were much smaller than those for DCFETs. Therefore, higher linearity power performances can be expected for the OR-DCFETs by suppressing the 3<sup>rd</sup> (or higher)-order inter-modulation. A wide and uniform g<sub>m</sub> distribution of OR-DCFETs, as compared with DCFETs can be also observed in Fig. 3. The maximum drain current (gate voltage swing for 90% g<sub>m</sub>) is 500 mA/mm (1.5V) for OR-DCFETs, and 460 mA/mm (1.2V) for DCFETs, respectively.

Fig.3  $V_{gs}\mathchar`-g_m,\ I_{ds}$  characteristics of OR-DCFET and DCFET

| an       | aO     | a1     | a2/a1 | a3/a1   | a4/a1  | a5/a1  | a6/a1  |

|----------|--------|--------|-------|---------|--------|--------|--------|

| DCFET    | 202.03 | 204.83 | 0.082 | -0.1614 | -0.012 | 0.0206 | 0.004  |

| OR-DCFET | 237.08 | 210.76 | 0.057 | -0.1283 | -0.008 | 0.0109 | 0.0019 |

Table 1.Compare of harmonic distortion factors between OR-DCFET and DCFET

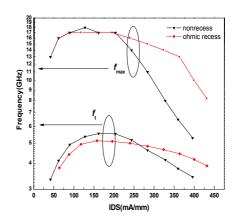

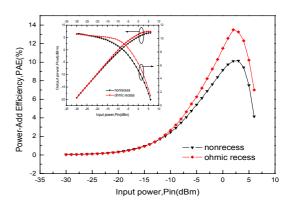

Microwave on-wafer S-parameters for 2.0 µm-long gate devices were measured by a HP-8510 network analyzer. A  $f_T$  and  $(f_{max})$  of 5.5 GHz (18 GHz) for D-DCFETs, 5.2 GHz (17Hz) for DCFETs were obtained at  $V_{ds}=2.5$  V, shown in Fig. 4, respectively. For DCFETs, a decrease of both  $f_T$  and  $f_{max}$  started to occur at  $I_{ds} > 250 mA/mm.$  However, no significant performance reduction was observed for OR-DCFETs till  $I_{ds} = 400 \text{mA/mm}$ . These microwave behaviors are similar to dc characteristics. Microwave power performances were characterized at  $V_{ds} = 2.5V$  under a 1.9 GHz operation for the gate dimension of  $2 \times 50 \ \mu m^2$  devices. Linear power gains were 11 dB for both devices. The maximum output power and PAE were 7.6 dBm (115 mW/mm) and 13 % for O-DCFETs, and 7 dBm (100 mW/mm) and

10.2 % for DCFETs, respectively. Although the performances are not so outstanding for these devices, better performances can be achieved by using shorter channel devices.

Fig. 4  $I_{DS}$  dependence of  $f_{T},$  and  $f_{max}$  for OR-DCFET and DCFET

Fig. 5 Power Performance comparison between OR-DCFET and DCFET

## 4. Conclusions

DCFETs with ohmic recess (OR-DCFET) process have been proposed and demonstrated improved characteristics than the conventional DCFETs devices. One can use this technology for sub-µm device for better performances.

#### References

- [1] Ming-Ta Yang, and Ti-Jen Chan, *IEEE Trans. Electrons Devices.* **43**, p.1174 (1996)

- [2] Hsien-Chin Chiu, Feng-Tso Chien, Shin-Cheng Yang, Ching-Wei Kuo, and Yi-Jen Chan, Electron. Lett., 36, 1320 (2000)

- [3] Feng-Tso Chien, Chien-Chin Chiol, and Yi-Jen Chan, IEEE Electron Device Lett., 36, p.60 (2000)