# Transmission characteristics of Gaussian monocycle pulse for inter-chip wireless interconnection using integrated antenna

K. Kimoto and T. Kikkawa

Research Center for Nanodevices and Systems, Hiroshima University Phone: +81-082-424-6265, Fax: +81-082-422-7185, E-mail: kimoto@sxsys.hiroshima-u.ac.jp, kikkawa@sxsys.hiroshima-u.ac.jp

#### 1. Introduction

oscilloscope.

## According to the scaling rule, the reduction in device feature sizes improves the performance of ultra-large-scale integrated circuits (ULSI) in terms of operation frequency and power consumption. However conventional metal interconnects will have limitation in global clock frequency of ULSI for high speed operation at 3-4 GHz due to parasitic RC (resistance -capacitance) delay.

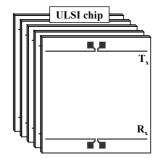

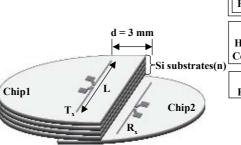

In order to overcome this problem, a new concept of wireless interconnection using Si integrated antennas has been proposed to send signals by electromagnetic wave so that both parasitic capacitance and resistance can be eliminated.<sup>[1,2]</sup> The conceptual diagram of inter-chip wireless interconnection for stacked multi-chip packaging using integrated antenna is shown in Figure 1. Si integrated antennas are fabricated on Si-ULSI so that the global clock signals can be sent from a transmitting antenna of one chip and received by a receiving antenna of another chip by electromagnetic wave propagation. Most of the radiated electromagnetic wave from the antenna on the Si substrate penetrates into the Si due to the difference in dielectric constants between Si ( $\epsilon_{Si}$ =12) and air ( $\epsilon_{Air}$ =1).<sup>[3]</sup>

In this study, the feasibility of inter-chip wireless interconnection using Si integrated antennas is investigated.

## 2. Fabrication and Measurement

P-type (100) Si substrates with 10  $\Omega$ ·cm resistivity were prepared. A 0.3 µm-thick SiO<sub>2</sub> was formed by pyrogenic oxidation at 1050°C on the 260 µm-thick Si substrate surface. A 1.0 µm-thick aluminum layer was deposited on the SiO<sub>2</sub> by direct current magnetron sputtering. 10 µm-wide and 2 mm long dipole antennas were fabricated by use of HL-700 electron-beam lithography and subsequent wet etching. Figure 2 shows the schematic diagram of inter-chip measurement sample structure. The Si wafers were stacked vertically and the horizontal distance between antennas (d=3 mm) and antenna length (L=2 mm) were fixed. The number of Si substrates (n) were varied from 1 to 10.

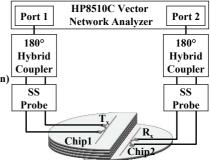

A wafer level measurement set-up for S-parameters in frequency domain is shown in Fig. 3. It consists of HP8510C Vector Network Analyzer, 180° Hybrid Couplers (6-26.5 GHz), probe station and Signal-Signal (SS) probes. Wafers were measured on wood (2.6 mm thick) on the metal chuck of the probe station. The relative dielectric constant of wood was 2.15 at 1 GHz.<sup>[3]</sup> From measured S-parameters reflection coefficient (S<sub>11</sub>) and transmission coefficient (S<sub>21</sub>), <sup>[4]</sup> antenna transmission gain (G<sub>a</sub>) through Si substrates can be calculated.

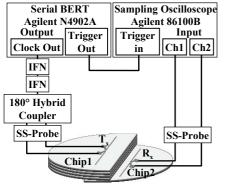

Figure 4 shows the measurement setup for inter-chip antenna transmission characteristics in time domain. It is composed of Agilent N4902A Serial BERT, two impulse forming networks, and Agilent 86100B sampling

## 3. Results and Discussion

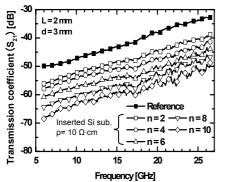

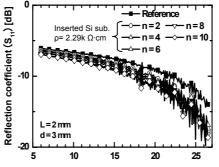

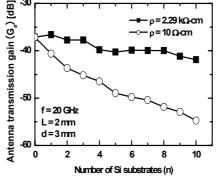

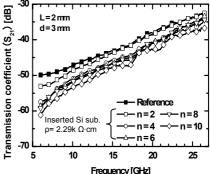

Effects of the number of inserted Si substrates on S<sub>11</sub> and S<sub>21</sub> of the dipole antenna (L=2 mm) in the stacked structure were shown in Figs. 5, 6 and 7. Neither S<sub>11</sub> nor S<sub>21</sub> were affected by the number of inserted Si substrates having  $\rho$ =2.29 k $\Omega$ ·cm very much as shown in Figs. 5 and 6. On the other hand, S<sub>21</sub> decreased with increasing the number of Si substrates having  $\rho$ =10  $\Omega$ ·cm as shown in Fig. 7. This is due to the loss of electromagnetic wave in Si substrates. Figure 8 shows the antenna transmission gain (G<sub>a</sub>) at 20 GHz versus the number of Si substrates for different Si substrates resistivities:  $\rho$ =10  $\Omega$ ·cm and  $\rho$ =2.29 k $\Omega$ ·cm. The attenuations in a Si substrate with  $\rho$ =2.29 k $\Omega$ ·cm and  $\rho$ =10  $\Omega$ ·cm were -0.48 dB and -1.6 dB, respectively.

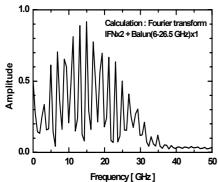

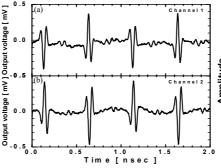

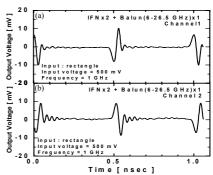

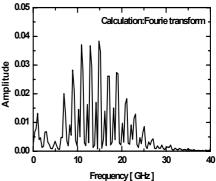

The transmitting Gaussian monocycle pulse was formed by inserting two cascade impulse forming networks at the output of the Serial BERT as shown in Fig. 9. Fast Fourier transform of the transmitting signal is shown in Fig. 10. The center frequency was 12.3 GHz and the band width was 14.3 GHz. The transmitting antenna with antenna length of 6 mm was radiated by Gaussian monocycle pulses shown in Fig. 9 and the received signal at the receiver dipole antenna which was located at the horizontal distance of 3 mm and vertical distance of 2.56 mm by stacking 10 Si substrates ( $\rho$ =2.29 k $\Omega$ ·cm) is shown in Fig. 11. Fast Fourier transform of the received signal is shown in Fig. 12. The center frequency was 15.8 GHz and the band width was 18.4 GHz. Therefore, the center frequency shifted higher approximately 3.5 GHz due to differentiation

## 4. Conclusion

We have demonstrated Gaussian monocycle pulse signal transmission in stacked Si substrates for inter-chip wireless interconnection by using Si integrated antennas.

#### Acknowledgements

This work is supported by the Ministry of Education, Culture, Sports, Science and Technology under the 21<sup>st</sup> Century COE program and the Grant-in-Aid for Scientific Research.

#### References

[1] Kihong Kim, Hyun Yoon and Kenneth K.O, IEDM Tech. Dig., pp.485-488, December 2000.

[2]A.B.M. H. Rashid, S. Watanabe and T. Kikkawa, IEEE Electron Device Letters, Vol. 23, No.12, December 2002, pp.731-733.

[3]S. Watanabe, A.B.M. H. Rashid and T. Kikkawa, Extended Abstract of SSDM 2003

[4] S. Watanabe, A.B.M. H. Rashid and T. Kikkawa, Advanced Metallization Conference 2002 Asian Session, pp. 94-95

$T_x$ : Transmitting antenna,  $R_x$ : Receiving antenna Fig.1. Concept of inter-chip wireless interconnect using dipole antennas integrated in multiple Si ULSI chips.

IFN : Impulse Forming Network Fig. 4. Measurement setup for inter-chip signal transmission characteristics in time domain.

Fig.7. Effect of the number of inserted Si substrates with  $\rho=10 \ \Omega \cdot cm$  on the transmission coefficient (S<sub>21</sub>) versus frequency. (Antenna L=2 mm, d=3 mm)

Fig.10. Fast Fourier transform of the transmitting Gaussian monocycle pulse signal.

Fig. 2. Schematic diagram of interchip measurement sample structure.

Frequency [GHz]

Fig.5. Effect of the number of inserted Si substrates with  $\rho = 2.29k \ \Omega \cdot cm$  on the reflection coefficient (S<sub>11</sub>) versus frequency. (Antenna L=2 mm, d=3 mm)

Fig.8. Antenna transmission gain  $(G_a)$  versus the number of Si substrates (n). (Antenna L=2 mm, d=3 mm)

Fig.11. Received signal at the receiver dipole antenna. (a) Channel 1. (b) Channel 2. (Antenna L=6 mm, d=3 mm, n=10 ( $\rho$ =2.29 k $\Omega$ ·cm))

Fig. 3. Measurement setup for inter-chip antenna transmission characteristics in frequency domain.

Fig.6. Effect of the number of inserted Si substrates with  $\rho = 2.29 \text{ k}\Omega \cdot \text{cm}$  on the transmission coefficient (S<sub>21</sub>) versus frequency. (Antenna L=2 mm, d=3 mm)

Fig.9. Transmitting Gaussian monocycle pulse for a transmitter dipole antenna. (a) Channel 1. (b) Channel 2.

Fig.12. Fast Fourier Transform of the received signal. (Antenna L=6 mm, d=3 mm, n=10 ( $\rho$ =2.29 k $\Omega$  cm))