# F-9-3 Pentacene TFTs Fabricated by High-aspect Ratio Metal Shadow Mask

Sung Hun Jin, Sang Min Yi\*, Keum Dong Jung, Chang Bum Park, Chong Nam Chu\*, Hyung Chul Shin, Byung-Gook Park, and Jong Duk Lee

Inter-university Semiconductor Research Center and School of Electrical Engineering, Seoul National University,

School of Mechanical and Aerospace Engineering, Seoul National University\*,

San 56-1, Shinlim-dong, Kwanak-gu, Seoul 151-742, Korea

Phone: +82-2-880-7282 Fax: +82-2-882-4658 E-mail: harin74@dreamwiz.com

## 1. Introduction

Among various organic semiconductors, pentacene continues to be an attractive material choice because of its high mobility on the order of 1 cm<sup>2</sup>/Vsec for a variety of electronic applications, including information displays [1-3], electronic paper [4], and radio frequency identification (RFID) [5]. Even though pentacene thin film transistors (TFTs) can be implemented in one of two configurations, i.e., top contact and bottom contact [6], the best performances of pentacene TFTs in the literature [7,8] have always been demonstrated in the top contact configuration due to the inherently favorable conditions of pentacene growth compared with bottom contact mode [6]. However, the top contact mode is incompatible with the conventional photolithography for the definition of source and drain (S/D) electrodes on organic semiconductors due to their intolerance to the exposure of solvents and other liquids [9]. Therefore, metal shadow masks are generally used to define the top S/D contacts on organic materials because they can guarantee simple S/D definition process without damage of organic materials. But the S/D patterning process by the conventional metal shadow mask ( $L_c \approx 20 \sim 70 \mu m$ ) [6], [9] has two major obstacles, which are high-resolution patterning [10] and mass manufacturability. While commercial products like OLED eliminate gradually the pessimistic prospect for the applications of a metal shadow mask to mass production [11], the high-resolution patterning using shadow masks can be a remaining barrier on highly integrated top-contact OTFTs [8].

To achieve top-contact OTFTs with a high areal density, several approaches including cold welding [12], high resolution rubber stamping [13] and special Si membrane masks ( $L_C \approx 10 \ \mu m$ ) [14] have been reported in the literature, whereas each method has fundamental drawbacks of too much-complicated implementation [12], low-level manufacturability for large area applications [13], and easy brittleness [14].

In this work, we proposed and implemented metal shadow masks with a high aspect ratio (AR) larger than 20, based on a combination of anisotropic micro-electro-discharge machining ( $\mu$ -EDM) [15] and isotropic electro chemical etching (ECE) [16] for the application of OTFTs scaled down to less than 5  $\mu$ m. The high-aspect ratio (HR) metal shadow masks have inherent merits of structural robustness, simple S/D patterning process, and re-usage. In addition, a batch mode  $\mu$ -EDM technique [17] can be fundamentally applicable to metals shadow masks of a high throughput and good uniformity for large area applications.

## 2. Experimental and Results

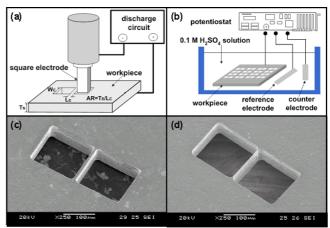

Figure 1 presents a schematic illustration of (a)  $\mu$ -EDM [15] and (b) ECE [16], which were used to fabricate metal shadow masks with high AR larger than 20. As shown in Fig. 1(a), an AR for a metal shadow mask is defined as the thickness of a shadow mask (T<sub>S</sub>) to the length of a bridge (L<sub>C</sub>). In this experiment,  $\mu$ -EDM system used the applied voltage of 100 V, a single RC pulse timing circuits with 500 pF and 1 k $\Omega$ , and a square copper electrode with one side length of 130  $\mu$ m and structural height of 1500  $\mu$ m fabricated by wire electrode discharge gliding (WEDG)[18]. The work pieces for shadow masks are 100 ± 5  $\mu$ m thick stainless steel (304 SS) with the size of 1.5 cm × 1.5 cm. After serially machining

FIG 1. Schematic configurations for (a) micro-electro-discharge machining ( $\mu$ -EDM) and (b) electro-chemical etching (ECE). The aspect ratio (AR) of an HR shadow mask denotes the ratio of the thickness of workpiece (T<sub>s</sub>) to the length of a bridge (L<sub>c</sub>). After  $\mu$ -EDM processing up to the channel length of 10  $\mu$ m, the work piece consecutively was electro chemically etched with an etch rate of 4.4 Å/sec in 0.1 mole H<sub>2</sub>SO<sub>4</sub> solution (c) A SEM image for a stainless steel shadow mask right after  $\mu$ -EDM process. After  $\mu$ -EDM process, L<sub>c</sub> is 10  $\mu$ m with an aspect ratio of 10 (d) A SEM image for a metal shadow mask right after  $\mu$ -EDM and ECE process. L<sub>c</sub> is 3.5  $\mu$ m with an aspect ratio of 28. The width of bridge (W<sub>c</sub>) is 150  $\mu$ m.

150 µm square contact holes using µ-EDM, the combinational process of ECE improves the AR of a metal shadow mask noticeably because the µ-EDM has a fundamental limit of the routinely machinable feature size ( $L_C \approx 10 \ \mu m$ ) as shown in Fig. 1(c). Figure 1(b) shows that process conditions of ECE system are the applied voltage of 1.2 V and the 0.1 mole H<sub>2</sub>SO<sub>4</sub> solution as electrolyte. Figure 1 (c) and (d) showed SEM images for a metal shadow mask after µ-EDM and ECE steps, respectively. To date, the length ( $L_C$ ) and width ( $W_C$ ) of the bridge can be routinely obtained as small as 5 ± 0.25 µm and 70 ± 1 µm, respectively.

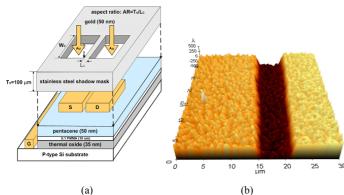

Figure 2(a) shows a schematic for the fabrication steps of pentacene TFTs. For a gate insulator, 35 nm thick thermal oxide was grown on a p-type wafer with the resistivity of 15  $\Omega$ cm. The thermal oxide was patterned by photolithography, and then etched by dilute HF solution for a gate electrode deposition. After cutting the patterned Si wafer to the size of  $2 \text{ cm} \times 2 \text{ cm}$ , each sample was spin-coated with a dilute PMMA solution to improve the ordering of pentacene due to the hydrophobic ending group methyl radical (-CH<sub>3</sub>) [19]. The coated PMMA thickness was 10 nm as measured by ellipsometery. A 50 nm thick pentacene was thermally evaporated on the PMMA treated gate oxide at a rate of about 0.3 Å/sec. During the deposition, the substrate temperature maintained at the temperature of 90  $^{\rm o}{\rm C}$  in the pressure of  $8{\times}10^{-8}$  torr. The pentacene of about 98 % purity was used without purification in this experiment. Finally 50 nm of gold was e-beam evaporated on pentacene active layer through a 100 µm thick HR shadow mask to define S/D contacts as well as the gate contacts. The dimension of source and drain contacts have the channel length ranging from 20  $\mu$ m to 5  $\mu$ m at a fixed channel width of 150  $\mu$ m.

Figure 2 (b) shows the AFM image of channel area for an OTFT with  $W_C$ =150 µm and  $L_C$ =5 µm. As shown in Fig. 2 (b), the

FIG 2. (a) Schematic illustration of process steps for pentacene TFTs fabricated using an HR metal shadow mask. The length of a bridge ( $L_c$ ) for metal shadow masks ranges from 20 µm to 5 µm with a fixed channel width of 150 µm (b) An AFM image for the defined channel area of OTFT with  $L_c$ =5 µm and W= 150 µm.

defined source and drain contacts have a good straight channel.

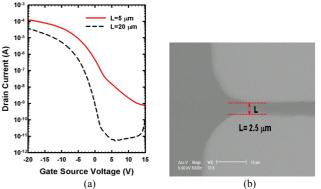

Figure 3 (a) shows the transfer characteristics of OTFTs with a different  $L_C$  of 5 and 20 µm for a fixed  $W_C$  of 150 µm in the saturation region. For the device with  $L_C$  of 20 µm, electrical parameters are the threshold voltage ( $V_{TH}$ ) of –1.3 V, subthreshold swing (SS) of 1.2 V/decade, current on-off ratio of  $7.1 \times 10^6$ , field effect mobility ( $\mu_{eff}$ ) of 0.421 ± 0.07 cm<sup>2</sup>/Vsec at gate-source voltage ( $V_{GS}$ ) of –10 V and drain-source voltage ( $V_{DS}$ ) of –20 V. On the other hand, the device with  $L_C$  of 5 µm has  $V_{TH}$  of 3.3 V, SS of 1.2 V/decade,  $\mu_{eff}$  of 0.498 ± 0.05 cm<sup>2</sup>/Vsec at the same  $V_{GS}$  and  $V_{DS}$ . As the  $L_C$  of OTFT reduces from 20 µm to 5 µm,  $V_{TH}$  was shifted toward positive voltage from –1.3 V to 3.3 V. The current on-off ratio and SS was deteriorated from  $7.1 \times 10^6$  to  $1.6 \times 10^5$  and from 1.2 V/decade, respectively.

The result is thought to be attributed to the scaling-down effects of OTFTs, i.e. short channel effect [20], which  $V_{TH}$  increases from negative voltage to positive voltage as  $L_C$  decreases. In addition, the hump effects [21] of OTFTs fabricated by the HR shadow mask having  $L_C = 5 \mu m$  enhance the conspicuous change of  $V_{TH}$ , SS and current on-off ratio because the parasitic OTFT with  $L_C = 2.5 \mu m$  is turned on before the main OTFT with  $L_C = 5 \mu m$  as shown in Fig. 3 (b). Figure 3(b) shows that the  $L_C$  has locally abnormal channel of 2.5  $\mu m$  in the OTFT due to the strong electric field around the corner of electrode during  $\mu$ -EDM process.

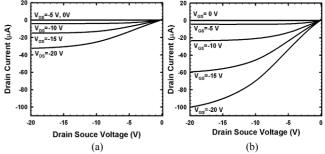

Figure 4 shows the output characteristics of pentacene TFTs with  $L_C$  of (a) 5 µm and (b) 20 µm. For the OTFTs with  $L_C=5$  µm and  $L_C=20$  µm at  $V_{GS}=-10$  V and  $V_{DS}=-20$  V, the saturated drain current ( $I_{DSS}$ ) was  $I_{DSS}=-24$  µA and  $I_{DSS}=-4$  µA, respectively. The measured saturation current ratio of (-24 µA)/(-4 µA) was obtained as 6. The significant improvement of current drivability was achieved from scaling down  $L_C$  from 20 µm to 5 µm at the same  $W_C$  of 150 µm. The result is meaningful because OTFTs of high current drivability consuming the same layout-area are highly demanded to achieve high-resolution flat panel displays based on OTFTs.

### 3. Conclusions

Metal shadow masks with a high aspect ratio (AR>20) using micro-EDM and ECE were proposed for high definition of S/D contacts (L  $\leq$  5 µm and W  $\leq$  150 µm) on organic semiconductors. The fabricated pentacene TFTs with the channel length of about 5 µm showed routinely mobility of 0.49  $\pm$  0.025 cm<sup>2</sup>/Vsec and current on-off ratio of 10<sup>5</sup>. The HR metal shadow masks with AR larger than 20 can be used repeatedly for S/D electrodes deposition due to the structural robustness. The pentacene TFTs by HR shadow masks can meet the required OLED pixel resolution ( $\leq$  100  $\times$  100 µm<sup>2</sup>) as well as high current drivability through the scaling-down of the width of OTFTs [11]. In addition, a batch mode µ-EDM can

FIG 3. (a) Transfer characteristics of pentacene TFTs with  $L_c=5 \ \mu m$  and  $L_c=20 \ \mu m$  in the saturation region (b) a SEM image for the locally abnormal parasitic OTFT with  $L_c=2.5 \ \mu m$ .

Fig. 4. Output characteristics of pentacene TFTs with (a)  $L_c= 20 \ \mu m$  and (b)  $L_c= 5 \ \mu m$  for a fixed channel width of 150  $\mu m$ .

potentially solve a throughput and yield problem of HR metal shadow mask generation.

### Acknowledgements

This work was supported by the contract of ISRC (Inter-University Semiconductor Research-Center) 2002-X-5505 to ETRI (Electronics and Telecommunications Research Institute) and MIC (Ministry of Information and Communication) to carry out the Advanced Technology Project.

### References

- [1] P. Mach, et al., Appl. Phys. Lett., vol. 78, pp. 3592, 2001.

- [2] C. D. Sheraw, et al., Appl. Phys. Lett., vol. 80, pp. 1088, 2002.

- [3] E. A. Huiteman, et al., *Adv. Mater.*, vol.14, pp. 1201, 2002.

- [4] Gerwin H. Gelinck, et al., Nature Mat., vol. 3, pp. 106, 2004.

- [5] P. F. Baude, et al., Appl. Phys. Lett., vol. 82, pp. 3964, 2003.

- [6] Ioannis Kymissis, et al., *IEEE Trans. Electron Devices*, vol. 48, pp. 1060, 2001.

- [7] Hagen Klauk, et al., J. Appl. Phys., vol. 9, pp. 5259, 2002.

- [8] Paul F. Baude, et al., *IEDM Techn. Dig.*, 8. 1. 1, 2003.

- [9] D. J. Gundlach, et al., Appl. Phys. Lett., vol. 74, pp. 3302, 1999.

- [10] G. J. Burger, et al., Sensors and Actuators, A 54, pp. 669, 1996.

- [11] E. Becker, et al., Appl. Phys. Lett., vol. 82, pp. 2712, 2003.

- [12] Changsoon Kim, et al., Appl. Phys. Lett., vol. 80, pp. 4051, 2002.

- [13] Jana Zaumseil, et al., Appl. Phys. Lett., vol. 82, pp.793, 2003.

- [14] C. D. Dimitrakopoulos, et al., Science, vol. 283, pp. 822, 1999

- [15] T. Masaki, K. Kawata, et al., Proc. IEEE Int. Workshop on Micro Electro Mechanical Systems (MEMS'90), pp. 21, 1990.

- [16] M. Datta, et al., IBM J. Res. Develop. vol. 42, pp.655, 1998.

- [17] Ken'ichi Takahata, et al., J. MEMS, vol. 11, pp.102, 2002.

- [18] Masuzawa, et al., Annals of the CIRP, vol. 34, pp. 431, 1985.

- [19] Sung Hun Jin, et al., J. Kore. Phy. Soc., vol. 44, pp.185, 2004.

- [20] L. Torsi, et al., J. Appl. Phys. vol.78, pp.1088, 1995.

- [21] P. Sallagoity, et al., *IEEE Trans. Electron Devices*, vol. 43, pp. 1900, 1996

- [22] Christos D. Dimitrakopoulos, et al., Adv. Mater. vol. 14, pp. 99, 2002.