# Formation of Nanometer-Scale Dislocation Network Sandwiched by Silicon-on-Insulator Layers

Yasuhiko Ishikawa<sup>1</sup>, Kazuaki Yamauchi<sup>1</sup>, Hiroya Ikeda<sup>1</sup>, Yukinori Ono<sup>2</sup>, Masao Nagase<sup>2</sup> and Michiharu Tabe<sup>1</sup>

<sup>1</sup>Research Institute of Electronics, Shizuoka University, 3-5-1 Johoku, Hamamatsu 432-8011, Japan Phone/Fax: +81-53-478-1335, E-mail: y-ishikawa@rie.shizuoka.ac.jp

<sup>2</sup>NTT Basic Research Laboratories, NTT Corporation, 3-1 Morinosato Wakamiya, Atsugi, Kanagawa 243-0198, Japan

## 1. Introduction

Formation of regular array of ultrasmall structures is crucial for nanodevices such as multiple single-electron tunneling junctions. Recently, two groups have reported that a network of line defects (screw dislocations) is formed at the bonding interface of Si (001) wafers when the in-plane crystalline direction is misaligned between the wafers [1,2]. Similar dislocation network has been reported for GaAs [3]. It is important that the spacing between the dislocations can be controlled on the nanometer scale by the in-plane misorientation angle (twist angle) [1].

In this paper, thin silicon-on-insulator (SOI) layer containing a nanometer-scale dislocation network is presented, which is fabricated using wafer bonding of a pair of SOI wafers. Such a dislocation network is effective to form a periodic potential laterally in the SOI layer.

## 2. Fabrication Procedure

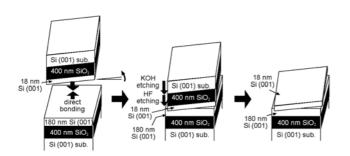

Figure 1 schematically shows the fabrication process of SOI layer containing a dislocation network. As the starting wafer, commercially available SOI (UNIBOND) wafers were used, which had a top p-Si (001) layer (~10 ohm cm) of 205 nm and a buried SiO<sub>2</sub> (BOX) layer of 400 nm. First, two wafers were thermally oxidized to reduce the thicknesses of top Si layers (18 nm and 180 nm). After removing the surface oxide in a diluted HF solution, which produces H-terminated surface, the wafers were bonded at room temperature in air. It is noted that the in-plane crystalline direction was intentionally misaligned, leading to the rotational lattice mismatch. Then, the sample was annealed in N<sub>2</sub> (1000°C, 2h) to stabilize the bonding. Finally, the Si substrate and BOX layer (front side) were etched in a KOH solution and a diluted HF solution, respectively [4]. A dislocation network should be embedded at the bonding interface in the top Si layer.

Two samples with the different twist angle (nominally  $1^{\circ}$  and  $5^{\circ}$ , accuracy  $(\pm 1^{\circ})$  were prepared.

## 3. Results and Discussion

# Transmission electron microscope (TEM) images

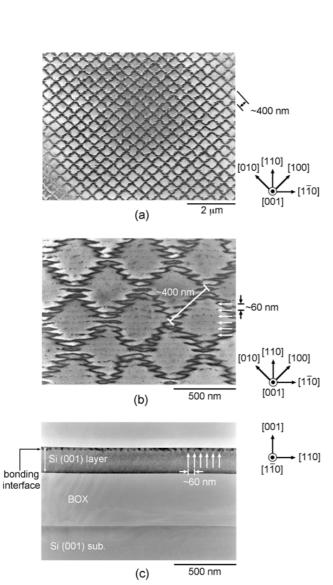

Figure 2(a) shows a typical plan-view TEM image taken for the sample with the twist angle of ~1°. A network of dark lines running along <100> directions (period ~ 400 nm) is clearly seen. A plan-view image with a higher magnification is shown in Fig. 2(b). In addition to the network of <100> dark lines, weak line structures (period ~ 60 nm) running along the  $[1\overline{1}0]$  direction are seen at the inside of squareshaped regions. The cross-sectional TEM image in Fig. 2(c) also showed the presence of the interface structures with the period of ~60 nm. These two types of periodic structures are probably ascribed to screw dislocations and edge dislocations, which are induced at the bonding interface by the in-plane misorientation and the atomic steps on top Si surfaces before the bonding, respectively [1].

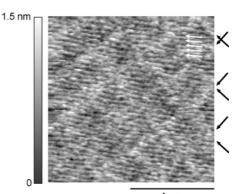

Atomic force microscope (AFM) images

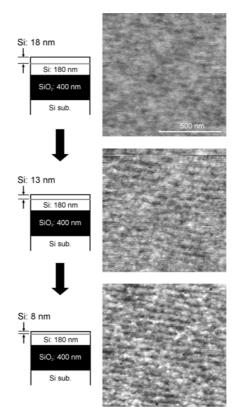

Figure 3 shows a typical AFM image taken on the sample with the twist angle of  $\sim 1^{\circ}$  after thermal oxidation and oxide removal. The thickness of top Si layer was reduced by 5 nm. As in the case of the TEM observations, a network structure with the period of  $\sim 400$  nm is seen together with line structures with the period of  $\sim 60$  nm. As in Fig. 4, these surface corrugations were enhanced with increasing the repetition cycles of the oxidation and oxide removal. This suggests that spatial distribution of lattice strain due to the interface dislocations is present, leading to the spatially modulated oxide growth.

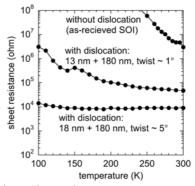

Figure 5 shows sheet resistance by four-point probe method on the macroscopic scale. The sheet resistances for the SOI layers containing the dislocations are much lower than that for an as-received SOI without the dislocations. Possible reasons for the lower resistances are (1) conduction through gap states due to the dislocations and (2) band gap narrowing induced by strain around the dislocations.

## 4. Conclusions

Thin SOI layer containing nanometer-scale dislocation network was shown. The dislocation network would be applicable to form a periodically modulated potential in the lateral direction of SOI layer.

#### Acknowledgements

The authors would like to thank Takeshi Mizuno for his support in experiments. This work was partly supported by a Grant-in-Aid for Scientific Research from the Japan Society for the Promotion of Science.

## References

- [1]J. L. Rouviere, K. Rousseau, F. Fournel and H. Moriceau, Appl. Phys. Lett. 77 (2000) 1135; Appl. Phys. Lett. 80 (2002) 4121.

- [2] R. A. Wind, M. J. Murtagh, F. Mei, Y. Wang, M. A. Hines and S. L. Sass, Appl. Phys. Lett. 78 (2001) 2205.

- [3]F. E. Ejeckam, Y. H. Lo, S. Subramanian, H. Q. Hou and B. E. Hammons, Appl. Phys. Lett. **70** (1997) 1685.

- [4] Y. Ishikawa, S. Makita, J. Zhang, T. Tsuchiya and M. Tabe, Jpn. J. Appl. Phys. 38 (1999) L789.

Fig. 1. Fabrication procedure of SOI layer containing a dislocation network.

1 µm

Fig. 3. Typical AFM image taken for a sample with twist angle of  $\sim$ 1°. Using thermal oxidation and oxide removal, the thickness of top Si layer was reduced by  $\sim$ 5 nm (i.e., 13 nm Si on 180 nm Si).

Fig. 2. Typical TEM images taken for a sample with twist angle of  $\sim 1^{\circ}$ . (a) Plan-view image of the SOI layer, (b) plan-view image with a higher magnification and (c) cross-sectional image.

Fig. 4. AFM images showing the change in the surface morphology during the thinning of top Si layer.

Fig. 5. Sheet resistance versus temperature.