# Optimization Technique of Number of Interconnect Layers and Circuit Area Based on Wire Length Distribution

Takanori Kyogoku, Junpei Inoue, Hidenari Nakashima, Kenichi Okada, and Kazuya Masu

Precision and Intelligence Laboratory, Tokyo Institute of Technology

4259-R2-17 Nagatsuta, Midori-ku, Yokohama 226-8503, Japan

Tel & Fax: +81-45-924-5031 e-mail: kyogoku@lsi.pi.titech.ac.jp

# 1. Introduction

This paper discusses the relationship between Si CMOS ULSI circuit area and the number of interconnect layers on the basis of Wire Length Distribution (WLD); the relationship has a quite important impact because it is directly related to fabrication and manufacturing cost. Using WLD which give a relation between a number of interconnect wire and its lengths, several attempts on chip performance predictions have been reported [1-3].

In this paper, we propose a methodology to optimize a number of interconnect layers and circuit area of Si ULSI.

## 2. Wire Length Distribution

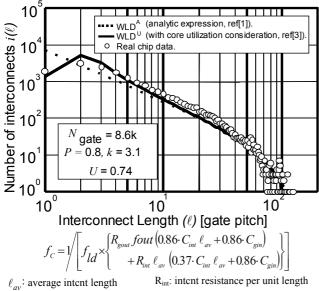

Figure 1 shows a example of Wire Length Distribution (WLD). Circles (O) show data from a macro block of a commercially available 0.13µm technology node CMOS chip. The broken line is the distribution calculated from analytic expression [1], while the solid line is calculated with the core utilization consideration [3]. The parameters required for depicting the distribution are number of gates  $N_{gate}$ , Rent's constants of p and k, and core utilization. In general, complex circuits tend to have large p and small k, while simple circuits have small p and large k. The core utilization (U) is defined as U=(cell area)/(circuit area). The method to determine p, k, and U has been reported by the authors [3]. It is noted that the parameters required for representing WLD are the number of gates N, Rent's constant of p and k, and the core utilization of U. The operation frequency  $f_c$  is estimated by the equation indicated in Fig. 1 [4].

# 3. Relation between Circuit Area and Number of Interconnect Layer

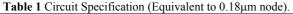

Circuit specification evaluated is summarized in Table 1. The specification is equivalent to 0.18µm technology. One million gates are assumed to be integrated on 10mm<sup>2</sup> area if the core utilization U is 100%; an average gate area is  $3.2 \times 3.2 \mu m^2$ . The circuit area varies depending on the core utilization;  $A_{\text{circuit}} \propto 1/U$ . As interconnect structure, one-tier structure is assumed, *i.e.*, every interconnect layer has the same metal cross section and interlayer dielectric thickness. The assumption of one-tier interconnect is supposed that the following results and discussion are relating to macro blocks of a chip. The values of interconnect capacitance and resistance C<sub>int</sub> and R<sub>int</sub> that are calculated by ref .[5] are dependent on WLD and the core utilization.

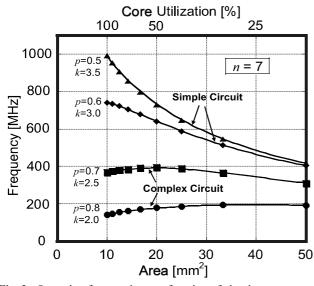

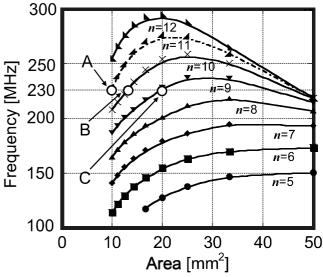

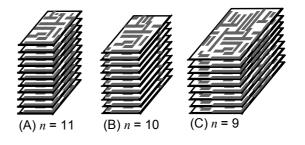

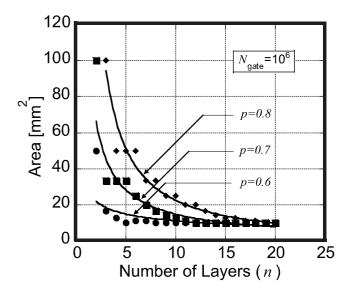

Figure 2 shows a operating frequency  $f_c$  as a function of chip area. For simple circuits (p=0.5 and 0.6),  $f_c$  is improved in the small circuit area region because of the decrease of resistance. On the other hand, the complex circuits (p=0.7 and 0.8) have a optimum area to have maximum  $f_c$  [3]; the decrease of  $f_c$  at small  $A_{circuit}$  is attributed from the increase of line-to-line capacitance, and decrease of  $f_c$  at large  $A_{circuit}$  is attributed from the increase of wire resistance. Figure 3 shows  $f_c$  as a function of  $A_{circuit}$ for complex circuits (p=0.8). Parameter is the number of interconnect layers **n**.  $f_c$  has the maximum value; the reason is the same as in Fig. 2. From Fig. 3, if the required operating frequency is 230MHz, we have several choice as indicated by A, B, and C in Fig. 3; the choice is summarized in Fig. 4. Figure 5 shows the relationship between circuit area  $A_{circuit}$  and the number of interconnect layers *n* to achieve the highest circuit operating frequency. For simple circuits, Acircuit does not change to achieve highest  $f_c$  with increase of n, while  $A_{circuit}$  and n has a close correlation.

Chip cost C is considered to have the relation;  $C \propto (A_{\text{circuit}} \times \mathbf{n}^{\alpha}) / f_c^{\beta}$ , where  $\alpha$  is the process dependent parameter and  $\beta$  may be market determined parameters. One will be able to correlate the WLD which is one of design data information with process and manufacturing cost.

## 4. Conclusions

This paper discusses the relationship between the number of interconnect layers and the circuit area on the basis of the WLD model. It has been shown that there exists the optimum chip area and the number of interconnect layer to achieve the required operating frequency. We have shown the possibility to make a relationship between design data of WLD and process/manufacturing cost. In the advanced process development the co-design concept of circuit design and process development becomes important for cost effective manufacturing.

#### Acknowledgements

This work is partially supported by Grant-Aid for a Scientific Research Projects from the Ministry of Education, Culture, Sports, Science and Technology and STARC.

#### References

- [1] J. A. Davis, et. al., IEEE Trans. on Electron Devices **45-3** (1998) 580.

- [2] H. B. Bakoglu, Circuits, Intreconnections, and Packaging

for VLSI (Addision-Wesley Publishing, 1990).

- [3] H. Nakashima, et. al., Proc. IEEE DATE 2 (2004) 1210.

- [4] S. Takahashi, et. al., IEEE Trans. Electron Devices 48 (2001) 239.

- [5] Jue-Hsien Chern, et. al., IEEE Electron Device Letters 13-1 (1992) 32.

$R_{gout}$ : gate output resistance  $C_{gin}$ : gate input capacitance

$C_{int}$ : intent capacitance per unit length  $f_{id}$ : logic depth

Fig. 1. Wire Length Distribution (WLD) and the prediction of operating frequency  $f_c$ .

| Number of Gates                 | 10 <sup>6</sup>                                  |  |  |

|---------------------------------|--------------------------------------------------|--|--|

| Chip Area @ <b>U</b> =100%      | $10 \text{mm}^2 (10 \mu \text{m}^2/\text{gate})$ |  |  |

| Rent's parameters $(p, k)$      | (0.8, 2), (0.7, 2.5),                            |  |  |

|                                 | (0.6, 3), (0.5, 3.5).                            |  |  |

| Intent cross section            | one-tier multilevel intent                       |  |  |

|                                 | metal cross section: 0.2µm×0.2µm                 |  |  |

|                                 | metal spacing; dependent on $U$                  |  |  |

|                                 | ILD thickness: $0.2\mu m (\epsilon = 3.9)$       |  |  |

| $R_{gout}, C_{gin}, and f_{ld}$ | $4 \text{ k}\Omega$ , 2.1fF, and 20              |  |  |

Fig. 2. Operating frequencies as a function of circuit area.

Fig. 3. Operating frequencies for complex circuit (p=0.8).

|                                   | А                 | В                   | С                 |  |

|-----------------------------------|-------------------|---------------------|-------------------|--|

| Operating freq. $f_c$             | 230 MHz           |                     |                   |  |

| Circuit Area A <sub>circuit</sub> | $10 \text{ mm}^2$ | $12.5 \text{ mm}^2$ | $25 \text{ mm}^2$ |  |

| # of intent layers n              | 11                | 10                  | 9                 |  |

**Fig.4.** Choices of the circuit area and the number of wiring layers under the same operating frequency condition.

**Fig.5.** The relationship between circuit area and the number of layers to achieve the highest circuit operating frequency.