# Material Characterization of Metal-germanide Gate Electrodes Formed by FUGE (Fully Germanided) Process

Yoshinori Tsuchiya, Masato Koyama, Junji Koga, and Akira Nishiyama

Advanced LSI Technology Laboratory, Toshiba Corp.

8, Shinsugita-cho, Isogo-ku, Yokohama 235-8522, Japan.

TEL: +81-45-770-3691 FAX: +81-45-770-3578 E-mail: yoshinori3.tsuchiya@toshiba.co.jp

### 1. Introduction

Fully silicided gate (FUSI) technology is the prime candidate for dual metal gate due to its compatibility with conventional CMOSFET fabrication process [1]. On the other hand, silicides with band edge work functions are necessary to control threshold voltage for bulk CMOS devices. As for PMOS, platinum silicide reveals the highest effective work function ( $\Phi_{eff}$ ) (~ 4.9 eV) [2], which is slightly small to achieve low V<sub>th</sub>. Recently, fully NiGe gate has been reported as a new PMOS gate candidate with  $\Phi_{eff}$ corresponding to valence-band edge (*Ev*) [3]. In order to develop bulk CMOS devices with fully germanided gate (FUGE), however, material characterization has not been sufficient yet, such as the work function values for alternative metal germanides and the thermal stability through the conventional back-end processing.

In this paper,  $\Phi_{\text{eff}}$  values for metal (Pt, Ni, Ta, Er) germanides prepared by FUGE process were systematically investigated for the first time. We found these germanides reveal work function values covering NMOS, midgap and PMOS gates on SiO<sub>2</sub>. NiGe<sub>x</sub> MIS stack is fully sustainable up to 600°C, if NiGe<sub>x</sub> is capped with a tungsten film. FUGE electrodes are successfully compatible with the HfSiON gate dielectric. It is found that Fermi level pinning (FLP) phenomenon, which limit the applicability of FUSI technology to Hf-based dielectrics [2], can also affect  $\Phi_{\text{eff}}$ values at FUGE/HfSiON.

#### 2. Experimental

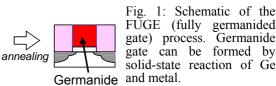

Germanide gated MIS capacitors were fabricated on p-type Si(100) substrate with FUGE process, which is similar to FUSI process (Fig. 1). Ge and metal (Pt, Ni, Ta, Er) layers were sputtered consecutively on thermally grown SiO<sub>2</sub> or HfSiON/SiO<sub>2</sub>. Then, the specimens were annealed at 400-800°C for 60 s in N<sub>2</sub> atmosphere to form germanide gates. C-V characteristics were measured after forming gas anneal at 400°C for 30 min. In some samples, tungsten layers were sputtered subsequently after metal formation.

#### 3. Results and Discussion

## <u>A. $\Phi_{eff}$ value of germanide on SiO<sub>2</sub></u>

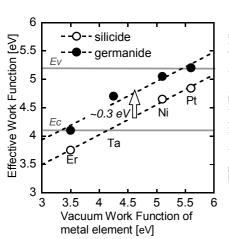

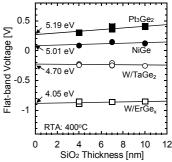

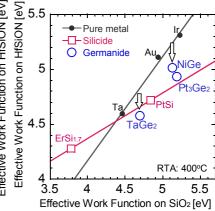

Fig. 2 shows that the flat-band voltages (V<sub>fb</sub>) of germanide gate MOS capacitors change depending on the constituting metal elements. The maximum difference of V<sub>fb</sub> is 1.2 V, and the  $\Phi_{eff}$  modulation range covers the energy of Si bandgap, corresponding to conduction-band edge (*Ec*) (ErGe<sub>x</sub>: 4.05 eV) and *Ev* (Pt<sub>3</sub>Ge<sub>2</sub>: 5.19 eV) as well as that closed to Si-midgap (TaGe<sub>2</sub>: 4.70 eV) (Fig. 3). The realization of  $\Phi_{eff}$  value corresponding to *Ev* with FUSI is quite difficult, because the  $\Phi_{eff}$  value of PtSi is 4.9 eV, which contains the highest vacuum work function ( $\Phi_{vac}$ ) metal (Fig. 4). The  $\Phi_{eff}$  values of germanides are about 0.3 eV higher than those of silicides, realizing high  $\Phi_{eff}$  values near *Ev* (Ni and Pt germanides).

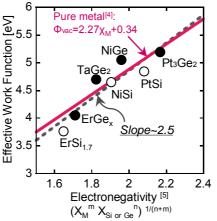

It is well known empirically that  $\Phi_{vac}$  values of pure metals are linearly related to Pauling's electronegativity  $(\chi_M)$ ,  $\Phi_{vac}=2.27\chi_M+0.34$  [4]. The  $\Phi_{eff}$  and  $\chi_M$  for germanides and silicides are related in the same way as  $\Phi_{vac}$ and  $\chi_M$  for pure metals, under the assumption that the  $\chi_M$  is a geometric mean of metal and Ge or Si (Fig. 5). This result shows the  $\Phi_{eff}$  values of germanides and silicides are strongly influenced by electron binding energies of elements. We conclude that larger electronegativity of Ge than Si results in higher  $\Phi_{eff}$  values of germanides than silicides.

#### <u>B. Thermal stability of germanide for PMOSFET and</u> <u>W-cap layer effect</u>

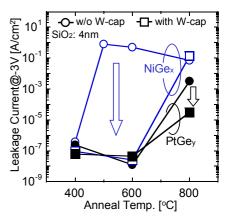

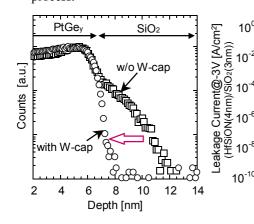

We also investigated the thermal stability of germanide gate electrodes with  $\Phi_{eff}$  values for low V<sub>th</sub> PMOS. The thermal stability through back-end processing, comparable to NiSi thermal stability, is needed for "gate last" FUGE process. A significant increase in gate leakage current was observed in the case of NiGe<sub>x</sub> gate electrode after 500°C annealing, presumably owing to the lower melting point of germanide than silicide (Fig. 6). On the other hand,  $PtGe_v$ gate electrode has sufficient thermal stability; low leakage current was maintained until after 600°C annealing. W-cap layer effectively suppresses the increase in gate leakage current after 600°C annealing of NiGex gate electrode, indicating that W/NiGe<sub>x</sub> is also a candidate gate structure. W-cap layer also inhabits PtGe<sub>v</sub> penetration into SiO<sub>2</sub> (Fig. 7), which is the cause of increase in gate leakage current after 800°C annealing.

### <u>C. Applicability of Germanide/HfSiON</u> gate stacked structure

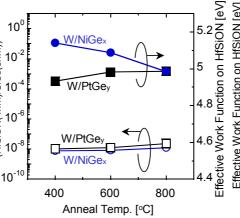

Fig. 8 shows that W-capped Ni and Pt germanides on HfSiON maintain low gate leakage current and stable  $\Phi_{eff}$  values even after 800°C annealing, indicating superior compatibility to the cases on SiO<sub>2</sub>. The  $\Phi_{eff}$  values of germanides on HfSiON decrease to Si-midgap compared to those on SiO<sub>2</sub>, which is similar to the silicide cases (Fig. 9). This result indicates that FLP occurs at germanide/HfSiON interfaces in the same manner as at silicide/HfSiON. However,  $\Phi_{eff}$  values corresponding to near Ev (>4.9 eV) are still achieved at NiGe<sub>x</sub> and PtGe<sub>y</sub>/HfSiON interfaces, in contrast to midgap  $\Phi_{eff}$  value of PtSi/HfSiON system (Fig. 9). Therefore, germanide gate has a potential ability for low V<sub>th</sub> PMOS with HfSiON gate dielectric.

#### 4. Conclusions

We have investigated  $\Phi_{\text{eff}}$  values and thermal stabilities of germanide gate electrodes formed by FUGE process. It is found that  $\Phi_{\text{eff}}$  values of germanides cover the energy of Si bandgap, and are higher than those of silicides. The  $\Phi_{\text{eff}}$  values corresponding to Ev, desired for low V<sub>th</sub> PMOS, were realized even on HfSiON. In addition, W-cap layer effectively improves thermal stability of germanides and makes Ni germanide gate electrode sufficiently stable for the back-end processing. In conclusion, Ni and Pt germanides are promising for PMOS "gate last" metal gate electrode.

#### 5. Acknowledgment

We would like to express sincere thanks to Mr. K. Nakajima, and Mr. M. Sato for their valuable discussion 1 and cooperation. 0.8

#### References

- [1] J. Kedzierski et al., IEDM Tech. Dig., (2003), p. 315. 0/0

- [2] M. Kadoshima et al., SSDM Ext. Abst., (2004) P.466.

- [3] H. Huang et al., IEDM Tech. Dig., (2003), p.319.

- [4] W. Gordy et al., Phys. Rev. 24, (1956) 439.

- [5] Y.C. Yeo et al., J. Appl. Phys. 92, (2002) 7266.

Fig. 4:  $\Phi_{eff}$  value vs  $\Phi_{vac}$  value of the metal element for germanides and silicides. PtSi and ErSi17 were formed by co-sputtering of metal and Si, and NiSi formed by FUSI process.

Metal

1 + + +

Ge

max

capacitors.

0.6

0.4

0.2

0

W/Fr

-2

-1

Fig. 2: C-V characteristics of ger-

manide/SiO<sub>2</sub> gate stacked MOS

ר ר

RTA: 400°C

Pt<sub>3</sub>Ge

0

Gate Voltage [V]

Fig. 3: Flat-band voltage of germanide gated MOS capacitors as a function of oxide thickness.

Fig. 6: Dependence of gate leakage current of germanide MIS capacitor with  $SiO_2$  on annealing temperature with or without W-cap.

Fig. 7: Backside SIMS depth profiles of Ge after 800 °C annealing, in PtGey/SiO2 with or without W-cap layer.

Fig. 8: Dependence of gate leakage current and  $\Phi_{eff}$  value of germanide/HfSiON on annealing temperature.

Fig. 9:  $\Phi_{eff}$  value on HfSiON vs SiO<sub>2</sub>. Pure metal gate electrodes were formed by sputtering.