# Area Selective Flash Lamp Post-Deposition Annealing of High-k Film Using Si Photo Absorber for Metal Gate MISFETs with NiSi Source/Drain

Takeo Matsuki, Isamu Nishimura\*, Yasushi Akasaka, Kiyoshi Hayashi\*\*, Masataka Noguchi\*\*\*, Koji Yamashita\*\*\*\*, Kazuyoshi Torii\*\*\*\*\*, Naoki Kasai\*\*\* and Yasuo Nara

> Research Department 1, Semiconductor Leading Edge Technologies, Inc. 16-1 Onogawa, Tsukuba-shi, Ibaraki-ken, 305-8569, Japan Phone: +81-29-849-1187 E-mail: matsuki@selete.co.jp

## 1. Introduction

Post-deposition annealing (PDA) process and its integration in LSI process are important items for high perform-ance high-k gate stack MISFETs. In the "gate first" high-k with conventional gate MISFETS fabricated and source/drain formation sequence, PDA is indispensable to suppress the mobility reduction [1]. The PDA temperature should be as high as that of source/drain activation annealing, while inter-diffusion between high-k and interfacial layer should be minimized [2]. In order to overcome this difficulty, ultra-thin SiON interfacial layer with precise nitrogen profile control is required [3]. In contrast, in the "gate last" MISFETs, "damascene" or "replacement", PDA temperature and its thermal budget are restricted by the NiSi on source/drain (S/D), which might cause problems such as high amount of residual impurity and defects in high-k film.

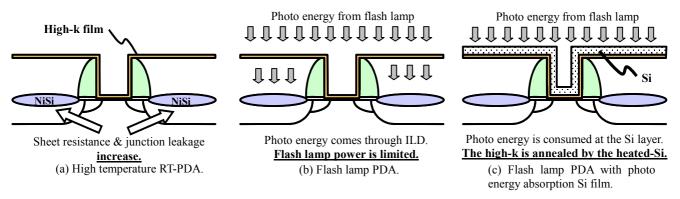

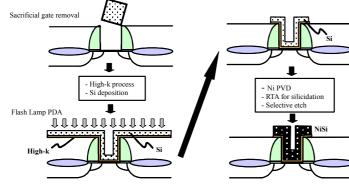

In this work, we propose a replacement silicide gate process with an area selective PDA process that is a combination of flash lamp anneal [4] and a Si photo absorption layer to prevent photo energy transmission to the NiSi on S/D.

### 2. Flash Lamp PDA with Si Photo Energy Absorber

Flash lamp PDA (FL-PDA) is a very short time photo exposure annealing process, and can achieve high temperature annealing with low thermal budget. It was reported that CV hysteresis in TiN/HfAlOx stacked structure was re-duced by using FLA as PDA [5]. However, even with FLA, NiSi performance on S/D might be degraded (Fig. 1-(b)). So we propose, here, FL-PDA with Si photo energy absorption layer (Si-PEAL) to prevent the degradation (Fig. 1-(c)

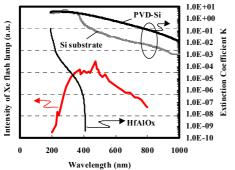

Figure 2 shows typical intensity spectrum of a Xe flash lamp and extinction coefficient K of the HfAlOx, a sputter-deposited-Si (PVD-Si), and Si substrate. Most part of the energy of the light is absorbed by the Si film or Si substrate. Therefore, in the proposed PDA method as shown in Fig.1-(c), HfAlOx is heated mainly by the Si film, while NiSi on the S/D receives much reduced energy from flash lamp

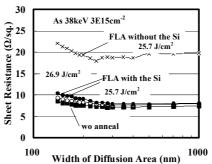

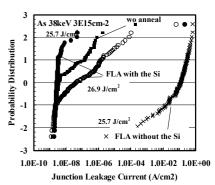

To investigate the effect of the Si layer above NiSi on S/D, sheet resistance and junction leakage of diffusion area was evaluated. It was confirmed that the Si-PEAL was effective to suppress an increase in the resistance of the diffusion area (Fig. 3). Junction leakage current increase was also suppressed by the Si-PEAL (Fig. 4). If the energy density of the flash was too high, the distribution became broad. The higher leakage current and large distribution is presumably due to the roughness at the interface between the silicide and Si substrate which could be formed by the phase change of the NiSi at high temperature [6].

## 3. Device fabrication

Figure 5 shows the concept of replacement NiSi gate MISFET fabrication flow. High-k film is formed after sacrificial gate removal, and annealed after Si deposition.

A "Gate-Last" structure was used to evaluate FET properties with NiSi/HfAlOx gate stack [7]. Gate insulator and electrode were formed after the source/drain formation in a non-self-aligned manner against the source/drain. The Si layer was deposited by PVD. A HfAlOx (2.5nm) was deposited by ALD at 300 °C using HfCl<sub>4</sub>, TMA and H<sub>2</sub>O as precursors on a interfacial SiO<sub>2</sub> (1nm). As a Si-PEAL, a Si film was deposited by sputtering on the HfAlOx. In the FL-PDA, the wafer was preheated at 220 °C, and energy density of the flash was set at 24.5 J/cm<sup>2</sup>, which is low enough to suppress NiSi degradation on S/D. FL-PDA was performed in  $N_2$  atmosphere. For a comparison, samples applied rapid thermal (RT) -PDA at 1050 °C for 1 sec (Fig. 1-(a)) and FL-PDA without Si-PEAL (Fig. 1-(b)) were also fabricated. The Si layer was patterned after FL-PDA and then fully silicided by Ni-PVD, silicidation annealing and selective removal of un-reacted Ni.

## 4. Results and Discussion

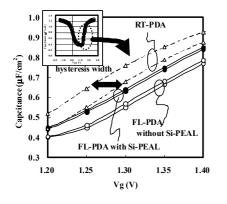

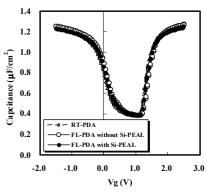

C-V curves of the samples applied the FL-PDA with Si-PEAL was compared with those of the high temperature RT-PDA and the FL-PDA without Si-PEAL (Fig. 6). There observed no obvious hump or shift, indicating that the amount of interface trap or fixed charge can be reduced by FL-PDA as small as those by high temperature RT-PDA. Moreover, the C-V hysteresis width can be reduced by FL-PDA to 1/8-1/10 that by RT-PDA (Fig. 7).

The FL-PDA with Si-PEAL showed better PBT immunity than the FL-PDA without Si-PEAL and the RT-PDA (Fig. 8). PBTI is believed to be due to the electron trapping to pre-existing defects in the high-k layer [8]. By using Si-PEAL, HfAlOx was heated from the top, which is probably effective to suppress the inter-diffusion between high-k and interfacial  $SiO_2$ , leading to the reduction of the defects in the high-k.

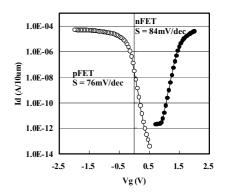

Id-Vg characteristics of the NiSi/HfAlOx MISFET using FL-PDA with Si-PEAL showed no obvious degradation in subthreshold characteristics (Fig. 9).

### 5. Conclusion

We proposed an area selective flash lamp PDA using Si photo energy absorption layer to apply an enough thermal treatment to the high-k layer without degrading the NiSi on S/D. Charge trapping was successfully reduced by suppressing inter-diffusion owing to low thermal budget of FLA and heating from the top Si layer.

### References

- [1] W. S. Kim et al., Jpn. J. Appl. Phys., 43 (2004) 1860

- [2] R. Mitsuhashi et al, Ext. Abst. IWGI2003 (2003) 150

- [3] R. Mitsuhashi et al, Ext. Abst. SSDM (2004) 34

- K. Yamashita et al, ISSM Proc. (2003) 153

- 5] T. Matsuki et al, MRS Sym. Proc., 811 (2004) 87

- [6] A. Lauwers et al, Microelectronic Eng., 50 (2000) 103

[7] T. Matsuki et al, 2004ICMTS Proc. (2004) 105

- [8] K. Onishi et al., IEEE Trans. Electron Devices, **50** (2003) 1517 Present affiliation : \*Rohm, \*\*Renesas, \*\*\*NEC, \*\*\*\*Sanyo, \*\*\*\*\*Hitachi

Fig. 1 Schematic diagrams of the feature of high temperature PDA, FL-PDA, and FL-PDA with a Si photo absorption layer.

Fig. 2 A Xe flash lamp intensity spectrum and extinction coefficient spectra of HfAlOx and Si.

Fig. 3 Energy absorption layer effect in the sheet resistance of the NiSi diffusion

Fig. 4 Energy absorption layer effect in junction leakage of the NiSi diffusion area.

Fig. 5 Concept of fabrication flow of replacement NiSi gate MISFETs with FL-PDA using Si photo energy absorption layer.

1.00 □ RT-PDA FL-PDA without Si-PEA FL-PDA with Si-PEAI  $\Delta V t \left( V \right)$ 0.10 0.01 1000 10 100 Stress time (sec)

Fig. 7 C-V hysteresis width of the Fig. 8 PBTI characteristics of the NiSi/HfAlOx nMISFETs. NiSi/HfAlOx nMISFETs.

Fig. 6 C-V curves of NiSi/HfAlOx MISFETs with FL-PDA (with/without Si-PEAL) and RT-PDA.

Fig. 9 Id-Vg characteristics of the NiSi/HfAlOx nMISFETs using the FL-PDA with Si-PEAL. Leff=0.7µm