# Influences of Activation Annealing on Characteristics of Ge p-MOSFET with ZrO<sub>2</sub> Gate Dielectric

Yoshiki Kamata, Yuuichi Kamimuta, Tsunehiro Ino, Ryosuke Iijima, Masato Koyama, and Akira Nishiyama

Advanced LSI Technology Laboratory, Corporate R&D Center, Toshiba Corporation 8, Shinsugita-Cho, Isogo-Ku, Yokohama 235-8522, Japan TEL+81-45-770-3691 FAX+81-45-770-3578 E-mail: yoshiki.kamata@toshiba.co.jp

## 1. Introduction

Since the aggressive scaling of MOS devices leads to the fundamental limit of SiO<sub>2</sub> as the gate dielectrics, high-quality deposited high-k materials have been developing for the replacement of  $SiO_2$ . On the other hand, Ge is one of the attractive materials as the substrate of MOSFET due to its higher mobility compared to Si [1]. In particular p-channel Ge FET is desirable since bulk hole mobility of Ge is four times as high as that of Si and it can be enhanced furthermore by strain [2]. In order to realize both thin EOT and high drive current, high-k/Ge is one of the attractive combination and promising electrical characteristics on the high-k/Ge system have been reported recently [3]. Furthermore owing to the low-temperature dopant activation in the Ge substrate [3], high-k materials that react with Si at temperatures as high as 1000°C could be re-examined as the prospective candidates. We have already shown that ZrO<sub>2</sub>/Ge gate stacks are more preferable to realize both thin EOT and low  $J_g$  than  $HfO_2/Ge$  ones [4, 5]. Although  $ZrO_2/Ge$ gate stacks have been already reported [3–7], so far little has been reported on the influences of activation annealing on Ge MOSFET device characteristics. The purpose of this work is to clarify the influence of the activation annealing on the characteristics of Ge p-MOSFET with ZrO<sub>2</sub> gate dielectric. Particularly, we address the issue of (i) interfacial layer (I. L.) thickness, (ii) gate leakage current, (iii) band alignment and (iv) activation annealing of p+/n-junction formation. Ge p-MOSFET performance is demonstrated with the optimized temperature.

### 2. Experimental

ZrO<sub>2</sub> was deposited by sputtering on (100) n-type Ge substrate (Sb: 0.05 Ωcm) which were cleaned with DHF (1%) and DI water rinse. Impurity activation annealing was performed at from 400 to 800°C for 30 min in N<sub>2</sub> after making gate electrode. Molybdenum was used for the gate electrode of MOS capacitor and p-MOSFETs. BF<sub>2</sub><sup>+</sup> (5 x 10<sup>15</sup> cm<sup>-2</sup>, 50 keV) was implanted to form p+/n-region. Forming gas annealing (H<sub>2</sub>: 10%) was carried out for MOS capacitor and p-MOSFET at 350°C for 30 min. For the band gap measurement, thick ZrGeO insulators of 100 nm on Si substrate deposited by sputtering with Zr and Ge target were used for the reflection electron energy loss spectroscopy (REELS).

## 3. Results and Discussion

## (i) Physical influences of annealing

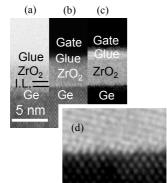

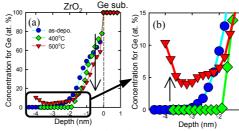

Figures 1(a)–(d) show high-resolution cross-sectional transmission electron microscopy (HR-XTEM) images for the samples before and after annealing in N<sub>2</sub>. The I. L. thickness decreased by the interdiffusion with  $ZrO_2$  after 500°C annealing in N<sub>2</sub>. The complete absence of the interfacial layer after 500°C annealing could be confirmed by the fact that the crystal lattice of  $ZrO_2$  reached down to the surface of the Ge substrate, as shown in Fig. 1(d). As a result, Ge was incorporated into  $ZrO_2$  above 500°C (Fig. 2), in which Ge concentration relative to Zr was about 15% inside high-k films. Since electrical properties could change as a result of the Ge incorporation into  $ZrO_2$ , we next investigated the influences of annealing on the electrical characteristics at the temperature as low as that needed to activate the dopant.

## (ii) $J_{g}$ band alignment and activation of p+/n-junction

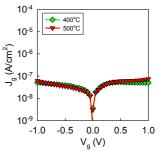

Figure 3 shows that gate leakage current density  $(J_g)$  remained as small as  $1 \times 10^{-7}$  A/cm<sup>2</sup> after annealing in N<sub>2</sub>. Figures 4 show that

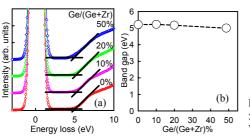

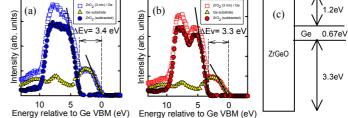

band gaps ( $E_g$ ) derived from REELS were almost the same up to Ge/(Ge+Zr)=50%. Since Ge/(Ge+Zr) ratio in ZrO<sub>2</sub> after 500°C annealing in N<sub>2</sub> was about 15%,  $E_g$  of the sample is also expected to be the same as as-deposited one. Figures 5 show that valence band offset ( $\Delta E_v$ ) between Ge incorporated ZrO<sub>2</sub> and Ge substrate, which is derived from valence XPS spectra of high-k and the substrate.  $\Delta E_v$  was almost the same of 3.3 eV before and after 500°C annealing in N<sub>2</sub>. Combining these results, band alignment didn't change after Ge incorporation into ZrO<sub>2</sub> film as depicted in Fig. 5(c). This is one of the reasons why no large gate leakage increase was observed with PDA [4, 5].

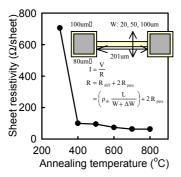

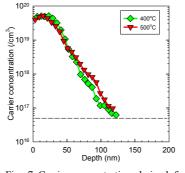

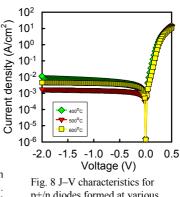

Next we investigated the activation of p+/n-junction. Figure 6 shows sheet resistivity ( $\rho_{sh}$ ) derived from the regression for the sample measured by two-terminal method with different width as the inset in Fig. 6. From  $\rho_{sh}$  results, boron is expected to be highly activated above 400°C [3]. As shown in Fig. 7, the results of spreading resistance analyses (SRA) indicated the low temperature dopant activation [8]. The peak concentration ( $C_m$ ) of electrically active dopant was 5x10<sup>19</sup> cm<sup>-3</sup>. Figure 8 shows J-V characteristics for the p+/n-junction. Samples annealed from 400°C to 600°C showed the good rectifying diode characteristics with the reverse leakage current below 10 mA/cm<sup>2</sup>. The ratio between the forward biased current density ( $J_f$ ) and the backward biased current density ( $J_b$ ) reached around four orders of magnitude at the sample annealed at 500°C. It should be noted that temperature of 400°C is high enough for the activation of implanted dopant.

#### *(iii) Characteristics of p-MOSFET*

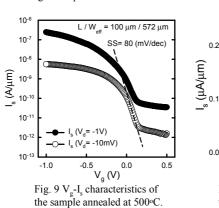

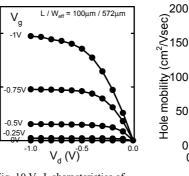

Below 500°C, the effect of annealing temperature on transistor characteristics was small: good cut-off characteristics were obtained (I<sub>s</sub>-V<sub>g</sub>, I<sub>s</sub>-V<sub>d</sub> for 500°C are shown in Figs. 9, 10). S-factor was as small as 80 mV/decade. Hole mobility ( $\mu_h$ ) of the ZrO<sub>2</sub>/Ge gate stacks annealed at 500°C slightly increased compare to that at 400°C (Fig. 11). It was as high as 100 cm<sup>2</sup>/Vsec at maximum and comparable to the reported hole mobility of HfO<sub>2</sub>/Ge gate stacks with interfacial GeON layer [9]. Considering the complete disappearance of I. L. at 500°C, the mobility enhancement of the sample annealed at 500°C may indicate that the direct high-k/Ge interface is superior to the ZrO<sub>2</sub>/I. L. (composed of GeO<sub>x</sub>)/Ge interface.

### 4. Conclusion

$ZrO_2/Ge$  gate stacks retained the structural integrity at Ge p-MOSFET fabrication process temperature of as high as 500°C. Band alignment for Ge incorporated  $ZrO_2$  film on Ge didn't change compared to  $ZrO_2$  on Ge. Good rectifying diode junction characteristics led to the promising p-MOSFET characteristics. Hole mobility of direct high-k/Ge gate stacks was as high as 100 cm<sup>2</sup>/Vsec.

#### References

[1] S. M. Sze, *Physics of semiconductor* devices 2<sup>nd</sup> ed. (Wiley, New York, 1981)

- [2] M. V. Fischetti et al., J. Appl. Phys. 80, 2234 (1996)

- [3] C. O. Chui et al., IEDM Tech. Dig. 2002, p.437

- [4] Y. Kamata et al., Ext. Abst. SSDM (2004) p.36

- [5] Y. Kamata *et al.*, Jpn. J. Appl. Phys. **4B**, 2323 (2005)

- [6] H. Kim et al., Appl. Phys. Lett. 83, 2647 (2003)

- [7] D. Chi et al., J. Appl. Phys. 96, 813 (2004)

- [8] C. O. Chui et al., Appl. Phys. Lett. 83, 3275 (2003)

- [9] N. Wu et al., IEEE Elec. Dev. Lett. 25, 631 (2004)

Fig. 1 HR-XTEM images of ZrO<sub>2</sub> / Ge (a)as-deposited, annealed at (b) 400°C and (c) 500°C. (d) is enlargement of (c).

Fig. 4 (a) REELS spectra and (b) extracted  $E_{g}$

Fig. 2 (a) Depth profile of Ge atoms in ZrO<sub>2</sub> layer and (b) its enlargement. With PDA, Ge profile decreases in the interface region in (a) and Ge content in ZrO2 increases after annealing at 500°C.

Fig. 3 J<sub>g</sub> of Mo / ZrO<sub>2</sub> 10nm / n-Ge.

Fig. 5 Valence XPS spectra for ZrO<sub>2</sub> film on Ge (a) before and (b) after annealing at 500°C. The onset of valence spectra corresponds to valence band maximum (VBM). Valence band offset ( $\Delta$  Ev) between ZrO<sub>2</sub> and Ge is derived from subtracting the spectrum of Ge substrate (triangle) from that of ZrO<sub>2</sub> on Ge (square). (c) Schematic diagram indicates band alignment for Ge incorporated ZrO<sub>2</sub> film on Ge.

Fig. 6 Sheet resistivity  $(\rho_{\text{sh}})$  dependence on anneal temperature.  $\rho_{\text{sh}}$  is derived from regression using 2-terminal measurement of the rectangle sample with different width.

Fig. 7 Carrier concentration derived from spreading resistance analyses (SRA). Carrier concentration of substrate of 5x1016 (/cm<sup>3</sup>) is also shown by dashed line.

p+/n diodes formed at various annealing temperatures.

Fig. 10 V<sub>d</sub>-I<sub>s</sub> characteristics of the sample annealed at 500°C.

0.2

0.0