# B-6-2

## Modeling of Body Factor and Subthreshold Swing in Short Channel Bulk MOSFETs

Arifin Tamsir, Masumi Saitoh, Gen Tsutsui and Toshiro Hiramoto

Institute of Industrial Science, University of Tokyo, 4-6-1 Komaba, Meguro-ku, Tokyo 153-8505, Japan Phone: +81-3-5452-6264, E-mail: arifin@nano.iis.u-tokyo.ac.jp

#### 1. Introduction

When designing a variable-threshold-voltage CMOS (VTCMOS) [1], the body factor  $\gamma$  defined by  $dV_{th}/dV_{bs}$  is one of the most important parameters and a sufficiently large value of  $\gamma$  is required [2]. The relation between subthreshold swing (S) and  $\gamma$  in a long channel device is given by [2]:

$$S = 60(1+\gamma) \tag{1}$$

In a short channel device, however, this simple relation no longer holds and a new model is strongly required. An analytical expression of relation between  $\gamma$  and S in short channel bulk MOSFETs has been reported recently [3]. However, it only discussed at low drain voltage ( $V_{dd} = 0.1$ V), the models were complex, and the physical characteristics hidden in  $\gamma$  and S are still unclear.

In this paper, we present simple empirical models of  $\gamma$ and S at low and even high drain voltage. The models are verified by comparing with results of 2D device simulation [4]. The relation between  $\gamma$  and S in a short channel device at the presence of high drain voltage is derived for the first time.

### **Proposed Models**

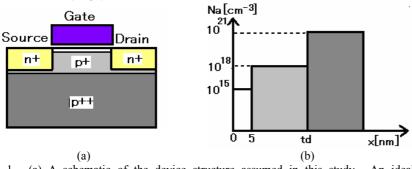

Fig. 1 shows the device structure assumed in this work [5].  $t_d$  corresponds to the depletion width and  $\gamma$  is changed by varying  $t_d$ . We use a capacitance network model shown in Fig. 2 [6].  $C_G$ ,  $C_B$ ,  $C_D$  and  $C_S$  are gate, substrate, drain, and source to channel capacitances for unit width, respectively. When the channel length becomes shorter,  $C_G/L$  and  $C_B/L$  (unit area capacitance) start to decrease by the short channel effect (SCE):

$$C_G/L = (C_{G0} - \alpha/L^2)$$

(2)  $C_B/L = (C_{B0} - \beta/L^2)$  (3)

where  $C_{G0}$  and  $C_{B0}$  are gate and substrate capacitance per unit area in a long channel device, respectively, which are shown as

$$C_{G0} = \varepsilon_{OX} / t_{ox\_ele} \qquad (4) \qquad C_{B0} = \varepsilon_{Si} / t_d \quad , \tag{5}$$

$\alpha$  and  $\beta$  are parameters caused by SCE, L is the gate length, and  $t_{ox}$  ele is electrical equivalent thickness of the gate oxide [7]. We assume that in a short channel the effect of  $\alpha$  can be ignored due to very close distance between gate and channel, while  $\beta$  should be taken into account.

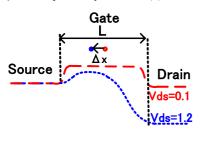

We also consider that DIBL causes the maximum potential barrier to move from the center of the channel towards the source as shown in Fig. 3, and consequently  $C_D$ decreases and  $C_S$  increases as,

$$C_S = k\varepsilon_{Si} t_d x_j / (L/2 - \Delta x)^2$$

(6)

$$C_D = k\varepsilon_{Si} t_d x_i / (L/2 + \Delta x)^2 \tag{7}$$

where  $\Delta x$  is the distance shifted toward the source by DIBL, k is a fitting parameter, and  $x_i$  is metallurgical depth.

# 3. Derivation of Body Factor and Subthreshold Swing

$\gamma$  is determined approximately by  $C_B/C_G$ , which means the ratio of the effect of substrate bias on the channel to that of the gate voltage. On the other hand, S is determined by

the ratio of the total capacitance of the channel to  $C_G$ . This assumption is valid in both long and short channel:

$$\gamma = \frac{C_B}{C_C} \approx \frac{C_{B0}}{C_{C0}} - \frac{\beta}{C_{C0}L^2} = \gamma_0 - \Delta\gamma \tag{8}$$

$$\gamma = \frac{C_B}{C_G} \approx \frac{C_{B0}}{C_{G0}} - \frac{\beta}{C_{G0}L^2} = \gamma_0 - \Delta\gamma$$

$$S' = \frac{S}{60} = \frac{(C_B + C_G + C_S + C_D)}{C_G} \cong \left(1 + \frac{C_{B0}}{C_{C0}}\right) + \frac{(C_S + C_D)/L - \beta/L^2}{C_{C0}} = S_0 + \Delta S$$

(8)

where  $\Delta \gamma$  and  $\Delta S$  are the differences of  $\gamma$  and S between long and short channel devices. By substituting eq. (4), (6), (7) into (8) and (9), we obtain  $\Delta \gamma$  and  $\Delta S$  as follows.

$$\Delta \gamma = A / L^2 \tag{10}$$

$$\Delta S = \frac{Bt_d}{L} \left( \frac{1}{(L/2 - \Delta x)^2} + \frac{1}{(L/2 + \Delta x)^2} \right) - \frac{A}{L^2}$$

(11)

where  $A = \beta t_{ox ele} / \varepsilon_{ox}$  and  $B = k t_{ox ele} x_i \varepsilon_{Si} / \varepsilon_{ox}$ . The model is fitted to the device simulation results. The device parameters are based on hp90 LSTP devices of 2003 ITRS [8]. A, B, and  $\Delta x$  are 210 nm<sup>2</sup>, 144 nm<sup>2</sup>, and 7.5 nm, respectively.

#### Results and Discussion

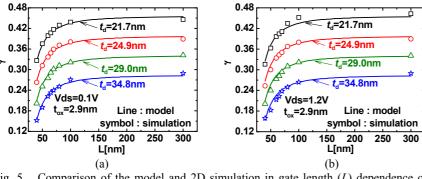

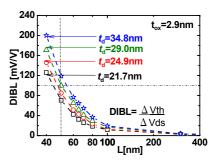

Figs. 4 and 5 show gate length dependence of S and  $\gamma$ , respectively. The model and the simulation are compared, and a good agreement is obtained. S increases and y decreases by SCE. When applying high drain voltage, S is severely degraded due to DIBL as shown in Fig. 4(b). However, it is interesting to note that the degradation of  $\gamma$ does not depend on DIBL, as shown in Figs. 5 (a) and (b). This is because according to eq. (8)  $\gamma$  is not related to  $C_D$  and  $C_{S}$ . Simulated gate length dependence of DIBL is shown in Fig. 6. The value of DIBL reaches 200 mV/V at L = 40 nm. Therefore, it is shown that our model is valid in the range where DIBL < 200 mV/V.

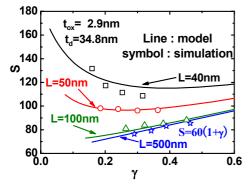

Finally, the relation between S and  $\gamma$  in a short channel device at high drain voltage is derived as a simple form:

$$S = 60 \left[ 1 + \gamma + \frac{Bt_d}{L} \left( \frac{1}{(L/2 - \Delta x)^2} + \frac{1}{(L/2 + \Delta x)^2} \right) \right].$$

(12)

The third term in parenthesis corresponds to the correction due to SCE and DIBL. Fig. 7 shows the comparison of the model and simulation in the relation between S and  $\gamma$  in long and short channel devices. In a long channel device (L = 500nm), eq. (1) is valid, as shown in the figure, and S is the smallest when  $\gamma = 0$ . As L becomes shorter, S gradually becomes larger than the line of eq. (1), and S is severely degraded when L = 40 nm especially in the small  $\gamma$  regime due to SCE. Please note that S exhibits the minimum value at a certain value of  $\gamma$  (around 0.25 when L = 50 nm). This result indicates that the optimum design of  $\gamma$  is very important for LSTP devices, and the present model will help the device design.

### Conclusions

We have proposed empirical models of body factor and subthreshold swing in short channel devices at not only low but high drain voltage. This model is very effective for the design of variable threshold-voltage CMOS circuits.

### Acknowledgements

This work was supported in part by the program for the "Promotion of Leading Researches" in the Special Coordination Funds for Promoting Science and Technology from MEXT. The device simulator (Medici<sup>TM</sup>) has been supplied through VLSI Design and Education Center (VDEC), University of Tokyo in collaboration with Synopsys Inc.

#### References

[1] T. Kuroda et al., *IEEE JSSC*, **31** (1996) 1770. [2] T. Hiramoto et al., *IEICE Trans. Electron.*, **E83-C** (2000) 161. [3] A. Kumar et al., *Solid-State Electron.*, **48** (2004) 1763. [4] Medici Ver. 4.1, Avant! Corp. [5] T. Inukai et al., *JJAP*, **41** (2002) 2312. [6] R. Koh et al., *JJAP*, **35** (1996) 996. [7] T. Nagumo et al., *JJAP*, **42** (2003) 1988. [8] ITRS, 2003.

Fig. 1. (a) A schematic of the device structure assumed in this study. An ideal step-like profile is assumed, where the depletion width  $(W_{dm})$  is determined by the depth of the upper layer  $(t_d)$  with low impurity concentration. In this device structure, Vth and  $\gamma$  are independently varied. (b) Profile of impurity concentration in the assumed device.

Fig. 2. A schematic of the capacitance network model. We consider  $C_G$ ,  $C_B$ ,  $C_S$ , and  $C_D$  as gate, substrate, source, and drain to channel capacitances for unit width, respectively.

140 Vds=0.1V Line: model 130 t...=2.9nm symbol: simulation 120 t.=21.7nm S[mV/dec] 100 90 t<sub>d</sub>=29.0nm 34.8nm 80 70 40 60 80 100 L[nm] 200 400

140 Vds=1.2V Line: model 130 t\_=2.9nm symbol: simulation 120 S[mV/dec] 3[mV/dec] ,=21.7nm  $t_{.}$ =29.0nm 34.8nm 90 80 70 60 80 100 L[nm] 200 40 400

Fig. 3. A schematic of channel potential profile. At a low Vds the maximum of the potential barrier is at the center, while at a high Vds it moves toward the source due to DIBL.

Fig. 4. Comparison of the model and 2D simulation in gate length (L) dependence of subthreshold factor (S). (a) Vds = 0.1 V where DIBL can be neglected. (b) Vds = 1.2 V where DIBL takes place.

Fig. 5. Comparison of the model and 2D simulation in gate length (L) dependence of body factor ( $\gamma$ ). (a) Vds = 0.1 V where DIBL can be neglected. (b) Vds = 1.2 V where DIBL takes place.

Fig. 6. Simulated gate length dependence of DIBL. DIBL exceed 100 mV/V when L < 50 nm.

Fig. 7. The relation between S and  $\gamma$  in devices with different gate lengths. The model and 2D simulation are compared. When L is long enough (L=500 nm), the relation between S and  $\gamma$  is S=60(1+ $\gamma$ ). However, as L is reduced, S becomes larger than the line of S=60(1+ $\gamma$ ) due to SCE. It should be noted that S has the minimum value at a certain value of  $\gamma$  in short channel devices, indicating that the optimum design of  $\gamma$  is very important.