# **Integrated RF-MEMS Technology with Wafer-Level Encapsulation**

Kei Kuwabara<sup>1</sup>, Masami Urano<sup>1</sup>, Junichi Kodate<sup>1</sup>, Norio Sato<sup>1</sup>, Tomomi Sakata<sup>1</sup>, Hiromu Ishii<sup>1</sup>, Toshikazu Kamei<sup>2</sup>, Kazuhisa Kudou<sup>2</sup>, Masaki Yano<sup>2</sup> and Katsuyuki Machida<sup>1</sup>

> <sup>1</sup>NTT Microsystem Integration Laboratories, NTT Corporation

> <sup>2</sup>NTT Advanced Technology Corporation

> 3-1 Morinosato-Wakamiya, Atsugi, Kanagawa 243-0198, Japan Phone: +81-46-240-2717 E-mail: k-kuwa@aecl.ntt.co.jp

## 1. Introduction

Single-chip radio frequency (RF) transceiver LSIs integrating a large number of off-chip devices have been researched to address the need for small high-performance RF transceivers [1]. RF-MEMS technology is attractive as a key technology [2], while conventional studies focused on development of individual devices. Developing single-chip RF transceiver LSIs requires an integration technology for fabricating different kinds of RF-MEMS devices on an LSI and a technology for protecting the RF-MEMS devices during packaging.

We propose an adaptable structure for the integration of different kinds of RF-MEMS devices and a wafer-level encapsulation technique for device protection. In this paper, we first describe the concept of the technology. Then, the fabrication process for the technology is presented. Finally, experimental results are demonstrated.

#### 2. Concept

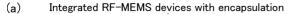

Figure 1 illustrates the concept of the integrated RF-MEMS technology with wafer-level encapsulation. Different kinds of RF-MEMS devices encapsulated in capsules are stacked on an LSI [Fig. 1(a)]. The devices are formed by multi-layer stacking [Fig. 1(b)].

The multi-layer structure has the advantage of adaptability. That is, each layer can be used for many purposes depending on the mask pattern design, so various device structures can be formed by stacking these layers. Thus, the structure enables the fabrication of different kinds of RF-MEMS devices simultaneously on the same plane.

Movable RF-MEMS devices such as switches are separately encapsulated in capsules. The capsules are composed of surrounding walls, a roof, and a sealing film. The capsule structure is formed by a wafer-level process and protects movable devices from destruction during packaging. The encapsulation enables the use of LSI packaging technology.

Therefore, the concept will lead to single-chip RF transceiver LSIs with reliable packaging.

## **3. Fabrication Process**

We developed a fabrication process based on <u>sea</u>mless integration <u>technology</u> (SeaiT) [3] to realize the concept. The process has the following features: i) Multi-layer stacking by electroplating of Au, sputtering of silicon dioxide, and spin coating of sacrificial photosensitive polyimide, ii) selective wafer-level encapsulation by the STP (spin coating film transfer and hot-pressing) technology [4, 5], and iii) a low process temperature (below 310°C).

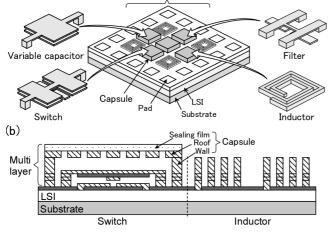

We explain the process using a switch as an example. Figure 2 shows the process flow for the switch, where the switch is formed not on an LSI but on a Si substrate for the examination of the process. First, the switch structure and walls are formed by multi-layer stacking [Fig. 2(a)]. Next, a roof is formed and sacrificial layers are removed by dry ashing [Fig. 2(b)]. Then, etching holes in the roof are sealed by a sealing film made of photosensitive polyimide using the STP technology [Fig. 2(c)]. Finally, the sealing film is patterned to encapsulate the switch selectively [Fig. 2(d)]. As a result, the process provides multi-layer RF-MEMS devices encapsulated by a wafer-level process.

## 4. Results

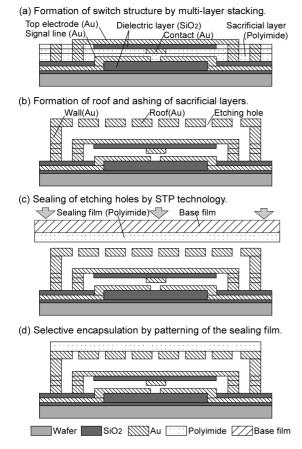

Figure 3 shows an SEM photograph of fabricated RF-MEMS devices without a roof. Different kinds of RF-MEMS devices, such as a switch, a variable capacitor, a resonator, and a filter, were fabricated simultaneously on the same plane using the multi-layer structure.

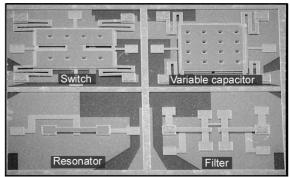

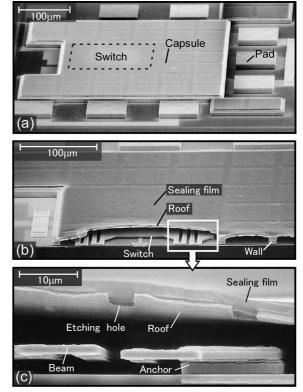

Figure 4 shows SEM photographs of an encapsulated switch. Figure 4(a) shows a fabricated capsule. The switch was properly encapsulated as shown in Fig. 4(b). Figure 4(c) indicates that etching holes in the roof were well sealed. Thus, the wafer-level encapsulation of RF-MEMS devices was achieved.

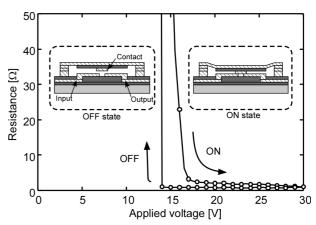

A DC measurement result for the switch is shown in Fig. 5. The switching operation was obtained by applying DC voltage above 16 V, and ON resistance as low as  $1.5 \Omega$  was observed. The result indicates that appropriate device operations can be attained using the technology.

#### 5. Summary

We proposed a multi-layer structure for the integration of different kinds of RF-MEMS devices and the wafer-level encapsulation by STP for protection of the devices. The experimental results proved that the technology provides integrated RF-MEMS devices with encapsulation. Therefore, the technology will pave the way for single-chip RF transceiver LSIs.

## Acknowledgements

The authors thank Dr. Y. Kado for his helpful support and encouragement.

## References

- [1] C. T.-C. Nguyen et al., Proc. IEEE, 86 (1998) 1756.

- [2] S. Lucyszyn, IEE Proc.-Sci. Meas. Technol., 151 (2004) 93.

- [3] H. Ishii *et al.*, Proc. Micromachining and Microfabrication SPIE, **4230** (2000) 43.

- [4] K. Machida et al., J. Vac. Sci. Technol. B, 16 (1998) 1093.

- [5] N. Sato et al., Jpn. J. Appl. Phys., 42 (2003) 2462.

Fig. 1. Concept of the integrated RF-MEMS technology. (a) Single-chip RF transceiver LSI with integrated RF-MEMS devices. (b) Cross section of the RF-MEMS devices formed by multi-layer stacking.

Fig. 2. Process flow for encapsulated switch.

Fig. 3. SEM photograph of integrated RF-MEMS devices. A switch, a variable capacitor, a resonator, and a filter were fabricated simultaneously on the same plane.

Fig. 4. SEM photographs of encapsulated switch. (a) Overall view, (b) inside capsule, and (c) cross section.

Fig. 5. DC measurement result for the switch. Input and output lines were connected by applying DC voltage above 16 V between the top and bottom electrodes.