# Mismatches under the Impact of Hot Carrier Stress in 0.15 µm Technology

S. Y. Chen<sup>1</sup>, J. C. Lin<sup>2,3</sup>, H. W. Chen<sup>1</sup>, H. C. Lin<sup>1</sup>, Z. W. Jhou<sup>1</sup>, S. Chou<sup>2</sup>, J. Ko<sup>2</sup>, T. F. Lei<sup>3</sup>, H. S. Haung<sup>1</sup>

<sup>1</sup>Institute of Mechatronics Engineering, National Taipei University of Technology

1, Sec. 3, Chung-Hsiao E. Rd., Taipei 106, Taiwan

Phone: 886-2-2771-2171 ext: 2011 E-mail: sychen@ntut.edu.tw

<sup>2</sup>Special Technology Division, United Microelectronics Corporation

3, Li-Hsin Rd. 2, Science-Based Industrial Park, Hsinchu city 300, Taiwan

<sup>3</sup>Department of Electronics Engineering, National Chiao Tung University, HsinChu city 300, Taiwan

## 1. Introduction

Mismatching properties of MOSFETs on a same wafer are great concerns of both manufacturers and designers, especially when the wafer carrying analog circuits. The mismatches due to process variations are most commonly known [1,2]. Another popular factor being considered is the size effects such as channel length, width, gate area, and layout types [1-5]. However, it is known that HCI (Hot carrier injection) in normal operation will degrade the MOSFET performance, but the mismatches due to this effect have not been fully explored. May be one of the sole example is the reliability mismatches due to HCI on nMOSFETs of one size was reported to having almost the same distribution under different stress voltages [6].

This paper, for the first time, thoroughly presents the hot carrier stress impact on mismatch properties of n and p MOS transistors with different sizes produced using 0.15  $\mu$ m CMOS technology.

## 2. Experiments

40 pairs transistors evenly distributed on neighbor hooding 5 dies, half n and half p, on a same wafer were stressed to investigate HCI effects on mismatch properties of these transistors. The HCI stress was performed under maximal substrate current at 25 °C. After each stress period, threshold voltage  $V_t$  is monitored at  $V_{ds}$ =0.75 V based on constant current method, and  $I_{ds}$  was monitored at analog operating condition as gate voltage  $V_g=V_t+0.3$  V with  $V_{ds}$ =0.75 V for all nMOSFETs. For pMOSFETs the stress and measurement conditions were the same except that the  $V_{ds}$  and  $V_g$  were negative biased.

### 3. Results and Discussion

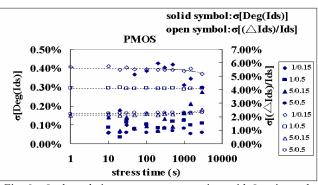

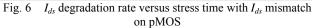

From Fig.1 and 2, one can observe that, for nMOS-FETs, the standard deviations of  $\Delta V_t$  and  $\Delta I_{ds}/I_{ds}$  are enlarged, which means the mismatches are worse after HCI stress. But for the case of pMOSFETs, the changes are much smaller although they possess higher degree of mismatch initially. Also note that the after stress lines of n and pMOSFETs exhibit cross points for both  $\Delta V_t$  and  $\Delta I_{ds}/I_{ds}$ drawings, which mean that the mismatches are the same based on the same gate area. It is suggested that the cross points can be used to indicate the minimal size for n and p pairs to have the same degree of mismatch in designing the devices. For the current case, the minimal gate area should be  $0.25\mu m^2$  at  $\sigma(\Delta V_t) = 8.4$  mV when  $V_t$  mismatch is the first priority. Similarly, the minimal gate area should be about  $0.18\mu\text{m}^2$  at  $\sigma[(\Delta I_{ds})/I_{ds}] = 5\%$  if  $I_{ds}$  mismatch is to be considered first. The mismatch shifts after HCI stress and the matching characteristics of n and pMOS transistors are summarized in Table I and Table II, where the  $A_{Vt}$  and  $A_{Ids}$  in Table II are area factors of corresponding properties defined as [1]

$$\sigma(property) = \frac{A_{property}}{\sqrt{WL}} \tag{1}$$

The statistics reveal that the smallest feature size has the biggest mismatch shift. Hence, the size effect is a dominant factor for property mismatches.

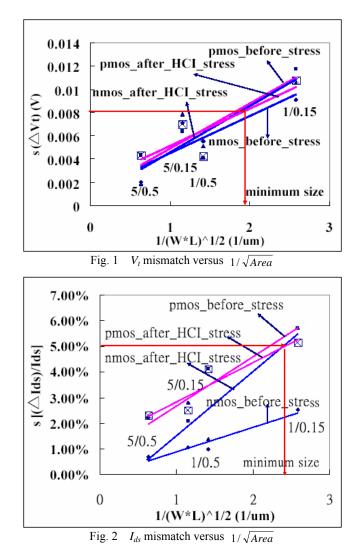

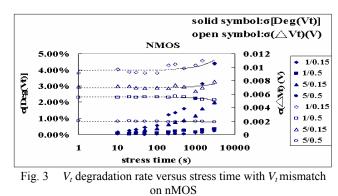

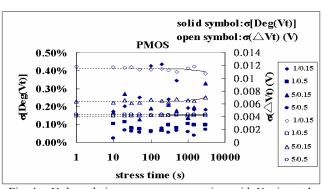

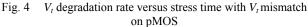

In Fig. 3, 4, 5, and 6, dot lines indicate the trend of property mismatches varying with stress time. It is found that the mismatches of HCI stress degradation on nMOS-FETs are more serious than on their counterparts. It is also observed that the degradation rates of properties on nMOS are faster than on pMOS. This can be explained that the HCI stress degrade nMOS matching more heavily than pMOS.

### 4. Conclusions

The hot carrier injection does degrade matching of nMOSFETs' properties. For pMOSFETs, the changes are minor. It is found that mismatch plots of n and pMOSFETs after stress reveal cross points. The cross points can be used to indicate the minimal size for n and p pairs to have the same degree of mismatches in design phase, such that the circuit performance can be more reliable.

#### References

- K. R. Lakshmikumar, et al., *IEEE Journal of Solid-State Circuits*, SC-21, 6 (1986) 1057.

- [2] M. J. M. Pelgrom, et al., *IEEE J. Solid-state Circuits*, SC-24, (1989) 1433.

- [3] S. J. Lovett, et al., IEE Colloquium on Improving the Efficiency of IC Manufacturing Technology, (1995) 11/1.

- [4] M. Conti, et al., IEEE Trans. on Circuits and Systems-I, Vol 49, 5 (2002) 680.

- [5] J. Bastos, et al., Proc. of IEEE Intern. Conf. on Test Structure, 9 (1996) 17.

- [6] Y. Chen, et al., IEEE IRW Final Report, (2001) 41.

Table I Mismatch shift after HCI stress with multiple W/L ratio

| Parameter                  | Device | Mismatch shift after HCI stress |        |        |        |  |

|----------------------------|--------|---------------------------------|--------|--------|--------|--|

|                            |        | 1/0.15                          | 1/0.5  | 5/0.15 | 5/0.5  |  |

| V <sub>t</sub> (mV)        | nMOS   | 1.462                           | -0.41  | 0.752  | -0.15  |  |

|                            | pMOS   | -1.02                           | 0.144  | 0.659  | -0.013 |  |

| <i>I</i> <sub>ds</sub> (%) | nMOS   | 3.2                             | 0.3827 | 1.76   | -0.035 |  |

|                            | pMOS   | -0.525                          | -0.019 | 0.421  | 0.0785 |  |

Table II Summarized matching characteristics of nMOS and pMOS

| Vdd   | device                   | $A_{Vt}$<br>(mV-µm) | A <sub>Ids</sub><br>(%-μm) | Device size                           |  |

|-------|--------------------------|---------------------|----------------------------|---------------------------------------|--|

| 1 5 V | nMOS before<br>stress    | 0.32                | 0.96                       | W/L=1/0.15,1<br>/0.5,5/0.15,5/<br>0.5 |  |

|       | nMOS after<br>HCI stress | 0.39                | 2.5                        |                                       |  |

|       | pMOS before<br>stress    | 0.39                | 1.92                       |                                       |  |

|       | pMOS after<br>HCI stress | 0.32                | 1.53                       |                                       |  |

Fig. 5  $I_{ds}$  degradation rate versus stress time with  $I_{ds}$  mismatch on nMOS