# High frequency gate bias response of carbon nanotube field effect transistor

Su Heon Hong<sup>1</sup>, Hee Tae Kim<sup>1</sup>, Hyung Kwon Kim<sup>1,2</sup>, Myung Gil Kang<sup>1</sup>, Jong Seoung Hwang<sup>2</sup>, Gyu Tae Kim<sup>3</sup>, Sung Woo Hwang<sup>1,2</sup> and Doyeol Ahn<sup>2</sup>

<sup>1</sup>Department of Electronics and Computer Engineering, Korea University,

5-1 Anam, Sungbuk, Seoul 136-701, Korea

Phone: +82-2-3290-3241 E-mail: swhwang@korea.ac.kr

<sup>2</sup>Institute of Quantum Information Processing and Systems, University of Seoul,

90 Jeonnong, Dongdaemun, Seoul 130-743, Korea

<sup>3</sup>Department of Electrical Engineering, Korea University,

5-1 Anam, Sungbuk, Seoul 136-701, Korea

### 1. Introduction

There have been much interests in the fabrication and the characterization of carbon nanotube field-effect-transistors (CNTFETs) [1] for the future application of large scale integrated circuits. Rapid improvement of the performance has led to the demonstration of such as logic circuits [2], and naturally, the frequency (f) response of CNTFETs has become an important issue. Even though it is expected that CNTFETs can operate at very high fs, actual high f measurements have rarely been done. Recently, f dependent response of a CNTFET was studied at the source/drain terminal which were not impedance matched to the equipment [3].

Here, we report the response of a CNTFET to high f gate pulses. An Al gate with coplanar waveguide (CPW) structure was fabricated so that high f pulses could be transmitted to the CNT channel. The response of the average drain current was measured at various fs, and the f response of the CNTFET was analyzed by a simple equivalent circuit model of conventional FETs.

#### 2. Fabrication and characterization of device

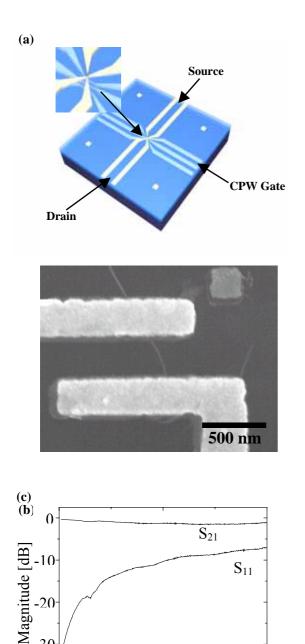

Figure 1(a) is a schematic for the transmission of high frequency pulse to the CPW gate. A few bundles of single wall CNTs dispersed on sodium dodecyl sulfate (SDS) solution were added on a SiO<sub>2</sub> layer under which the Al CPW was formed. The source-drain Ti/Au electrodes were defined on one of the CNT bundles by electron beam lithography. Figure 1(b) shows the scanning electron microscope (SEM) image of the CNT bundle underneath the source and drain electrode with the gap of 300 nm.

The fabricated high *f* CNTFET was mounted on the microwave fixture[4] with wire-bond transition[5] modified for room temperature characterization, and DC and high *f* measurements were performed. Figure 1(c) shows measured S-parameters of the CPW. The  $|S_{21}|$  was less than 0.5 dB when f < 1 GHz and less than 1.5 dB up to f = 10 GHz.

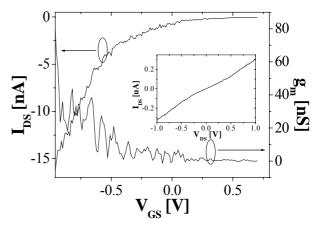

Figure 2 shows the measured DC drain current  $(I_{DS})$  and the trans-conductance  $(\partial I_{DS} / \partial V_{GS} = g_m)$  as a function of the gate bias  $(V_{GS})$  when the drain-source bias  $(V_{DS})$  is -1 V.

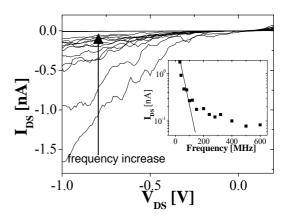

Figure 3 shows average drain current  $(I_{DS}^*)$  measured when 50 % duty cycle rectangular pulses were applied as a

function of  $V_{DS}$ , in the range 0 < f < 600 MHz. The pulse amplitude was 1 V and the offset was zero. The DC  $I_{DS}$ value was obtained by averaging the value of  $I_{DS}$  at  $V_{GS} =$ 0.5 V and that at  $V_{GS} = -0.5$  V. The value of  $I_{DS}^*$  decreases with the increase of f. The inset of Fig. 3 is  $I_{DS}^*$  curve as a function of f in log scale. The data fit with the exponential function exp  $(-f/f_0)$  with  $f_0 = 82$  MHz.

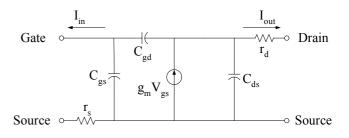

The cutoff frequency  $f_T$  is given by  $g_m/(2\pi C_G)$  where  $C_G$ is the gate coupling capacitance of the CNT. From a parallel plate-cylinder model,  $C_G = 2\pi L \varepsilon_0 / \ln(2h/r)$  and  $h = t_{ox} + r$ , where r is the radius of the CNT, L is the length of the CNT,  $\varepsilon$  is the average dielectric constant of the device, and  $t_{ox}$  is the thickness of the gate oxide. From the condition that r =8 nm, L = 300 nm and  $\varepsilon \sim 4$ ,  $C_G$  is 205 fF. The value of  $g_m$ at  $V_{DS} = -1$  V is -12 nA/V from Fig. 2. The measured  $g_m$  is related with the intrinsic trans-conductance  $g_m'$  by the formula  $g_m = g_m' / (1 + g_m' r_s)$ . Since we have not reached the gate-bias saturation regime, we cannot estimate the contact resistance. However, the metallic CNT fabricated in the same batch shows the source/drain contact resistance of  $\sim 4$  $M\Omega$  at room temperature (inset of Fig. 2). Therefore, this resistance  $r_s$  has little effect on  $g_m$ . Then, the estimation of  $f_T$ is 93 MHz [6]. This is consistent with the observed  $f_0$  in the inset of Fig. 3 within 13 %.

#### **3.** Conclusions

We report the response of a CNTFET to high *f* gate biases. An Al gate with the coplanar waveguide (CPW) structure was fabricated for high *f* pulse transmission to the CNTFET. The *f* response of the drain current was measured up to 600 MHz. The measured  $I_{DS}^*$  exhibited an exponential decrease with the increase of *f* with the characteristic frequency  $f_0 =$  82 MHz. This value was comparable to the cut-off frequency of the transistor calculated from the equivalent circuit with  $g_m$  obtained from DC measurements.

#### Acknowledgements

This work was supported by the Korean Ministry of Science and Technology through the Creative Research Initiative program. The work at Korea University was supported by the BK21 program in 2005.

## References

- [1] S. J. Tans et al., Nature 393 (1998) 49.

- [2] A. Javey et al., Nano Lett 2 (2002) 929.

- [3] J. Appenzeller and D. J. Frank, Appl. Phys. Lett. 84 (2004) 1771.

- [4] M. S. Jun et al., Rev. Sci. Instrum. 75 (2004) 2455.

- [5] JuHwan Lim et al., IEEE Trans. Adv. Packag. (accepted).

- [6] E. S. Yang, in Microelectronic Devices (McGraw Hill, 1988).

Fig. 2  $I_{DS}$  -  $V_{GS}$  and  $(\partial I_{DS} / \partial V_{GS})$  -  $V_{GS}$  characteristics when  $V_{DS} = -1.0$  V. The inset shows  $V_{DS}$ - $I_{DS}$  characteristic of a metallic CNTFET in the same batch.

Fig. 3  $I_{DS}^{*}$  as a function of  $V_{DS}$ , in the range 0 < f < 600MHz. The frequency increases following the direction of The inset is frequency dependent the arrow. characteristics of CNTFET when  $V_{DS}$  is -1.0 V

Fig. 4 Equivalet circuit of the CNTFET.

Fig. 1 (a) Schematic of our CNTFET with a CPW gate. (b) SEM image of the source and drain electrodes. (c) Measured S-parameters of the CPW.

5

Frequency [GHz]

10

-30

0