# H-2-1 (Invited)

# Nitride-based nonvolatile memory and role of SiON dielectric film for performance improvement

Tetsuya Ishimaru, Nozomu Matsuzaki, Takashi Hashimoto\* and Hitoshi Kume

Central Research Laboratory, Hitachi, Ltd., 1-280, Higashi-koigakubo, Kokubunji-shi, Tokyo 185-8601, Japan.

Phone: +81-42-323-1111, Fax: +81-42-327-7753, e-mail: t-ishi@crl.hitachi.co.jp.

\*Renesas Technology Corp., 2-4-1, Marunouchi, Chiyoda-ku, Tokyo 100-6334, Japan.

#### 1. Introduction

Nitride-based charge-trapping memory has recently been paid much attention as a replacement for floating-gate nonvolatile memory. Nitride memory has advantages of low-cost process, low voltage operation and high compatibility to logic process, which is suitable for embedded application [1-7]. Multi-bit operation by means of localized charge trapping in nitride is also an attractive feature of this memory, which enables high-density memory for mass storage [8-10].

So far, various kinds of nitride-based memories have been proposed. In this paper, several leading nitride memories are compared, and a split-gate MNOS memory we have developed for embedded use is introduced.

# 2. Nitride-based memory technology

Several nitride-based memories have been compared in Table 1. These are divided into two groups according to the applications: embedded memory on SoC or mass storage. For mass storage use, bit size is the most important, and multi-bit operation is necessary. The multi-bit operation is achieved by localized charge storage in nitride, which is given by hot carrier injection. On the other hand, for embedded use, it is important to reduce the area of peripheral circuits which occupy large part

of a flash module.

# 3. Split-gate MNOS memory

### Concept of memory cell design

We have developed a split-gate MNOS memory for embedded use aiming at low-cost production by means of the reduction of peripheral circuit area as well as high-frequency operation and high reliability.

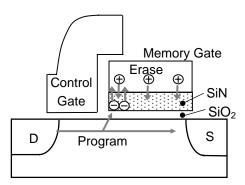

The cell structure and the operation bias condition of this memory are shown in Fig. 1 and Table 2, respectively. The key features are: (1) program by source-side hot-electron injection and erase by electron emission from the nitride and hole injection, and (2) a control-gate (CG) transistor with the same oxide thickness as a core MOS transistor.

These features lead to the reduction of the peripheral circuit area. Low current consumption and use of only positive voltage both for program and for erase operations reduce power-supply circuits [5]. In addition, wordline decoder/driver circuit can be composed of only low-voltage transistors because only low voltage is applied to the CG, which also contributes to small area of the peripheral circuits [4].

High-frequency operation is obtained by large read-out current of this memory, which is given by the CG transistor with

$Table\ 1.\ Comparison\ of\ nitride-based\ nonvolatile\ memories$

|                                | NROM[8]                              | PHINES[9]                     | Twin<br>MONOS[10]                    | SONOS[1]              | LONOM[3]                             | Split-gate<br>MNOS[5]                               |

|--------------------------------|--------------------------------------|-------------------------------|--------------------------------------|-----------------------|--------------------------------------|-----------------------------------------------------|

| Program                        | Channel<br>hot electron<br>injection | BTBT<br>hot hole<br>injection | Channel<br>hot electron<br>injection | Electron<br>tunneling | Channel<br>hot electron<br>injection | Source side<br>hot electron<br>injection            |

| Erase                          | BTBT<br>hot hole<br>injection        | FN electron injection         | BTBT<br>hot hole<br>injection        | Hole<br>tunneling     | BTBT<br>hot hole<br>injection        | FN electron<br>emission &<br>Gate hole<br>injection |

| ONO thickness<br>(from top-ox) | 9/6/7                                | 9/6/6                         | 4/5/4                                | 3/15.5/1.8            | 8.5/5/4                              | 0/26/4                                              |

| Number of gates/cell           | 1                                    | 1                             | 3                                    | 1                     | 1                                    | 2                                                   |

| Multi-bit operation            | Yes                                  | Yes                           | Yes                                  | No                    | No                                   | No                                                  |

| Main<br>Applications           | Mass storage                         | Mass storage                  | Mass storage,<br>Embedded            | IC card,<br>Embedded  | Embedded                             | Embedded                                            |

Fig. 1. Schematic cross section of split-gate type MNOS memory.

Table 2. Bias conditions of program/erase operations

|         | $V_{mg}$ | $V_{cg}$ | $V_s$ | $V_d$ |

|---------|----------|----------|-------|-------|

| Program | 12V      | 1.5V     | 6V    | 0.8V  |

| Erase   | 15V      | 1.5V     | 0V    | 0V    |

thin oxide thickness and the large Vt window operation.

High reliability is one of inherent characteristics of this memory, which is because of a low oxide damage without using hot-hole injection, no mismatch between electron and hole injection, and good charge retention by a thick bottom oxide and nitride [5-7].

#### Memory performance using SiON charge-trapping layer

Performance and reliability of the split-gate MNOS memory are further improved by using a SiON film instead of a SiN film as a charge-trapping layer [7]. This is due to the increase in hole injection efficiency from the gate during erase and deep level of electron traps in a SiON film.

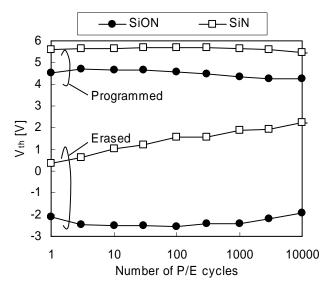

Figure 2 shows endurance characteristics of the memories with SiN and SiON films. It is verified that erase speed of the

Fig. 2. Endurance characteristics for SiON and SiN.

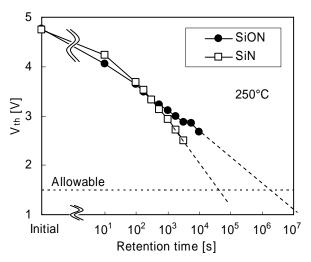

memory using SiON is faster than that using SiN and that erase speed degradation is suppressed for SiON. As a result, large Vt window and large read-out current can be obtained for SiON. Figure 3 shows retention characteristics measured at 250°C. Significant improvement of retention lifetime is achieved for SiON compared to that for SiN.

Fig. 3. Retention characteristics of SiN and SiON.

#### 4. Conclusion

Nitride-based nonvolatile memory is attractive for mass storage and embedded applications, and we have developed an embedded split-gate MNOS memory. This memory has the advantages of low-cost production, high-frequency operation and high reliability. Further, using a SiON film instead of a SiN film as a charge-trapping layer, the performance and reliability are significantly improved. The split-gate MNOS memory is considered to be one of the most promising embedded memories.

# Acknowledgements

The authors would like to express their sincere thanks to Shogo Kiyota, Katsutaka Kimura, and Takahiro Onai for encouragement, and to Tatsuro Toya, Katsuhiko. Kubota, and Kosuke Okuyama for useful suggestions.

#### References

- [1] S. Minami and Y. Kamigaki, ICICE Trans. E84-C, pp.713, 2001.

- [2] C. T. Swift et al., IEDM Tech. Dig., pp.927, 2002.

- [3] J.-H. Kim et al., VLSI Tech. Dig., pp.31, 2003.

- [4] T. Tanaka et al., VLSI Circ. Dig., pp.221, 2003.

- [5] N. Matsuzaki et al., Ext. Abst. SSDM, pp.204, 2003.

- [6] F. Ito et al., VLSI Tech. Dig., pp.80, 2004.

- [7] T. Ishimaru et al., IEDM Tech. Dig., pp.885, 2004

- [8] B. Eitan et al., Proc. SSDM 99, Tokyo pp.522, 1999.

- [9] C.C. Yeh, et al., IEDM Tech. Dig., pp.931, 2002

- [10] Y. Hayashi et al., VLSI Tech. Dig., pp.122, 2000.