# Multi-bit Programming for 1T-FeRAM by Local Polarization Method

Yoshiaki Tabuchi<sup>1</sup>, Satoshi Hasegawa<sup>1</sup>, Tetsuro Tamura<sup>2</sup>, Hiromasa Hoko<sup>2</sup>, Kazumi Kato<sup>3</sup>, Yoshihiro Arimoto<sup>4</sup>, Hiroshi Ishiwara<sup>1</sup>

<sup>1</sup>Tokyo Institute of Technology, Interdisciplinary Graduate School of Science and Engineering 4259 Nagatsuta-cho, Midori-ku, Yokohama, Kanagawa 226-8503, Japan Phone: +81-45-924-5874 E-mail: ytabuchi@neuro.pi.titech.ac.jp

<sup>2</sup>Silicon Technology Lab., FUJITSU LABORATORIES LTD.

10-1 Morinosato-Wakamiya, Atsugi 243-0197, Japan

<sup>3</sup>National Institute of Advanced Industrial Science and Technology 2266-98 Anagahora, Shimoshidami, Moriyama-ku, Nagoya, 463-8560, Japan

<sup>4</sup>System LSI Development Labs., FUJITSU LABORATORIES LTD.

4-1-1 Kamikodanaka, Nakahara-ku, Kawasaki, Kanagawa 211-8588, Japan

### 1. Introduction

FeRAM has such distinctive features as nonvolatality, low power consumption. FeRAMs are being mass-produced up to the capacity of 1Mbit. However, FeRAM applications are limited at present because of restriction of the memory capacity. MFIS-FET which has ferroelectric layer between gate and insulator, is a 1-transistor type memory device and has minimal cell size. In this study, multi-bit programming performed on MFIS-FET for the further increase of the capacity of FeRAM.

## 2. Experiment

**MFIS-FET**

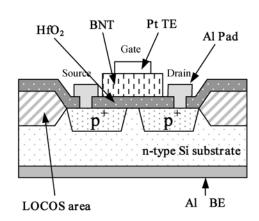

MFIS-FET was fabricated as shown in fig. 1. Ferroelectric layer and insulator layer were formed using (Bi, Nd)<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub> (BNT) which has appropriate coercive field and  $HfO_2^{[1][2][3]}$  which has excellent channel characteristics, respectively.

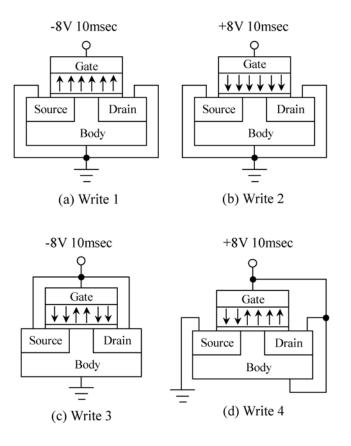

Data programming method

Data programming method for multi-bit memory is shown in fig. 2. For "Write 1" and "Write 2", pulses of +8V or -8V were applied to gate while drain, source, and body were held at ground level, corresponding to typical writing method for "on" state and "off" state. Pulse width was 10ms for all write operation. "Write 3" pulse was applied after "Write 2" operation to switch the polarization of the ferroelectric on the channel area. A pulse of -8V was applied to gate, drain and source, while body was held at ground level. Similarly, "Write 4" pulse was applied after "Write 1" to switch the polarization on the source area. A pulse of +8V was applied to gate, drain and body, while source was kept at ground level.

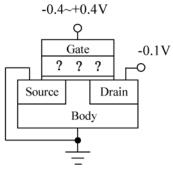

Read process is shown in figure 3. The gate voltage was held at a voltage between -0.4V and +0.4V, and drain voltage was held at -0.1V.

### 3. Result and discussion

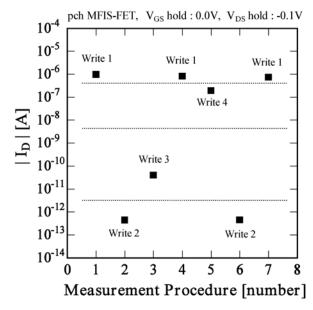

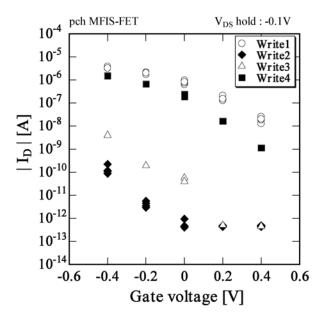

Figure 4 shows the change of read out current after each write operation. The current level for "Write 3" and

"Write 4" were between those for "Write 1" and "Write 2" which are conventional "on" and "off" state. Comparison of the polarization states for "Write 2" and "Write 3" or "Write 1" and "Write 4" reveals that the polarization on the drain region has dominant influence on the current level.

Figure 5 shows the results of read out current with different gate voltage. The four write states are able to be distinguished by the shift of the threshold voltage. The signal margin might be optimized by the device parameter such as channel length or ferroelectric properties. Moreover, 3bit programming can be achieved by source-drain exchange at write and read operation.

#### 4. Conclusions

Multi-bit programming was performed on MFIS-FET. The polarization of the ferroelectric on the channel and source / drain region was controlled locally by the combination of programming bias, which resulted in the change of the read out current in four levels. The result showed the possibility of further increase of capacity of FeRAM.

### References

- [1] S. Sakai and R. Ilangovan, IEEE Electron. Dev. Lett. 25 (2004) p. 369.

- [2] K. Aizawa, B-E Park, Y. kawashima, K. Takahashi and H. Ishiwara, Appl. Phys. Lett. **85** 3199-3201 (2004)

- [3]K.Takahashi, B.E. Park, K.Aizawa and H. Ishiwara, Extended Abstract of the 2004 International Conference on Solid State Devices and Materials, (2004), pp.52-53

Fig. 1 A cross section of the fabricated MFIS-FET

Fig. 2 Write method

Fig. 3 Read method

Fig. 4 Read out current after various write operation. The gate voltage is 0V.

Fig. 5 Relation between read out current and gate voltage for each write state.