# P1-9

**Reduction of Accumulation Thickness in Metal Gate** Hiroshi Watanabe<sup>A</sup>, Kazuaki Nakajima<sup>B</sup>, Kouji Matsuo<sup>B</sup>, Tomohiro Saito<sup>B</sup>, and Takuya Kobayashi<sup>B</sup>

(A) Advanced LSI Technology Laboratory, Toshiba Corp., Isogo, Yokohama, 235-8522, Japan

Phone: +81-45-770-3691 Facsimile: +81-45-770-3578 E-mail: pierre.watanabe@toshiba.co.jp

(B) Process and Manufacturing Engineering Center, Semiconductor Company, Toshiba Corp., Isogo, Yokohama, 235-8522, Japan

## Abstract

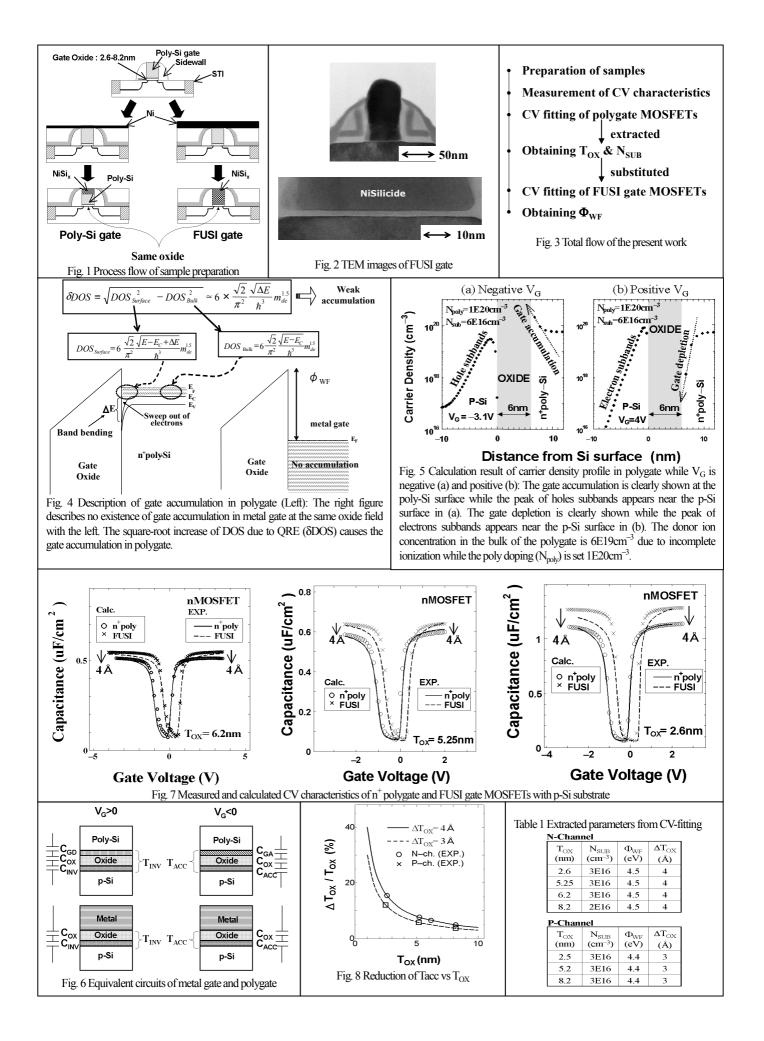

Although it has been believed that highly doped polygate can hardly be accumulated, we will show a decisive evidence for existence of the gate accumulation that contributes to 4Å (nMOSFET) and 3Å (pMOSFET) in accumulation thickness with regardless of gate oxide thickness. This makes an accumulation thickness smaller in metal gate than in polygate.

## Introduction

It has been considered that metal gate is necessary to improve transistor performance in 45nm generation and beyond [1-4], since gate depletion width can be excluded from inversion thickness (Tinv) in polygate MOSFETs. On the other hand, there are few reports explaining an accumulation thickness (Tacc) in metal gate is smaller than in polygate, which is clearly seen in the measured CV characteristics [1, 3, 4], since Tacc has been regarded to be same between in polygate and metal gate. We pointed out an importance of the gate accumulation that is due to quantum repulsion effect (QRE) in the analysis of gate capacitance [5, 6]. Here we investigate the gate accumulation in both experimental and theoretical manners, taking into account the QRE. Consequently, it is found that Tacc is thicker by 4Å (nMOSFET) and 3Å (pMOSFET) in polygate than in metal gate. Experiments

To investigate the gate accumulation, we compare CV characteristics between in polygate and in metal gate. A Ni full silicide (FUSI) gate is fabricated as a metal gate using the process described in Fig. 1. The polygate is obtained if the Ni layer is thinner. Since gate oxides in samples of both gates are prepared with the same oxidation process, the thicknesses of both gate oxides are same. The TEM image of the FUSI gate is shown in Fig. 2. The total flow of the present work is schemed in Fig. 3. The CV-fitting of polygate is carried out to extract the substrate impurity concentration  $(N_{\mbox{\scriptsize SUB}})$  and the oxide thickness (T<sub>OX</sub>). The CV-fitting of FUSI gate is subsequently carried out using these  $T_{\text{OX}}$  and  $N_{\text{SUB}}$  to extract the work function ( $\Phi_{WF}$ ). Here note  $T_{OX}$  is used instead of Tacc and Tinv in the present CV-fitting in which the QRE is included.

## Theory

Fig. 4 describes an origin of the gate accumulation in polygate while a gate voltage  $(V_G)$  is negative. In the left-hand side, the QRE sweeps electrons away from the bended band at the poly-Si surface, since the bended area is too narrow for electrons to be confined there. In other words, the electrons are excited up to 3-dimensional conduction band at the poly-Si surface. The energy levels measured from the conduction band edge at the poly-Si surface accordingly become larger by the band-bending ( $\Delta E$ ). The density-of-states (DOS) is therefore increased in a square-root manner of  $\Delta E$ . This square-root increase of DOS (&DOS) causes the electron density to be increased at the poly-Si surface, while the DOS is not increased at the metal gate surface. Therefore, this  $\delta DOS$  distinguishes between the polygate and the metal gate. Fig. 5(a) shows the calculation results of carrier densities in a negative V<sub>G</sub>. The gate accumulation is clearly shown at the poly-Si surface as the increase of electron density due to  $\delta DOS$ . On the other hand, Fig. 5(b) exhibits the gate depletion as the decrease of electron density at the poly-Si surface. The width of this decreased area turns out almost same as that of the increased area of gate accumulation shown in Fig. 5(a). All the calculations performed here include the effects of not only the QRE but also incomplete depletion of polygate, subbands of electrons and holes, incomplete ionization and band-gap narrowing [5-7], which results in Tox=Tacc=Tinv. For simplicity, we neglect interfacial transition (IFT) layers [6] from both sides of SiO<sub>2</sub> since a chemical transition in the SiO<sub>2</sub>/FUSI interface is unknown and T<sub>OX</sub> estimated in CV-fitting is irrespective of whether or not the IFT layers are considered, as shown in Fig. 7(a)-(c) of [6]. A quantum-mechanical depletion caused by reflection of wavefunction from an abrupt barrier at the flat band, so-called dark space effect [8], is also neglected. This effect might appear in the gate accumulation, since a wavefunction in the 3-dimensional conduction band to which electrons are excited up by the QRE is similar to the wavefunction at the flat band. As shown in Fig. 6, the gate capacitance is composed of the gate accumulation capacitance ( $C_{GA}$ ), the oxide capacitance ( $C_{OX}$ ) and the silicon accumulation capacitance  $(C_{ACC})$  in a negative  $V_G$ , while it is composed of the gate depletion capacitance ( $C_{GD}$ ),  $C_{OX}$ , and the silicon inversion capacitance ( $C_{INV}$ ) in a positive  $V_G$ . The  $C_{GA}$  as well as C<sub>GD</sub> are excluded from in metal gate.

### **Results and Discussion**

Shown is the main result of nMOSFETs in Fig. 7. We have obtained excellent agreements between measured and calculated CV characteristics in each gate in both polarities of V<sub>G</sub> with regardless of T<sub>OX</sub>. There are clear discrepancies between polygate and FUSI gate in both polarities of V<sub>G</sub>, which means that the gate accumulation as well as the gate depletion exists in the polygate. These discrepancies are compensated in both polarities of  $V_G$  with regardless of  $T_{OX}$  if  $T_{OX}$  is reduced by 4Å in the polygate, which means that the effective thickness ( $\Delta T_{OX}$ ) of gate accumulation is same as that of gate depletion and is estimated 4Å with regardless of T<sub>OX</sub>. In pMOSFETs,  $\Delta T_{OX}$  of both gate depletion and gate accumulation are 3Å with regardless of  $T_{\text{OX}}.$  Fig. 8 shows the ratio of  $\Delta T_{\text{OX}}$  to  $T_{\text{OX}}$  is then increased as  $T_{OX}$  is reduced. The  $\Phi_{WF}$  of FUSI gate is 4.5eV in nMOSFETs and 4.4eV in pMOSFETs with regardless of  $T_{\text{OX}}$ . The parameters extracted here are summarized in Table. 1. Discrepancies left between the calculated and measured capacitance in FUSI gate near ±1V, as shown in Fig. 7, can be ascribed to the IFT layers since the dark space effect is most remarkable at the flat band (-0.6V in FUSI gate) [8]. No discrepancy at the flat band suggests that the measured samples include the SiO<sub>2</sub>/FUSI IFT layer that breaks the condition of the abrupt barrier for the dark space effect.

Summary The QRE is necessary to precisely predict the CV characteristics of both polygate and metal gate in both polarities of V<sub>G</sub> with regardless of  $T_{OX}$ . The  $\Delta T_{OX}$  is 4Å in nMOSFET and 3Å in pMOSFET with regardless of  $T_{OX}$ , which reaches 30-40% at  $T_{OX}$ = 1nm. The influence

whereas the dark space effect is removed by the IFT layer.

#### References

of IFT layer at the FUSI gate interface is left in the CV characteristics,

- [1] B. Tavel et al., IEDM01, p. 825 (2001)

- [2] J. Kedzierski et al., IEDM02, p. 247 (2002)

- [3] T. Aoyama et al., IEDM04, p. 95 (2004)

- [4] K. Manabe, et al., SSDM04, p. 18 (2004)

- [5] H. Watanabe, K. Uchida, and A. Kinoshita, SSDM03, p. 270 (2003)

- [6] H. Watanabe, D. Matsushita, and K. Muraoka, SSDM04, p. 732 (2004)

- [7] H. Watanabe and S. Takagi, J. Appl. Phys., 90, p. 1600 (2001)

- [8] A. S. Spinelli, A. Pacelli, and A. L. Lacaita, IEEE TED 47, 2366 (2000)