# Pd<sub>2</sub>Si Fully-Silicided Gate: Kinetics of Silicide Formation and Workfunction Tuning

Takuji Hosoi, Kosuke Sano, Kosei Hosawa, and Kentaro Shibahara

Research Center for Nanodevices and Systems, Hiroshima University 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan Phone: +81-82-424-6265, Fax: +81-82-424-3499, E-mail: hosoi@sxsys.hiroshima-u.ac.jp

### 1. Introduction

NiSi fully-silicided (FUSI) gate is one of the most promising candidates for metal gate CMOS technology [1] because of its process compatibility and workfunction tunability by predoping [2,3]. Dopant pileup formed by snowplow effect [4] during silicidation is considered to be the origin of workfunction shift. However, the reported magnitude of the shift was insufficient for CMOS application [5-8], and a detail of workfunction shift mechanism is still unclear. In addition, an adhesion issue of doped NiSi film and void formation at the NiSi/SiO<sub>2</sub> interface was pointed out [7-9]. Research on the other silicides would help better understanding and improving FUSI gate technology.

We have investigated  $Pd_2Si$  FUSI gate MOS structure.  $Pd_2Si$  has higher thermal stability than NiSi [10], and its lower silicidation temperature provides flexibility for device fabrication process. Residual compressive stress in a  $Pd_2Si$  film is 50 MPa [11], which is much smaller than NiSi (720 MPa) [12]. These stress values might be related to the volumetric changes due to silicidation. Since the snowplow effect similar to NiSi was reported for  $Pd_2Si$  [4], workfunction tunability is also expected. In this report,  $Pd_2Si$  FUSI gate formation process and workfunction tuning are described.

# 2. Pd<sub>2</sub>Si FUSI gate Formation

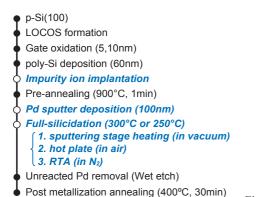

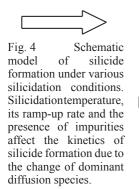

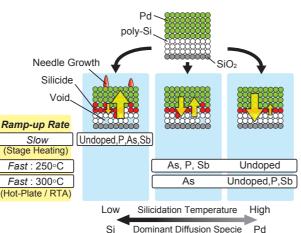

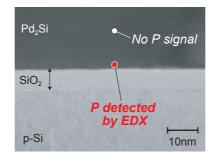

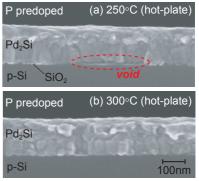

Fig. 1 shows the fabrication process flow of Pd<sub>2</sub>Si FUSI gate MOS diodes. Since Pd<sub>2</sub>Si is the first phase in a Pd-Si system, one step annealing was performed for silicidation. Three types of heating equipments, lamp heating in a sputtering chamber, hot-plate and RTA were used for silicidation. Fig. 2 shows XTEM (cross-sectional TEM) image of Pd<sub>2</sub>Si FUSI gate formed at 250 °C with lamp heating. Needle-like silicide growth at the surface, formation of mixed silicide phases and void formation at the Pd<sub>2</sub>Si/SiO<sub>2</sub> interface were observed. In the case of hot-plate heating, only the Pd<sub>2</sub>Si phase was formed, which was confirmed by X-ray diffraction [13]. This is attributed to higher ramp-up rate because of large thermal capacity ratio of the hot-plate and a Si substrate. However, the voids at the interface were still formed at 250 °C even with the hot-plate heating especially for the predoped case shown in Fig. 3(a). This void formation was avoided by raising the silicidation temperature to 300 °C (Fig. 3(b)). Similar results were obtained by the RTA silicidation. These results indicate that the ramp-up rate for silicidation annealing as well as the silicidation temperature and the presence of impurities are key factors to control the silicide formation, as illustrated in Fig. 4. Since an excessive Si diffusion toward the NiSi surface and the resulting void formation have also been found in Sb doped NiSi FUSI gate [14], the reduction of Si diffusion is a common issue for FUSI gates.

## 3. Workfunction Tuning by Impurity Predoping

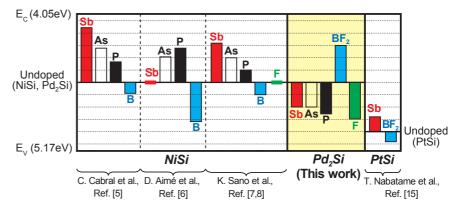

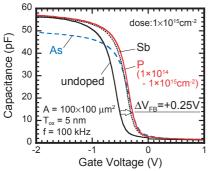

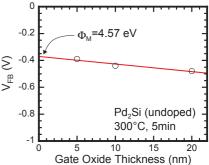

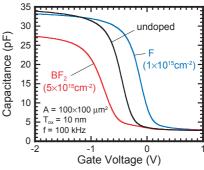

As shown in Fig. 5, the workfunction of undoped Pd<sub>2</sub>Si FUSI gate was estimated to be 4.57 eV. Fig. 6 shows C-V characteristics for undoped and P, As, and Sb predoped Pd<sub>2</sub>Si FUSI gate MOS diodes. The positive flatband voltage  $(V_{FB})$ shifts were obtained with these impurities inspite of n-type dopants. The maximum  $V_{FB}$  shift obtained with P was +0.25 V regardless of the implantation dose. No interfacial layer formation was found in the XTEM image as shown in Fig. 7. From EDX analysis, P signal was detected only in the Pd<sub>2</sub>Si layer in the vicinity of the Pd<sub>2</sub>Si/SiO<sub>2</sub> interface. These results indicate that impurity pileup at the interface is an origin of the workfunction shift, as in the case of NiSi. On the other hand, the  $V_{FB}$  shift of -0.30 V was obtained for BF<sub>2</sub> predoped  $Pd_2Si$ , as shown in Fig. 8. Furthermore, the  $V_{FB}$  shift of +0.30 V was obtained with F predoping, despite no shift in NiSi [7,8]. It is interesting that the Pd<sub>2</sub>Si FUSI gate workfunction shifts by As, P, Sb and BF<sub>2</sub> predoping are all in the opposite direction to the NiSi [5-9] and PtSi [15], as summarized in Fig. 9.

### 4. Summary

It has been found that the high ramp-up rate to avoid the silicidation reaction at low temperature is an important factor to control the quality of the silicide layers. The workfunction of undoped  $Pd_2Si$  is 4.57 eV, which can be modulated by impurity predoping of poly-Si. It is noteworthy that the  $Pd_2Si$  workfunction shifts with various impurities are all in the opposite direction to the NiSi case.

# Acknowledgement

This work was partly supported by a Grant-in-Aid for the 21st Century COE program "Nanoelectronics for Tera-bit Information Processing" and STARC.

### References

- [1] P. Ranade et al., IEDM 2005, p.227.

- [2] J. Kedzierski et al., IEDM 2002, p.247.

- [3] W. P. Maszara et al., IEDM 2002, p.367.

- [4] I. Ohdomari et al., Appl. Phys. Lett. 38, 1981, p.1015.

- [5] C. Cabral, Jr. et al., VLSI Tech. Symp. 2004, p.184.

- [6] D. Aimé et al., IEDM 2004, p.87.

- [7] K. Sano et al., SSDM 2004, p.456.

- [8] K. Sano et al., Jpn. J. Appl. Phys. 44, 2005, p.3774.

- [9] J. Kedzierski et al., IEEE Trans. Electron Devices, **52**, 2005, p.39.

- [10] J. F. Chen et al., Mater. Chem. and Phys. **39**, 1995, p.229.

- [11] A. Lauwers et al., J. Vac. Sci. Technol. B 19, 2001, p.2026.

- [12] P. Gergaud et al., Mater. Res. Soc. Symp. Proc. 615, 2000, G8.3.

- [13] K. Sano et al., IEEE RTP Conf., 2005, p.145.

- [14] T. Hosoi et al., ISDRS 2005, p.244.

- [15] T. Nabatame et al., IEDM 2004, p.83.

Fig. 1 Fabrication process flow of Pd<sub>2</sub>Si FUSI gate MOS diodes.

Fig. 6 C-V characteritstics of Pd<sub>2</sub>Si FUSI gate MOS diodes with As, P or Sb doping.  $V_{FB}$  shift of +0.25 V was obtained with P predoping regardless of implanted dose. Capacitance reduction due to void formation occured with As doping.

Fig. 9 Summary of the workfunction shift with various impurities in NiSi [5-8], PtSi [15] and Pd<sub>2</sub>Si FUSI gate MOS structures. The range of workfunction values of Pd<sub>2</sub>Si (~0.6 eV) is comparable to that for NiSi, but the shifts in Pd<sub>2</sub>Si are all in the opposite direction to the NiSi and PtSi.

Fig. 2 XTEM image of As predoped Pd, Si FUSI gate formed at 250°C with lamp heating. Initial Pd and poly-Si thicknesses were 180 nm and 100 nm, respectively.

Dominant Diffusion Specie Pd

Fig. 7 XTEM image of the interfaces in P predoped Pd<sub>2</sub>Si FUSI gate MOS diode. P signal was detected at the Pd<sub>2</sub>Si/SiO<sub>2</sub> interface by EDX analysis.

Fig. 3 Cross-sectional SEM micrograph of Pd<sub>2</sub>Si FUSI gate formed at 250 °C (a) and 300 °C (b) with hot-plate heating.

Fig. 5 Flatband voltage as a function of gate oxide thickness extracted from the C-V characteristics of undoped Pd<sub>2</sub>Si FUSI gate MOS diodes.

Fig. 8 C-V characteritstics of Pd<sub>2</sub>Si FUSI gate MOS diodes with BF<sub>2</sub> or F.  $\tilde{V}_{FB}$ shift of -0.3 V and +0.3 V were obtained with BF<sub>2</sub> and F predoping, respectively.