# Combined Negative Bias Temperature Instability and Hot Carrier Stress Effects in Low Temperature Poly-Si Thin Film Transistors

Chih-Yang Chen<sup>1</sup>, Jam-Wem Lee<sup>2</sup>, Wei-Cheng Chen<sup>3</sup>, Hsiao-Yi Lin<sup>3</sup>, Kuan-Lin Yeh<sup>3</sup>, Po-Hao Lee<sup>1</sup>, Ming-Shan Shieh<sup>1</sup>, Shen-De Wang<sup>1</sup> and Tan-Fu Lei<sup>1</sup>

<sup>1</sup>Institute of Electronics, National Chiao Tung University, 1001 Ta-Hsueh Rd., Hsin-Chu 300, Taiwan, R. O. C. <sup>2</sup> National Nano Device Laboratory, Hsin-Chu, Taiwan, R.O.C. <sup>3</sup>Toppoly Optoelectronics Corp., Miao-Li, Taiwan, R. O. C. Phone:+ 886-3-5712121 ext 54219 Fax: +886-3-5724361 E-mail: cyc.ee92g@nctu.edu.tw

#### 1. Introduction

To recognize the reliability of low temperature poly-Si thin film transistors (LTPS TFTs), hot carrier stress (HCS) has been extensively applied. Due to the poor conductivity of the buffer oxide, the temperature dependency of HCS induced degradation is an important concern in LTPS TFTs, as well as in SOI MOSFETs. Furthermore, negative bias temperature instability (NBTI) has been reported to degrade the device reliability, especially in the threshold voltage shift ( $\Delta V_{th}$ ) [1]. However, the mechanism and correlation between HCS induced degradation and NBTI in p-channel LTPS TFTs has not been explored. Therefore, this study aimed to study the device degradation mechanism under NBTI and HCS. Besides, a modified model was proposed to explain the degradation mechanism.

#### 2. Experimental

P-channel LTPS TFTs were fabricated on glass substrates. A 40nm-thick amorphous Si layer was deposited and crystallized by excimer laser annealing. Gate dielectric was deposited with an equivalent 100nm-thick  $SiO_2$  layer and followed by Mo deposition as gate electrode. Source and drain were doped by plasma doping. Then, the inter-layer dielectric was deposited. Finally, metal pad was deposited and patterned. Both the channel length (L) and width (W) of the device used in this work were 20µm.

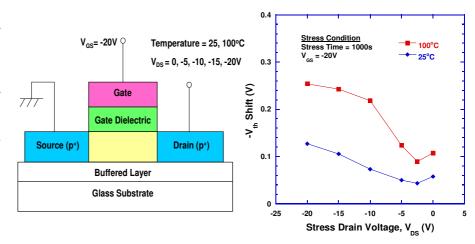

The NBTI stress was performed with  $V_{GS}$  of -20V. The  $V_{DS}$  was varied from 0 to -20V to study the combined NBTI and HCS effects. The schematic cross-section view of the LTPS TFT and the stress setup is shown in Fig. 1.

### 3. Results and Discussion

Figure 2 reveals the  $\Delta V_{th}$  of the devices after various stress conditions. At  $V_{DS} = 0$ V, the device degradation is primarily caused by NBTI. As  $V_{DS}$  increases from 0 to -2.5V, the  $\Delta V_{th}$  slightly decreases, implying NBTI was suppressed. As  $V_{DS}$  continuously increases to -20V, the  $\Delta V_{th}$  increases due to the enhanced hot carrier generation. The  $\Delta V_{th}$  is larger for the devices stressed at 100°C than those stressed at 25°C because NBTI and hot hole injection can be thermally enhanced at elevated temperature [1][2].

To quantify the combined effects of NBTI and HCS, both the empirical models for NBTI and HCS will be discussed. For the NBTI stress, the  $\Delta V_{th}$  can be modeled as [3]

$$\Delta V_{th} = At^n \exp(-\frac{E_a}{kT}) \exp(C|V_G|) = A' \exp(C|V_G|)$$

(1)

where  $A' = At^n exp(-E_a/kT)$ . In our case, instead of grounded drain, a  $V_{DS}$  was applied; thus the model must be modified. We assumed V(y) is the hole quasi-Fermi potential at a point y along the channel with respect to the Fermi poten-

tial of the p<sup>+</sup> source. At low  $V_{DS}$ , V(y) varies almost linearly between source and drain [4]. Thus V(y) can be concisely express as  $V(y)=(y/L)\times V_{DS}$ , and the  $\Delta V_{th}$  can be rewritten as

$$\Delta V_{th} = \frac{A'}{L} \int_{0}^{L} \exp[C(|V_{GS}| - |V(y)|)] dy = \frac{A'}{C|V_{DS}|} \exp[C|V_{GS}|) [1 - \exp(-C|V_{DS}|)]^{(2)}$$

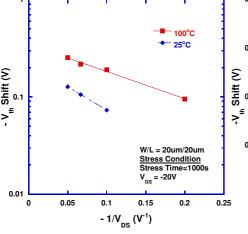

The analytic model can be used to interpret the NBTI effect under low  $V_{DS}$  bias. For the HCS (high  $V_{DS}$ ), the  $\Delta V_{th}$  can be experimentally expressed as [5]

$$\Delta V_{th} = Bt^n \exp(-\frac{\alpha}{|V_{DS}|}) = B' \exp(-\frac{\alpha}{|V_{DS}|})$$

(3)

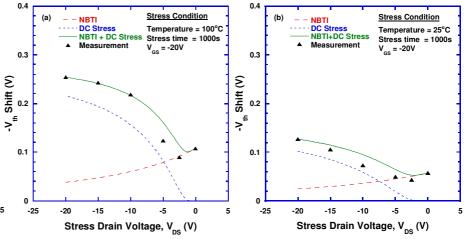

where  $B'=Bt^n$ , and  $\alpha$  can be extracted from the slope of Fig. 3. By combining the  $\Delta V_{th}$  in equation (2) and (3), the overall  $\Delta V_{th}$  caused by NBTI and HCS can be predicted as shown in Fig. 4(a) and (b). The measured data follows the same trend as the modified model, which confirmed the mixed NBTI and HCS effects dominate the degradation mechanism as  $V_{DS}$  is applied.

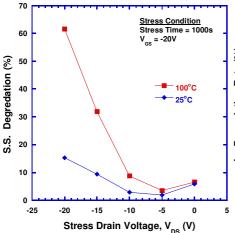

Figure 5 show the degradation rate of S.S., which reflects the interface states generation. The S.S. is closely related to the deep interface states, which originate from the dangling bonds [6]. The increase of  $V_{DS}$  leads to more S.S. degradation, because more hot carriers were generated by impact ionization and the Si-H bonds were broken by hot carriers.

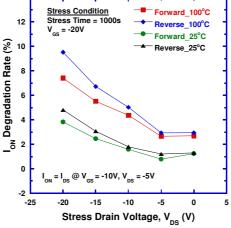

Figure 6 shows the on current ( $I_{ON}$ ) degradation rate. At low  $V_{DS}$ , both the forward and reverse mode  $I_{ON}$  degradation rates show slightly difference, indicating NBTI induced degradation is uniform in the channel. As  $V_{DS}$  increases, the degradation rate in the reverse mode is larger than that in the forward mode, signifying hot carriers induced damage is mainly located in the drain side.

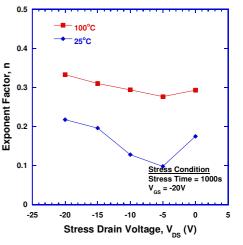

In our experiment, the  $\Delta V_{th}$  follows a power law dependence on the stress time ( $\Delta V_{th} \sim t^n$ ). The exponent factors (n) were shown in Fig. 7. At  $V_{DS} = 0$ V, the n values are about 0.2 to 0.3, which are consistent with the previous studies in NBTI [7]. As  $V_{DS}$  increases form 0V to -5V, the n values decrease due to the retarded NBTI by the application of  $V_{DS}$ . As  $V_{DS}$  increases to more negative, the degradation rate is dominated by HCS, thus the n values increase with the  $V_{DS}$ .

### 4. Conclusion

We proposed an analytic model to quantify the combined NBTI and HCS effects, and the experimental results conformed to the model. From the analysis of the experimental results and the model we proposed, the combined NBTI and HCS effects of p-channel LTPS TFTs can be identified.

# Acknowledgements

This work was support by the National Science Council, Taiwan, R. O. C., under contact NSC94-2215-E-009-064.

# References

- 1. K. Okuyama, et al., IEDM Tech. Dig., 527 (1993).

- 2. E. Li, et al., Proc. IRPS, 103 (2000).

- 3. A. T. Krishnan, et al., IEDM Tech. Dig., 39.3.1 (2001).

- 4. Y. Tour and T. H. Ning, Fundamentals of modern VLSI devices, p. 123 (1998).

- 5. E. Takeda and N. Suzuki, *IEEE Electron Device Lett.*, **4**, 111 (1983).

- 6. T. J. King, et al., J. Appl. Phys., **75**, 908 (1994).

- 7. S. Ogawa and N. Shiono, *Phys. Rev. B*, **51**, 4218 (1995).

Fig. 1 Schematic cross-section view of the LTPS TFT and the stress setup.

Fig. 2  $\Delta V_{th}$  of the LTPS TFTs after various stress conditions.

Fig. 3 Relationship between the magnitude of  $\Delta V_{th}$  and  $V_{DS}$ .

Fig. 4 Comparison of the measured data with the predicted combined NBTI and HCS effects under (a) 100°C and (b) 25°C stress.

Fig. 5 Degradation rates of subthreshold swing as a function  $V_{DS}$  with fixed  $V_{GS}$  of -20V.

Fig. 6 On current degradation rate as a function of  $V_{DS}$  with fixed  $V_{GS}$  of -20V.

Fig. 7 comparison of the exponent factor as a function of  $V_{DS}$  with fixed  $V_{GS}$  of -20V.