# Direct Evidence of GeO Volatilization from GeO<sub>2</sub> Films and Impact of Its Suppression on GeO<sub>2</sub>/Ge MIS Characteristics

Sho Suzuki<sup>†</sup>, Koji Kita, Hideyuki Nomura, Tomonori Nishimura and Akira Toriumi

Department of Materials Engineering, School of Engineering, The University of Tokyo

7-3-1 Hongo, Bunkyo-ku, Tokyo 113-8656, Japan

Phone : +81-3-5841-7161 Fax : +81-3-5841-7161 E-mail: kita@adam.t.u-tokyo.ac.jp

## **1. Introduction**

Germanium has been considered as one of the beyond-Si channel materials [1]. The key to improve the Ge device performance is to control the Ge/dielectric interface properties. However, it has been pointed out that the thermodynamical instability of Ge oxides [2] is a big issue to overcome. It should be noted that Ge-O bonds still exist at the interface, even if high-k gate dielectric is employed instead of GeO<sub>2</sub>. Thus it is critically important to develop the way to improve the GeO<sub>2</sub>/Ge interface quality in order to realize high performance Ge devices.

## 2. Experimental

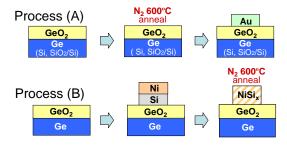

The GeO<sub>2</sub> films were deposited by rf-sputtering on three kinds of substrates; HF-treated p-Ge(100), HF-treated Si(100), and thermally-oxidized Si. The MIS capacitors were fabricated by two kinds of processes as shown in **Fig.1**. In the *process* (A), the films were annealed at 600°C in pure N<sub>2</sub> ambient, followed by Au electrode deposition. In the *process* (B), Si and Ni layer were sequentially deposited on the film before annealing at 600°C in N<sub>2</sub>. Ni-silicide electrode is formed during the annealing. The physical thickness of the films were determined with grazing incidence x-ray reflectivity (GIXR) measurements.

**Fig. 1** Schematics of fabrication processes (*A*) and (*B*) for GeO<sub>2</sub> MIS capacitors. The *process* (*A*) employed PDA in N<sub>2</sub> at 600°C. In the *process* (*B*), the annealing in the same condition was performed only after Ni and Si layer deposition. The Ni-silicide electrode is formed during the annealing in *process* (*B*).

## 3. Results and Discussions

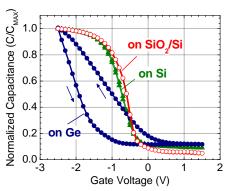

The 1MHz C-V characteristics of GeO<sub>2</sub> MIS capacitors, fabricated on Ge, Si, and thermally-oxidized Si substrates by *process* (A) are shown in **Fig.2**. Only the capacitor fabricated on Ge shows seriously deteriorated characteristics, while the capacitors on Si and that on SiO<sub>2</sub>/Si show quite good characteristics. Those results mean that the quality of GeO<sub>2</sub> film and that of the interface significantly differs according to the substrates. In order to investigate the mechanism of the observed difference, the

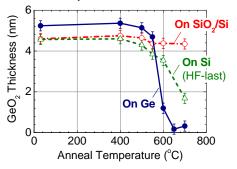

thermodynamical stability of Ge oxides on those substrates were investigated. **Fig.3** shows the change of GeO<sub>2</sub> physical thickness by annealing in N<sub>2</sub>. The thickness of the film on Ge substrate drastically decreases > 600°C, while that on SiO<sub>2</sub>/Si shows no change up to 700°C. The clear difference between those substrates clearly shows that the driving force of Ge oxide desorption is not originated from the GeO<sub>2</sub>-bulk properties but from the reaction at GeO<sub>2</sub>/Ge. interface. The reaction will probably be attributed to the generation of volatile GeO at the interface (GeO<sub>2</sub> + Ge  $\rightarrow$ 2GeO) [2,3]. Thus the interface degradation caused by GeO desorption should be responsible for the miserable C-V characteristics observed only for GeO<sub>2</sub>/Ge MIS capacitor.

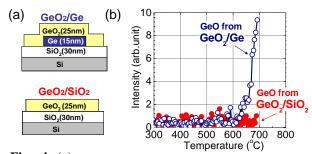

The results of thermal desorption mass spectroscopy of the  $GeO_2$  films, deposited on Ge and  $SiO_2$ , as shown in **Fig.4**, support above discussions. From the film deposited

**Fig. 2** Bidirectional C-V characteristics (1MHz) of GeO<sub>2</sub> MIS capacitors fabricated on Ge, Si, and thermally-oxidized Si substrates by *process* (A) (normalized with accumulated capacitance). The film thicknesses are ~10nm for all samples. The capacitor fabricated on Ge substrate shows the characteristics with huge hysteresis and stretch-out, while quite good characteristics are obtained from the capacitors on Si and SiO<sub>2</sub>/Si substrates.

**Fig. 3** Change of GeO<sub>2</sub> film physical thickness on various substrates by annealing in N<sub>2</sub>. The thickness of the film on Ge substrate drastically decreases by annealing at 600°C, while that on SiO<sub>2</sub>/Si shows no change up to 700°C. The clear difference among those substrates indicate that the interface reaction between GeO<sub>2</sub>/substrate is the driving force of Ge oxide desorption.

**Fig. 4** (a) Structures of  $\text{GeO}_2/\text{SiO}_2$  and  $\text{GeO}_2/\text{Ge}$  stacks examined by thermal desorption mass spectroscopy (TDS). (b) Intensity of the signals corresponding to Ge mono-oxide (GeO) detected by TDS of sputtered-GeO<sub>2</sub> film on Ge ( $\circ$ ) and that on SiO<sub>2</sub> ( $\bullet$ ). The mass numbers of 86, 88, 89, and 90 were taken into account as the signal for GeO. Above 600°C, the GeO signal was observed only from the film on Ge, which indicates the GeO desorption is driven by GeO<sub>2</sub>/Ge interface reaction.

on Ge, the GeO desorption was clearly detected  $> 600^{\circ}$ C, while no signal was observed from the film on SiO<sub>2</sub>.

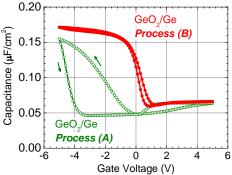

Next, we examined a new fabrication process to improve the GeO<sub>2</sub>/Ge interface quality, indicated as *process* (**B**) in **Fig.1**. In this process, annealing at 600°C was conducted after the deposition of cap layer (NiSi<sub>X</sub>), which is expected to block the GeO desorption from GeO<sub>2</sub>. The C-V characteristics of GeO<sub>2</sub>/Ge MIS capacitors with 25nm-thick GeO<sub>2</sub> layer, fabricated with *process* (**A**) and (**B**) are shown in **Fig.5**. Only a small hysteresis and a small flat-band voltage shift were observed for the sample with *process* (**B**), in contrast to miserable characteristics for the sample with *process* (**A**). The great improvement of the characteristics by applying *process* (**B**) clearly shows the important role of NiSi<sub>X</sub> cap-layer to suppress the GeO desorption. To our knowledge, this is the first demonstration of fairly good GeO<sub>2</sub>/Ge MIS characteristics with 600°C process.

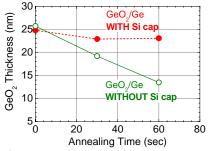

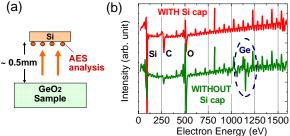

The material selection for the cap-layer will also be an important issue, since high-k films, like HfO<sub>2</sub> deposited over GeO<sub>2</sub>, cannot prevent the GeO desorption [4]. In our experiment, Si layer will have the ability to block GeO. Actually, the decrease of physical thickness of GeO<sub>2</sub> film deposited on Ge substrate by N2 annealing, can be efficiently suppressed by the Si-cap layer, as shown in Fig.6. In order to ensure the role of Si-cap layer further, Auger electron spectroscopy (AES) was employed to detect the desorbed GeO from GeO2/Ge stack. A Si-chip was set opposite to GeO<sub>2</sub>/Ge stack in the furnace during N<sub>2</sub> annealing, as shown in Fig.7 (a). Then the desorbed GeO from GeO<sub>2</sub> film would absorb on Si-chip which was analyzed with AES. As shown in Fig.7 (b), Ge was clearly detected on the Si-chip when GeO<sub>2</sub>/Ge stack was annealed without Si-cap. On the other hand, no Ge signal was observed when the sample was covered with Si-cap. From those results, it is concluded that Si-cap layer efficiently blocks the GeO desorption during annealing process, and dramatically improve the GeO<sub>2</sub>/Ge interface quality.

### 4. Conclusion

It has been clarified that  $GeO_2/Ge$  MIS characteristics are drastically improved by employing a cap-layer during

the annealing process to suppress the GeO desorption, which is driven by the interface reaction at  $GeO_2/Ge$ . These results give us a guideline for preparing high-quality dielectric/Ge interface.

#### Acknowledgements

This work was partly supported by a Grant-in-Aid for Scientific Research from the MEXT in Japan. The TDS was measured by S.Kimura and T.Nabatame, in MIRAI project, Tsukuba, Japan.

(†) S. Suzuki is currently with Canon Inc.

#### References

- [1] C.O.Chui et al., IEDM Tech. Dig. 437 (2002).

- [2] J.T. Law and P.S. Meigs, J. Electrochem. Soc. 104, 154 (1957).

- [3] K. Prabhakaran et al., Appl. Phys. Lett. 76, 2244 (2000).

- [4] K. Kita et al., ECS Trans. 3 (3) 71 (2006).

**Fig. 5** 1MHz C-V characteristics of  $\text{GeO}_2/\text{Ge}$  MIS capacitors fabricated with *process* (*A*) and (*B*). The thicknesses of both  $\text{GeO}_2$  films were ~25nm after N<sub>2</sub> annealing at 600°C for 1min. The characteristics of the sample with *process* (*B*) is greatly improved from those with *process* (*A*), in terms of hysteresis and flat-band voltage.

**Fig. 6** Change of  $GeO_2$  physical thickness by  $N_2$  annealing at 600°C, with (dotted line) and without (solid line) the Si-cap layer. The film thickness was strictly determined by GIXR measurements. The Si-cap layer efficiently suppresses the desorption of GeO.

**Fig. 7 (a)** The experimental setup to monitor the desorbed species from  $GeO_2$  film. A Si-chip was set opposite to the  $GeO_2$  sample with a 0.5mm distance in the furnace, to catch the desorbed species during the annealing at 600°C. **(b)** Auger electron spectroscopy (AES) of the surface absorbants on Si-chips, which were annealed with  $GeO_2/Ge$  samples covered WITH or WITHOUT Si-cap layer. The Ge signal was detected only when the sample was without Si-cap layer.