## A-3-1 (Invited)

## A Study of NBTI and PBTI (Charge Trapping) in High k Stacks with NiSi, TiN, Re Gates

S. Zafar, Y. H. Kim, V. Paruchuri, V. Narayanan, B. Doris, A. Callegari, J. Stathis, and T. Ning IBM Semiconductor Research & Development Center (SRDC), Research Division,

T. J. Watson Research Center, Yorktown Heights, NY 10598, Ph: 914-945 3304; Fax: 914-945 2141; email:szafar@us.ibm.com

Abstract: Threshold voltage (V<sub>t</sub>) of a field effect transistor (FET) is observed to shift with stressing time and this stress induced V<sub>t</sub> shift is an important transistor reliability issue. V<sub>t</sub> shifts that occur under negative gate bias is referred as NBTI and those that occur under positive bias is referred as PBTI or charge trapping. In this paper, we present results of experimental and modeling studies of NBTI and PBTI for a variety of FETs with different gate dielectric stacks (SiO<sub>2</sub>/HfO<sub>2</sub>, SiON) and gate materials (TiN, NiSi, Re, poly Si). In part I, NBTI measurement and modeling results for SiO<sub>2</sub>/HfO<sub>2</sub>/metal pFETs are presented. The main result is that the estimated V<sub>t</sub> shifts at 10 years due to NBTI is independent of metal gate material and is comparable to those for conventional SiON/poly-Si pFETs. In part II, PBTI measurement and modeling results for SiO<sub>2</sub>/HfO<sub>2</sub>/metal nFETs are presented. The main results are as follows. PBTI significantly increases as the Hf content in the high  $\kappa$  layer is increased. PBTI in TiN and Re gated SiO<sub>2</sub>/HfO<sub>2</sub> devices is much smaller than those observed for SiO<sub>2</sub>/HfO<sub>2</sub>/NiSi. In summary for SiO<sub>2</sub>/HfO<sub>2</sub> stacks, NBTI is observed to be independent of gate material whereas PBTI is significantly worse for FUSI gated devices. Consequently, HfO<sub>2</sub> FETs with TiN and Re gates exhibit over all superior transistor reliability characteristics in comparison to HfO<sub>2</sub>/FUSI FETs.

**Experimental Details:** NBTI and PBTI measurements were made on pFETs and nFETs, respectively; the details for measuring  $V_t$  shifts  $(\Delta V_t)$  as a function of stress time is given elsewhere [1, 2].  $\Delta V_t$  measurements were made at 125°C at various positive and negative stress voltages. In this study, all the high  $\kappa$  stacks consist of SiO<sub>2</sub> (~6Å)/HfO<sub>2</sub> (25Å) and received a high temperature (~1000°C) post deposition anneal and a forming gas anneal. TiN and Re gates were deposited by sputtering and CVD, respectively. Silicidation temperature for NiSi was 500°C.

NBTI Modeling and Experimental Study: Measured  $\Delta V_t$  versus stress time curves are analyzed by using previously proposed model for NBTI [1]. The model assumes that both interfacial and oxide hole traps are created due to depassivation of Si-H bonds at the silicon interface, and the depassivation is mediated by dispersive diffusion of protons. The equilibrium hole occupancy of traps is given by Fermi function. The model predicts a stretched exponential equation for  $V_t$  shift as a function of stressing time (t) as given below.

$$\begin{split} |\Delta V_t\left(t\right)| &= \Delta V_{max} \cdot (1 - exp - \left(t/\tau_o\right)^{\;\beta}) \qquad (1) \\ \text{where } \Delta V_{max}, \; \tau_o \; \text{and} \; \beta \; \text{are fitting parameters; } \tau_o \; \text{and} \; \Delta V_{max} \; \text{are} \\ \text{both function of stress oxide field } E_{stress}, \; \text{whereas } \beta \; \text{is} \\ \text{independent of } E_{stress}. \; \text{Equation 1 will be used for fitting } \Delta V_t \\ \text{versus stress time curves for NBTI, thus estimating } \Delta V_t \; \text{values at} \\ 10 \; \text{years lifetime.} \end{split}$$

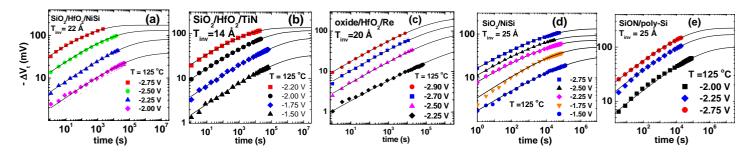

Fig. 1 (a) - (d) shows the dependence of NBTI induced  $\Delta V_t$  on stress time at various negative stress voltages for a variety

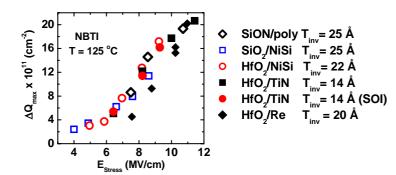

of pFETs. As shown in Fig. 1, the model fits (eq. 1) are in good agreement with data for a variety of pFETs and are used for estimating  $\Delta V_t$  at 10 years of stress time. In Fig. 2, NBTI results for NiSi, TiN and Re gated pFETs are compared with those conventional pFETs. Since T<sub>inv</sub> values are different for various pFETs,  $\Delta Q_{max}$  values are compared.  $\Delta Q_{max}$  is the charge density created after 10 years of stress:  $\Delta Q_{max} = \Delta V_t \; (10 \ yr) \, \cdot \, \epsilon_{ox} / T_{inv},$ where  $\varepsilon_{ox}$  is the permittivity of SiO<sub>2</sub> and  $\Delta V_t$  (10 yr.) is the estimated shift after 10 years of stressing and are estimated by fitting equation 1 to measured curves as shown in figures 1. In Fig. 2, NBTI induced  $\Delta Q_{max}$  for TiN and Re pFETs are observed to be comparable to those for NiSi and convention pFETs. Since all the pFETs in this study have a similar Si/oxide interface, the result of Fig. 2 indicates that NBTI depends predominantly on the Si/oxide interfacial property. In summary, NBTI shows no measurable dependence on gate material or dielectric stack provided Si/oxide interfacial quality remains same.

**PBTI Modeling and Experimental Study**: A model for charge trapping is proposed for high  $\kappa$  nFETs [2]. The trapping physics in high  $\kappa$  stacks is assumed to be same as that were proposed for SiO<sub>2</sub> with one main exception: the trapping cross section is assumed have a small distribution in its values. Like the NBTI model equation, the model equation for charge trapping is also a stretched exponential equation as shown below.

$$\Delta V_{t}(t) = \Delta V_{\text{max}} \cdot (1 - \exp - (t/\tau)^{\gamma})$$

(2)

where  $\Delta V_{max}$ ,  $\tau$  and  $\gamma$  are fitting parameters. Equation 2 will be used for fitting  $\Delta V_t$  versus stress time curves for PBTI, thus estimating  $\Delta V_t$  values at 10 years lifetime.

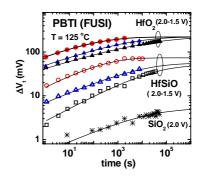

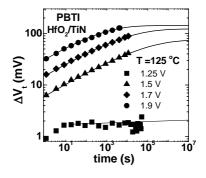

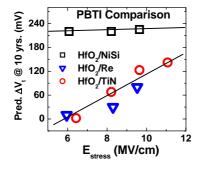

Fig. 3 shows the dependence of PBTI on stressing time and bias for SiO<sub>2</sub>/HfO<sub>2</sub>/NiSi, SiO<sub>2</sub>/HfSO/NiSi and SiO<sub>2</sub>/NiSi nFETs. From Fig. 3, we observe that the charge trapping increases as the Hf content in the high  $\kappa$  layer increases, thereby indicating that the interaction between poly-Si (before silicidation) and Hf plays an important role in creating traps in the high  $\kappa$  gate dielectric stacks. Fig. 4 shows the dependence of PBTI induced ΔV<sub>t</sub> on stress time for SiO<sub>2</sub>/HfO<sub>2</sub>/TiN nFETs. In both figures 3 and 4 symbols are measurements and solid lines are model fits obtained using equation 2. As shown in these two figures model equation gives good fits over several decades of stress time for a variety of high κ nFETs. Measurements similar to those for HfO<sub>2</sub>/TiN nFETs were also made for HfO<sub>2</sub>/Re nFETs. In Fig. 5, PBTI in HfO<sub>2</sub> stacks with TiN and Re as gates are compared with those for HfO<sub>2</sub>/NiSi nFETs. As shown in the figure, PBTI in NiSi gated nFETs is significantly worse than PBTI in TiN and Re gated devices.

**Conclusions**: Experimental and modeling study for a variety of high  $\kappa$  FETS is presented. NBTI and PBTI in FUSI (NiSi), TiN,

and Re gated HfO<sub>2</sub> devices are compared: NBTI is independent of gate material and is comparable to conventional SiON/poly-Si FETs. PBTI is worse for HfO<sub>2</sub>/NiSi nFETs in comparison to HfO<sub>2</sub>/TiN and HfO<sub>2</sub>/Re devices. Consequently, HfO<sub>2</sub> FETs with TiN and Re gates exhibit superior  $V_t$  reliability in comparison to HfO<sub>2</sub>/NiSi FETs.

## Reference:

- [1] S. Zafar, JAP (2005);

- [2] S. Zafar et al, JAP 93, 9298 (2003)

**Fig 1**: Dependence of NBTI induced V<sub>t</sub> shift for various pFETs :(**a**) SiO<sub>2</sub>/HfO<sub>2</sub>/NiSi, (**b**) SiO<sub>2</sub>/HfO<sub>2</sub>/TiN, (**c**) SiO<sub>2</sub>/HfO<sub>2</sub>/Re, (**d**) SiO<sub>2</sub>/NiSi, and (**e**) SiON (~5%N)/poly-Si; symbols are measurements and solid lines are model fits using eq. 1.

**Fig. 2**: NBTI comparison for  $SiO_2/HfO_2$  pFETs with FUSI (NiSi), TiN and Re gates;  $\Delta Q_{max}$  is charge density created after 10 yrs of stressing and is estimated from fits shown in Fig. 1 and 6. NBTI is similar for  $HfO_2$  pFETS with different gate materials (NiSi, TiN, Re) & comparable to SiON/poly pFETs.

**Fig. 3**: PBTI for NiSi gated nFETs with SiO<sub>2</sub>, SiO<sub>2</sub>/HfSiO & SiO<sub>2</sub>/HfO<sub>2</sub> as gate dielectrics; symbols are measurements and solid lines model fits using eq. 2. PBTI becomes worse with increasing Hf content in the dielectric layer.

**Fig. 4**: Charge trapping induced  $\Delta V_t$  curves for SiO<sub>2</sub>/HfO<sub>2</sub>/TiN nFETs; symbols are measurements and solid lines are fits using eq.2.

**Fig. 5**: PBTI comparison for SiO<sub>2</sub>/HfO<sub>2</sub> stacks with different gate materials; symbols are measurements. PBTI is worse in HfO<sub>2</sub>/NiSi compared